国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

4,231 - 4,240 / 6,199

半導体装置

【課題】半導体装置の高耐圧化および高速動作を実現すること。

【解決手段】炭化珪素からなる{11−20}面を主面とするn+型炭化珪素基板1と、n+型炭化珪素基板1の上に形成されたn+ソース領域6と、n+ソース領域6の表面から形成されたトレンチ8と、酸化速度が異なるトレンチ8の複数の側壁に形成されたゲート酸化膜9と、を備え、複数の側壁によって形成される複数のコーナー部のうち、複数の側壁よりも酸化速度の遅い面を有するコーナー部からトレンチ8の中心までの距離が、他のコーナー部からトレンチ8の中心までの距離よりも長くなっている。

(もっと読む)

金属内包フラーレン伝導材料及びその製造方法

【課題】金属内包フラーレンのアダマンタン修飾誘導体から液−液界面析出法により、n型及びp型の両極性のFET特性を有する金属内包フラーレンナノロッドを製造する金属内包フラーレンナノロッド及びその製造方法を実現する。

【解決手段】金属内包フラーレンアダマンタン修飾誘導体であるLa@C82アダマンタン修飾誘導体又はCe@C82アダマンタン修飾誘導体をCS2溶液に混合し容器内に入れて、このCS2溶液にヘキサンを徐々に加え、CS2層とヘキサン層が交じり合わないようにしてから、遮光下0℃で静置することによって、CS2層とヘキサン層の界面に単結晶の金属内包フラーレンアダマンタン修飾誘導体ナノロッドを製造する。

(もっと読む)

銀導電膜およびその製造法

【課題】非真空雰囲気下かつ300℃未満の低温で大面積の製膜が可能であり、薄膜型太陽電池の裏面電極側の反射膜として好適なテクスチャー構造を有し、低抵抗かつ基板との密着性に優れた導電薄膜を提供する。

【解決手段】基板上に形成された銀の薄膜であって、平均粒径DTEMが100nm以下の銀粒子が焼結した層で構成され、比抵抗が5μΩ・cm以下であり、焼結層中の空孔割合が3個/μm2以下であり、表面粗さRaが10〜100nmのテクスチャー構造を有する銀導電膜。このようなテクスチャー構造をもつ銀導電膜は、平均粒径DTEM;100nm以下の銀粒子が沸点60〜300℃の非極性または極性の小さい液状有機媒体に分散している銀粒子分散液を、基板上に塗布して塗膜を形成し、その後、前記塗膜を焼成する工程を有する製造プロセスで製造することができる。

(もっと読む)

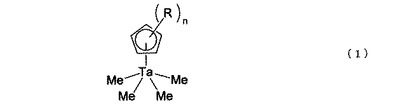

タンタル化合物とその製造方法、及びそれを原料とするタンタル含有薄膜とその形成方法

【課題】ハロゲン及び窒素を含まないタンタル含有薄膜の形成が可能な新規なタンタル化合物とその製造方法、及び膜の形成方法を提供する。

【解決手段】一般式(1)で表されるタンタル化合物を、テトラハロシクロペンタジエニルタンタル誘導体とメチル化金属化合物とを反応させることにより製造し、このタンタル化合物を原料としてタンタル含有薄膜を形成させる。

(式中、Meはメチル基を、nは1から5の整数を、Rはアルキル基を示す。)

(もっと読む)

基板処理装置

【課題】スペース効率が良好でコンパクトな基板処理装置を提供する。

【解決手段】ウエハにスパッタリングを施すスパッタリング室12と、スパッタリング室12内に収納されウエハ1を保持するウエハチャック20と、ウエハ1を保持したウエハチャック20を回転させる回転機構21と、ウエハ1に向けてイオンビーム36を照射するミリング用イオン源30とを備えており、ミリング用イオン源30のミリング用電極32を短辺側がウエハの外径より小さく長辺側が同外径より大きい矩形形状に形成し、このミリング用電極32の開口部33の開口率をウエハの中心側より周辺側が大きくなるように設定する。ミリング加工時にウエハを回転させつつイオンビームをウエハに照射すると、ミリング加工量をウエハ全面で均一化できる。ミリング用イオン源のサイズを小さくできるので、スペース効率を向上させてスパッタリング装置を小型化できる。

(もっと読む)

バリア膜製造方法、及びバリア膜

【要 約】

【課題】低抵抗の窒化物薄膜を低い成膜温度で形成する。

【解決手段】真空雰囲気中に高融点金属を有する原料ガスと窒素原子を有する含窒素還元ガスを導入し、高融点金属の窒化物薄膜24を形成する際、窒素を有しない補助還元ガスを導入する。補助還元ガスによって析出した高融点金属が、析出した窒化物の高融点金属の不足分を補償し、化学量論組成比に近く、低比抵抗の窒化物薄膜24を成長させることができる。

(もっと読む)

半導体素子

【課題】電極または金属配線と所望の絶縁膜とを密着でき、所望の低リーク電流特性および高耐圧特性を得ることができること。

【解決手段】この発明にかかるHEMT100は、基板1の上部に形成された化合物半導体層の電子供給層5の上部に、ソース電極6とゲート電極7とドレイン電極8と絶縁膜9,10とを有する。ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10との各接合界面には窒化物系の接合膜11a,11d,11cが形成され、ゲート電極7と絶縁膜9との接合界面には窒化物系の接合膜11bが形成される。接合膜11a,11d,11cは、ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10とをそれぞれ接合する。接合膜11bは、ゲート電極7と絶縁膜9とを接合する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CMISFETを有する半導体装置の性能を向上させるとともに、製造工程数を低減する。

【解決手段】CMISFETを有する半導体装置を製造方法する際に、まず、シリコン膜と第1金属からなる第1金属膜を熱処理により反応させることで、金属シリサイドからなるpチャネル型MISFETのゲート電極31bとnチャネル型MISFETのダミーゲート電極32を形成する。それから、ゲート電極31bを覆いかつダミーゲート電極32を露出する絶縁膜33を形成してから、第1金属の仕事関数よりも低い仕事関数を有する第2金属からなる金属膜35を形成する。金属膜35はダミーゲート電極32に接するが、ゲート電極31bとは、間に絶縁膜33が介在して接しない。その後、熱処理によりダミーゲート電極32と金属膜35とを反応させてnチャネル型MISFETのゲート電極を形成する。

(もっと読む)

SiC基板の製造方法及びSiC基板並びに半導体装置

【課題】SiC基板の製造方法及びSiC基板並びに半導体装置において、マイクロパイプだけでなく基底面内転位及び積層欠陥も低減すること。

【解決手段】マイクロパイプを有するSiC単結晶基板1上に、SiCエピタキシャル成長層2を化学的気相成長させるSiC基板の製造方法であって、SiCエピタキシャル成長層2の成長工程が、積層に伴ってマイクロパイプが閉塞される第1のエピタキシャル成長層2aを成長する閉塞層成長工程と、第1のエピタキシャル成長層2aの途中に不純物濃度が3×1019cm−3以上の第2のエピタキシャル成長層2bを少なくとも一層成長する歪み層成長工程と、を有している。

(もっと読む)

半導体装置

【課題】より簡単に素子間分離膜の端部におけるリーク電流の発生を抑制すること。

【解決手段】NMOSとPMOSとを電気的に分離するフィールド酸化膜を、LOCOS法を用いてSOI基板の活性層にシリコン酸化膜を成膜することにより形成する。フィールド酸化膜の端部には、酸化膜が薄くなるバーズビーク部が形成され、このバーズビーク部において寄生トランジスタが構成される。そのため、寄生トランジスタの作用で生じるリーク電流を抑制するためのチャネルカット領域を設ける。詳しくは、NMOSに、フィールド酸化膜のバーズビーク部であり、且つ、N+拡散層(ソース)におけるPウェル拡散層との2ヵ所の境界部にP+拡散領域を形成する。このようなチャネルカット領域を設けることにより、ゲートオフ時における寄生トランジスタにおける寄生チャネルによる電流パス(リーク電流)を抑制することができる。

(もっと読む)

4,231 - 4,240 / 6,199

[ Back to top ]