国際特許分類[H01L23/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832)

国際特許分類[H01L23/00]の下位に属する分類

容器,封止 (4,129)

マウント,例.分離できない絶縁基板 (9,861)

容器の充填または補助部材,例.センタリング部材 (134)

封緘,例.封緘層,被覆 (7,021)

動作中の完全装置を支持する支持体,すなわち分離できる定着物 (458)

冷却,加熱,換気または温度補償用装置 (8,151)

動作中の固体本体からまたは固体本体へ電流を導く装置,例.リードまたは端子装置 (2,507)

動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

半導体装置に適用される標識,例.登録標識,テストパターン

放射,例.光,からの保護

他に分類されない半導体装置用構造的電気的装置 (109)

国際特許分類[H01L23/00]に分類される特許

181 - 190 / 648

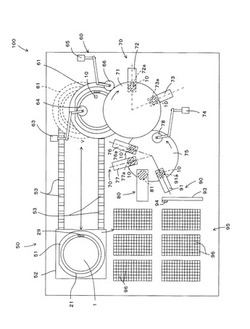

半導体装置の製造装置および半導体装置の製造方法

【課題】レーザを照射して半導体ウエハにマーキングを施すことにより、半導体ウエハに大きな反りが生じ、半導体装置の製造が困難となる。

【解決手段】半導体基板11が研削されて薄型化された半導体チップ10は、半導体基板11の裏面がダイシングテープ21に接着され、ロード部50からチャック部64に搬送される。半導体チップ10は、順次、ピックアップされてマーキング前検査部70にてマーキング基板面の検査がなされた後、マーキング部80で半導体基板11の裏面にレーザによりマークが形成される。このように、半導体チップ10は個々に分離された状態でマーキングが施されるので、半導体基板11に反りが発生しない。

(もっと読む)

素子、実装装置および方法

【課題】素子の認識マーク設置面の反対面から、認識マークの位置を認識し、高精度での位置決めができる素子、実装装置及び方法を提供する。

【解決手段】表面および裏面の位置決め基準となる素子表面位置決めマークおよび素子裏面位置決めマークを備える素子であって、前記素子表面位置決めマークが、複数設けられた前記素子を透過しない観察光を透過させる所定形状のマークであり、前記素子裏面位置決めマークが、前記複数の素子表面位置決めマークの一方の端面にそれぞれ設けられた、前記観察光を透過しない所定形状のマークである。

(もっと読む)

回路素子

【課題】回路素子の向きを簡単な構成で認識しやすくすることにより、実装ミスの低減を図る回路素子を提供する。

【解決手段】複数の接続パッド31a及び31bの一部である接続パッド31aと基板32との間に設けられた成膜層33は、基板32側の配線33b上に保護膜33c側の配線33aが直接重ねられ、複数の接続パッド31a及び31bの残りと基板32との間に設けられた成膜層33は、2層の配線33a、33b間に絶縁層33eが設けられている。そして、これにより接続パッド31aと基板32との間に設けられた成膜層33の膜厚d1と、複数の接続パッド31bと基板32との間に設けられた成膜層33の膜厚d2と、を互いに異ならせて、互いに色が異なるように視認させる。

(もっと読む)

電子部品モジュールの製造方法及び電子部品モジュール

【課題】確実に電子部品をシールドすることができるとともに、低背化を伴う小型化を実現することができる電子部品モジュールの製造方法及び該製造方法を用いて製造した電子部品モジュールを提供する。

【解決手段】第1工程は、集合基板10を封止樹脂にて封止する。第2工程は、電子部品モジュール1の境界部分にて、封止樹脂の天面から、集合基板10に向かって切り込み部17を形成する。第3工程は、切り込み部17の開口部及び天面を覆うようにシート状の導電性樹脂18を載置する。第4工程は、所定の温度範囲で軟化し、加圧に対して導電性樹脂18よりも変形量の大きいシート状の絶縁性樹脂19を、導電性樹脂18上に載置する。第5工程は、圧力及び熱を加えることにより、集合基板10の少なくとも側面の一部及び天面を導電性樹脂18及び絶縁性樹脂19で被覆する。第6工程は、それぞれの電子部品モジュール1に個片化する。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のモジュールを高密度実装した統合モジュールを小型化できる技術を提供する。

【解決手段】集積チップ部品68が搭載された上層のモジュール基板66と、半導体チップIC1、単体チップ部品54および集積チップ部品55が搭載された下層のモジュール基板51とを、導電性の複数の接続部材65を介して電気的かつ機械的に接続し、これらをモールド樹脂56で一括封止した状況下において、モジュール基板51、66の側面およびモールド樹脂56の表面(上面および側面)にCuめっき膜およびNiめっき膜との積層膜からなるシールド層SLを形成して、電磁波シールド構造を実現する。

(もっと読む)

半導体装置およびその電力供給方法

【課題】基板上に集積回路(半導体素子)を実装してなる半導体装置において、集積回路における発熱の抑制を行うと共に、静電気放電によるノイズから内部回路を保護する。

【解決手段】複数の出力セル101を有する液晶ドライバにおいて、出力セル101の構成要素であるオペアンプ105は、半導体素子である液晶ドライバ内に形成された電源配線109aに接続されている。また、半導体素子を実装する基板上にバイパス配線201が形成され、バイパス配線201は、電源配線109aに対して、全ての出力セルのオペアンプ105毎にバンプ203を介して接続される。さらに、バイパス配線201は、第1の部分201aと第2の部分201bとによって半導体素子の電源配線109上のESD保護素子205を挟んで配置される。

(もっと読む)

電子部品装置及びその製造方法

【課題】

低コストで作製可能な電子部品装置及びその製造方法を提供する。

【解決手段】

開口部によって開口される空洞部を有する容器と、前記容器の壁部を貫通して前記容器の内外にわたって配設されるリードフレームと、電磁シールド構造を有し、前記容器の前記開口部に蓋をする蓋部とを有し、前記空洞部内に電子部品が配設される電子部品装置であって、前記空洞部内で前記電子部品と前記リードフレームの所定電位のフレームとを接続するワイヤの長さは、前記ワイヤと前記電子部品との第1接続部から前記容器の前記開口部までの第1の距離と、前記ワイヤと前記所定電位のフレームとの第2接続部から前記容器の前記開口部までの第2距離との合計距離以上に設定され、前記ワイヤは、前記第1接続部及び前記第2接続部の間で前記蓋部に接触される。

(もっと読む)

電子部品用パッケージ、電子部品装置、及び電子部品用パッケージの製造方法

【課題】

低コストで作製可能な電子部品用パッケージ、電子部品装置、及び電子部品用パッケージの製造方法を提供する。

【解決手段】

開口部によって開口される空洞部を有する容器と、前記容器の壁部を貫通して前記容器の内外にわたって配設されるリードフレームと、電磁シールド構造を有し、前記容器の前記開口部に蓋をする蓋部とを有し、前記空洞部内に電子部品が配設される電子部品用パッケージであって、前記壁部の前記空洞部側の内壁に沿って、前記リードフレームのうちの所定電位のラインと前記開口部との間に形成される溝部と、前記溝部内で前記蓋部と前記所定電位のラインとを接続する導電部とを含む。

(もっと読む)

電子デバイスの製造方法

【課題】配線部をスパッタリングにより形成するスパッタ配線工程において、基板の外周部を、スパッタ装置内のヒーターとクランプリングとにより挟み込み、基板を保持することによる、基板の欠けの発生を抑制する。

【解決手段】緩衝層形成工程において、基板1の表面1Aに緩衝層3を形成するとともに、緩衝層3の材料と同じ材料を用いて、緩衝層形成工程の保護層形成工程を実施し、半導体装置10の製造方法を複雑化させることなく、基板1の表面1Aの外周部1B、および裏面1Dの外周部1Eに保護層4を形成するので、緩衝層形成工程の後に実施するスパッタ配線工程において、基板1の表面1Aおよび裏面1Dを直接挟み込むことなく、保護層4を介在させて挟み込み、基板1を保持することができ、基板1、特に基板1の外周部1B、および外周部1Eに欠けが発生することを抑制して、スパッタ膜11を形成することができる。

(もっと読む)

埋め込まれた基板及びリードフレームを備えたモジュールパッケージ

基板と、リードフレームと、基板とリードフレームとの間に配置される1つ又はそれ以上の集積回路とを含む集積回路パッケージを説明する。基板の片側又は両側に複数の電気的構成要素を取り付けることができる。集積回路の能動面は、基板に電気的及び物理的に接続される。集積回路の背面は、リードフレームのダイ取り付けパッド上に搭載される。リードフレームは複数のリードを含み、複数のリードは、基板に物理的に取り付けられ電気的に結合される。基板とリードフレームと集積回路の一部分を成形材料が封止する。またこのようなパッケージの形成方法も説明する。

(もっと読む)

(もっと読む)

181 - 190 / 648

[ Back to top ]