国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

111 - 119 / 119

フェーズロックドループ回路

入力基準信号Urefと入力信号Up,inとの間の位相差ΔΦを検出するための位相比較器であって、Kpが前記位相比較器の位相検出器ゲインである位相比較器と、入力信号Uvco,inに応じて角周波数ωvco,outを有する周期的な出力信号Uvco,outを生成するための電圧制御発振器(VCO)であって、Kvcoが前記電圧制御発振器の電圧制御発振器ゲインである電圧制御発振器(VCO)と、フェーズロックドループ回路の動作中にループゲインK:=Kp×Kvcoが所定の範囲内のままとなるようにフェーズロックドループ回路の動作中に前記位相検出器ゲインKpを制御するようになっているコントローラと、を備えるフェーズロックドループ回路(PLL回路)。  (もっと読む)

(もっと読む)

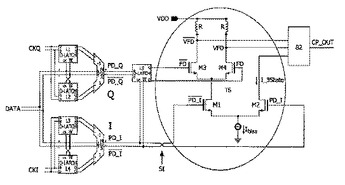

高速の位相周波数検出装置

本発明は、ランダムデータ用のタイミング情報を回復する回復回路用の検出装置およびチャージポンプ回路に関する。検出装置は、基準信号の直交成分を、入力信号に基づいてサンプリングし、第1のバイナリ信号を生成するための、第1のラッチ手段と、基準信号の同相成分を、入力信号に基づいてサンプリングし、第2のバイナリ信号を生成するための、第2のラッチ手段と、第1のバイナリ信号を、第2のバイナリ信号に基づいてサンプリングし、周波数誤差信号を生成するための、第3のラッチ手段と、を備える。よって、簡潔で速い検出回路が、デジタル実施に基づいて達成される。さらに、チャージポンプ回路は、差動入力回路と、差動入力回路のテール電流を、周波数検出装置の周波数ロック状態に応じて制御するための制御手段とを備える。これは、チャージポンプ回路の挙動が、検出装置によって生成される余分なリップルを低減できる、という利点を提供する。  (もっと読む)

(もっと読む)

クロック信号生成装置、半導体集積回路およびデータ再生方法

本発明は、位相誤差検出範囲を広くした位相誤差検出器と、PLL同期状態に基づいたゲイン制御により、PLLの引込時間の改善を図る。位相誤差が増加している場合に位相誤差検出点の補正を行うことにより位相誤差検出範囲を広くする。また、位相誤差値を平滑化した値の標準偏差に基づいてPLLのロック状態を判定し、引込過渡状態と定常状態とでゲインを切り替えることにより、PLLの引込時間を短縮かつ安定させることが可能となる。 (もっと読む)

利得を自動的に設定する位相ロックループ

【解決手段】利得を自動的に設定する位相ロックループPLLが提供される。PLLは、第1の周波数と第2の周波数の差を表す第1の信号を供給する周波数弁別器を備える。またPLLは、周波数弁別器に結合され、第1の信号を受信し、第1の信号からの情報に基づいて第2の信号を供給する比較器を備えている。第2の信号は設定する位相ロックループに対する利得設定を表す。 (もっと読む)

バイナリ変調によるチャネルのタイミング回復

書込み(書換え)可能な光ディスクシステム及び読取り専用の光ディスクシステムのために、位相ロックループ(PLL)によってデータクロックが回復される。前記位相ロックループ(PLL)においては、実際の零交差と生成されるクロック信号の零交差を比較することによって誤差信号が生成される。レーザ波長λlaser及び開口数NAを持つ光学系と仮定すると、変調伝達関数のカットオフ波長は、λ0=λlaser/(2・NA)によって与えられる。ビット長の減少に伴って、最小波長の振幅は、縮小し、λ0未満の波長の場合は零になる。結果として、これらの信号の零交差によって生成される位相誤差信号は、雑音によって乱される。本発明の着想は、クロック回復のための位相情報の導出において十分なパフォーマンスを持つ零交差しか用いないことにある。

(もっと読む)

(もっと読む)

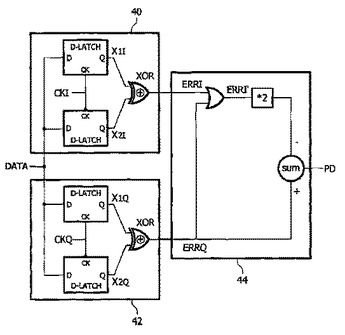

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

遅延ロックループのための起動回路

遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。  (もっと読む)

(もっと読む)

位相周波数検出器およびそれが組み込まれた位相ロックループ回路

【課題】 位相誤差信号に周波数差を加味した変形を加えることにより、周波数が離れているときでも短時間で位相同期を達成する。

【解決手段】 周波数が離れているときに生じる位相誤差信号の不連続なジャンプをジャンプ検出部30において検出し、検出信号により状態記憶部32の状態を遷移させる。保持部34において、状態記憶部32の状態に応じて位相誤差信号を修正して周波数位相誤差信号とする。

(もっと読む)

PLL回路

【課題】位相差が零に近づくまでの時間が短くて済み、ループ動作の高速化が図られたPLL回路を提供する。

【解決手段】位相/周波数検出回路16で参照信号SREF と比較信号Sv との位相差が−π/2と+π/2とに挟まれた第1の領域内にあるか、あるいはその第1の領域から外れた第2の領域内にあるかを検出し、参照信号SREF と比較信号Sv との位相差が第2の領域内(±π/2以外)にある場合に、位相反転回路17で位相が反転した比較信号Sv を出力する。

(もっと読む)

111 - 119 / 119

[ Back to top ]