国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

11 - 20 / 119

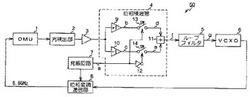

ルビジウム原子発振器

【課題】回路構成を単純化して部品コストを低減すると共に、回路の小型化を実現したルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器50は、ルビジウム原子の共振周波数により励振する光マイクロ波ユニット(OMU)1と、OMU1を透過した光の強度を検出する光検出部2と、Amp3に現れる周波数誤差信号の位相を検波する位相検波器4と、位相検波器4の出力信号を積分するループフィルタ5と、ループフィルタ5の電圧に基づいて所定の周波数を発振する電圧制御水晶発振器(VCXO)6と、マイクロ波の位相を低周波により変調する発振回路7と、VCXO6の発振信号をマイクロ波に逓倍する位相変調逓倍部8と、を備えて構成されている。

(もっと読む)

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

位相比較器

【課題】位相比較器において、2つのフリップ・フロップの出力信号がリセットされるまでの遅延時間によって両出力信号に現れる余分な成分を取り除き、それによって生じる種々の問題を解決すること。

【解決手段】本発明の位相比較器は、比較対象の2つの入力信号が入力されて第1と第2の出力信号を出力する第1と第2のフリップ・フロップと、第1と第2の出力信号を論理積処理してリセット信号を出力する論理積処理回路と、論理積処理回路と同じ遅延時間を持ち第1遅延信号と第2遅延信号を出力する第1と第2の遅延手段と、第1遅延信号と第2遅延信号がそれぞれ入力されるとともにリセット信号によってリセットされて第3と第4の出力信号を出力する第3と第4のフリップ・フロップとを備え、位相が進んだ方の入力信号を遅延させた第1もしくは第2遅延信号が入力される第3もしくは第4のフリップ・フロップの出力信号に位相比較出力信号が出力さるように構成されている。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

送受信装置及び同期システム

【課題】2つの送受信装置の間の同期確立と距離を測定する

【解決手段】他の第2送受信装置に対して第1信号を送信し、第2送受信装置において受信した第1信号を折り返して第2信号として返信して、フェズドロックループ(PLL)により同期をとる送受信装置である。基準信号を出力する基準発振器と、送信ベースバンド信号を発生する、位相と周波数が可変の信号発振器と、送信ベースバンド信号により搬送波を変調して得られる第1信号を送信する送信器を有する。第2送受信装置から受信した第2信号を復調して受信ベースバンド信号を得る受信器と、送信ベースバンド信号と基準発振器の出力する基準信号との第1位相差を検出する第1位相比較器と、受信ベースバンド信号と基準発振器の出力する基準信号との第2位相差を検出する第2位相比較器と、第1位相差と第2位相差との絶対値の差を出力する比較器とを有する。比較器の出力が零となるように、信号発振器の位相と周波数をフィードバック制御した。

(もっと読む)

デジタル位相比較器およびこれを備えたデジタルPLL回路

【課題】デジタル位相比較器におけるスタートアップ時のキャリブレーションを不要とする。

【解決手段】基準信号を遅延させて遅延基準信号として出力し、遅延量に相当する時間差を有する遅延量信号を出力する手段と、遅延基準信号と発振器出力信号との時間差をデジタル値に変換し第1のデジタル値として出力する手段と、第1の時間量子化器で発生した時間残差を検出し、時間残差に応じた時間差を有する時間残差信号を出力する手段と、基準信号の状態に応じて時間残差信号を出力するか遅延量信号を出力するかを切り替える手段と、時間残差信号の時間差をデジタル値に変換して第2のデジタル値として出力し、遅延量信号の時間差をデジタル値に変換して第3のデジタル値として出力する手段と、第2のデジタル値および前記第3のデジタル値を用いて第1のデジタル値を補正することで小数位相を算出する手段と、を有する。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

半導体装置

【課題】クロック周波数の設定を変えた場合でも電源や温度などに変動があっても、高精度なクロック信号を生成する。

【解決手段】周波数電圧変換回路13は、スイッチSW1,SW2から構成されるスイッチ部、静電容量素子C,C10〜C13、およびスイッチCSW0〜CSW3から構成されている。静電容量素子C10〜C13は、容量の絶対値が異なるもので構成され、設計者が意図する周波数範囲をカバーするよう設ける。静電容量値は、たとえば、2の重み付けがされている静電容量素子C11〜C13は、たとえば、4ビットの周波数調整制御信号SELC0〜SELC3に基づいて、スイッチCSW0〜CSW3が選択し、周波数の切り替えを行う。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

11 - 20 / 119

[ Back to top ]