国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

31 - 40 / 119

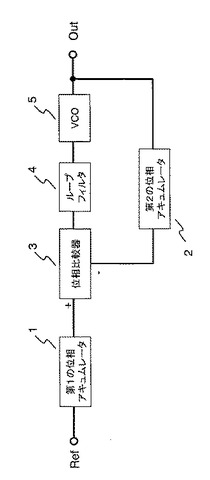

PLL回路

【課題】位相比較周波数を高く保ち、PLLの位相雑音を改善し、出力信号の精度を向上させたPLL回路を提供する。

【解決手段】基準信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した基準信号の位相に相当する信号を出力する第1位相アキュムレータ1、発振器の出力信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した発振器の出力信号の位相に相当する信号を出力する第2位相アキュムレータ2、第1及び第2位相アキュムレータの出力信号を比較して差を求め基準信号と発振器の出力信号との位相差を示す出力信号を出力する位相比較器3、位相比較器の出力信号に従って発振器への制御信号を生成する制御部4、制御部からの制御信号に応じた周波数の信号を出力する上記発振器5を有す。

(もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

遅延ロックループのための初期化回路

【課題】遅延ロックループのための起動回路を提供する。

【解決手段】遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出し、そのアンロックの検出でアラーム検出するようにした周波数シンセサイザである。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

31 - 40 / 119

[ Back to top ]