国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

71 - 80 / 119

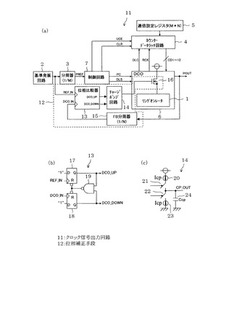

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

DLL回路

【課題】DLL回路を備えたLSIの電磁放射強度を低減し、電磁放射ノイズの電子機器への影響を低減する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、前記第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、 前記同期基準信号と前記同期対象信号との位相差を比較する位相比較回路105と、前記位相比較回路105の比較結果に基づいて前記第1遅延部102の出力信号を選択する第1制御回路106と、前記同期基準信号又は前記同期対象信号を遅延する第2遅延部104と、前記位相比較回路105の比較結果が所定の範囲内である場合に、前記第2遅延部104の出力信号を選択する第2制御回路107と、を備え、前記位相比較回路105は、前記同期基準信号と前記同期対象信号のうち前記第2遅延部104によって遅延された信号と他方の信号との位相差を比較する。

(もっと読む)

ルビジウム原子発振器

【課題】回路構成を単純化して部品コストを低減すると共に、回路の小型化を実現したル

ビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器50は、ルビジウム原子の共振周波数により励振

する光マイクロ波ユニット(OMU)1と、OMU1を透過した光の強度を検出する光検

出部2と、Amp3に現れる周波数誤差信号の位相を検波する位相検波器4と、位相検波

器4の出力信号を積分するループフィルタ5と、ループフィルタ5の電圧に基づいて所定

の周波数を発振する電圧制御水晶発振器(VCXO)6と、マイクロ波の位相を低周波に

より変調する発振回路7と、VCXO6の発振信号をマイクロ波に逓倍する位相変調逓倍

部8と、を備えて構成されている。

(もっと読む)

発振回路、PLL回路、半導体チップ、および、試験装置

【課題】発振回路における位相雑音成分を低減する。

【解決手段】発振信号を生成する発振回路であって、与えられる制御電圧に応じた周波数の発振信号を出力する電圧制御発振器と、電圧制御発振器が出力する発振信号の位相の変動成分を抽出し、位相の変動成分に応じて制御電圧を調整するジッタ復調器とを備える発振回路を提供する。発振回路は、電圧制御発振器に入力される制御電圧の、予め定められたカットオフ周波数より大きい周波数成分を除去して、電圧制御発振器に供給するローパスフィルタを更に備えてよい。

(もっと読む)

データ再生装置

【課題】再生信号の分解能が著しく低下した場合にも、安定して精度よくクロックを生成し、高速かつ安定したデータPLLを用いたデータ再生装置を提供する。

【解決手段】データ再生装置において、ピックアップ102の出力信号を所定のクロックでアナログ/デジタル変換するA/D変換器104と、A/D変換器104の出力信号を所望の特性に等化する波形等化回路105と、波形等化回路105の出力信号を最尤復号する最尤復号回路106と、クロックの位相誤差を検出する位相誤差検出回路107と、等化誤差を検出する等化誤差検出回路110と、位相誤差検出回路107の出力信号および等化誤差検出回路110の出力信号を加算する加算器111と、加算器111の出力信号により制御されてクロックを生成する電圧制御発振器114とを備えた。

(もっと読む)

タイムトゥデジタルコンバータ

【課題】タイムトゥデジタルコンバータを提供する。

【解決手段】タイムトゥデジタルコンバータは、高い解像度と広い測定範囲のために低解像度タイムトゥデジタルコンバータと高解像度タイムトゥデジタルコンバータとを含む。低解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔で測定する。高解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔よい更に小さい第2量子化間隔で測定する。低解像度タイムトゥデジタルコンバータは、高解像度タイムトゥデジタルコンバータより広い測定範囲を有する。

(もっと読む)

装置、位相ロック・ループ・システム及び位相ロック・ループを動作させるための方法

【課題】フィード・フォワード位相周波数検出器を備えた、高速且つ低ジッタの位相ロック・ループ(PLL)を提供する。

【解決手段】

位相周波数検出器に含まれる位相差センサは、基準信号の立ち上がりエッジとフィードバック信号の立ち上がりエッジとの間の位相差期間を指示する出力信号を供給する。また、この装置に含まれる進み−遅れセンサは、基準信号がフィードバック信号より進んでいる場合を指示する出力信号を供給する。さらに、ステアリング論理が、位相差センサ及び進み−遅れセンサの出力に結合される。このステアリング論理は、基準信号がフィードバック信号より進んでいる場合は、位相差期間信号を第1出力に導き、基準信号がフィードバック信号より遅れている場合は、位相差期間信号を第2出力に導く。

(もっと読む)

位相誤差検出回路、位相同期ループ回路および情報再生装置

【課題】 位相誤差検出回路において、読み出し信号の振幅レベルが変動しても位相誤差を精度良く検出し、よって位相同期ループ回路の位相同期特性を安定させること。

【解決手段】 位相誤差検出回路7は、入力信号の連続する2つのサンプリング位置n,(n−1)における信号レベルXn、Xn−1について、それらの和Anと差Bnの比Cn(=An/2/Bn)を演算する演算器を備える。そして、信号レベルXn、Xn−1の極性が変化するサンプリング位置における演算結果Cnを位相誤差信号Tnとして出力する。さらに、演算したAnの値を、入力信号のDC誤差信号Snとして出力する。

(もっと読む)

クロックリカバリ回路

【課題】

過剰な位相雑音が検出されたとしても、同期外れを起しにくいクロックリカバリ回路を提供する。

【解決手段】

位相比較回路と、フィルタと、電圧制御型発振回路とを有するPLL回路を有するクロックリカバリ回路において、入力されるデータ信号に含まれるパターンを用いて、データ信号と前記電圧制御型発振回路から出力されるクロック信号との±πを超える位相差を検出し、その位相差に応じた信号を発生させる信号発生回路と、その信号を前記位相比較回路からの出力信号に加算する回路とを備える。

(もっと読む)

クロックデータ復元装置

【課題】トランスミッタ・クロック・ジッタや符号間干渉が大きい場合であっても安定してクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、サンプラ部10、検出部20、オフセット決定部30、クロック出力部40およびDA変換部50を備える。クロック信号CK,CKXの位相は、入力デジタル信号の位相と一致するよう調整される。サンプラ部10におけるオフセット付与量(±Voff)は、値D(n-1)がハイレベルである場合の第1信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整され、値D(n-1)がローレベルである場合の第2信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整される。復元されたクロック信号として、クロック信号CK,CKXの何れかが出力される。復元されたデータとして、デジタル値D(n)の時系列データが出力される。

(もっと読む)

71 - 80 / 119

[ Back to top ]