国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

81 - 90 / 119

到達ロックループ技術を用いたスペクトラム拡散クロック生成器

ランダム周波数変調および正確な可変周波数拡散を備えるスペクトラム拡散クロック信号到達ロックループ技術を用いた新しい技術が示される。到達ロックループは、正確な拡散制御を有する到達比較器、ループフィルタ、およびVCOの3つのモジュールを含む。到達ロックループは不安定にされ、一定の周波数で発振し、VCOからの高周波出力信号を周波数において拡散するため、最終誤差補正出力上に低周波変調信号を生成する。到達比較器の入力において周波数拡散の周期を小量にリセットするために定時信号に対してサイクルスリップが生成されるように拡散周波数が長くなるまで低周波変調信号のそれぞれのサイクルにおける拡散周波数の周期も、微小ランダム量だけ何サイクルも増加する。  (もっと読む)

(もっと読む)

半導体集積回路

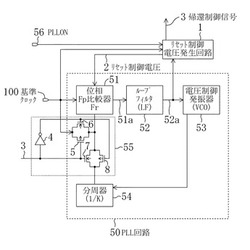

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】スイッチオーバーから発生する出力信号における不所望の位相変化を信頼性を持って回避することが可能なフェーズロックループ。

【解決手段】制御可能オシレータDCOが出力信号CKoutを発生し、PLL12入力クロックとして使用するために第一クロック/第二クロックCKin2、CKin1を切り換えることが可能である。使用中のCKin1又はCKin2と、CKoutのプリセットされ、位相シフトされたCK<1:8>間の位相差を決定し、DCOを制御するために使用され、使用されていないCKin2又はCKin1がCKoutを発生するために、位相が調節される。入力クロックの幾つかのCKin1,CKin2,CKin3間の位相差がスイッチオーバーの前に調節されることで、スイッチオーバーから発生するPLL出力信号における不所望の位相変化を高い精度で回避し且つヒットレススイッチングを達成する。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

PLL回路

【課題】差動入力型VCO回路の利点である同相ノイズに強く、さらに入力電圧範囲がシングル入力より広いPLL回路を提供する。

【解決手段】差動入力型VCO回路とループフィルタ回路と位相検出回路とを備え、半導体集積回路に設けられるPLL回路であって、差動入力型VCO回路に位相検出した信号を供給する位相検出回路と、位相検出回路の出力と差動入力型VCO回路の一方の差動入力を接続し、位相検出回路の出力とグランド間に設けたループフィルタ回路と、差動入力型VCO回路の他方の差動入力に位相検出回路と略同じバイアス電圧を供給するダミー出力用バイアス回路と、を具備する半導体集積回路に設けられるPLL回路である。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】位相比較器のフリップフロップ間の誤差に起因するスプリアスを抑圧することができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】位相比較器33から出力された位相比較信号Dnu(t)を第1の利得値αnuで電圧増幅するとともに、その位相比較器33から出力された位相比較信号Dnd(t)を第1の利得値αnuと異なる第2の利得値αndで電圧増幅し、電圧増幅後の位相比較信号Dnu(t)と電圧増幅後の第2の位相比較信号Dnd(t)との差分信号を出力する減算回路33を設ける。

(もっと読む)

クロック変換回路

【課題】クロック変換時の収束時間を短縮し安定性を向上する。

【解決手段】位相比較部10は基準クロックをカウントした基準クロックカウンタ値と、供給された再生クロックステップ値を加算して再生クロックのタイミングでラッチした再生クロックステップ値加算結果との位相比較を行い、位相誤差を検出する。ループフィルタ11は検出された位相誤差を平滑化し位相誤差に対応した電圧値を出力する。電圧制御発振部12はループフィルタ11により出力された電圧値により再生クロックを生成する。

(もっと読む)

デジタルPLL回路及びそれを備えた光ディスク装置

【課題】動作周波数が低く、安価にIC化を行うことができ、設計が容易なデジタル回路を用いて時間分解能の高いクロック信号を生成することができるDPLL回路を備えた光ディスク装置を提供する。

【解決手段】デジタルPLL回路部は、エッジ検出回路部と、クロックデータ生成回路部と、位相差検出回路部とを備え、一周期毎に、デジタルクロックデータから、デジタルクロック信号の立ち上がりエッジ又は立ち下がりエッジの有無を時間分解能単位で示した書き込みタイミング信号を生成して出力する。

(もっと読む)

半導体装置

【課題】PLL回路のロックタイムを短縮しつつ、ロック時のチャージポンプのリーク電流を削減して安定した出力信号を供給する半導体装置を提供する。

【解決手段】一の電源電圧と接続され、半導体基板上に位相同期ループ回路1を配設する半導体装置において、位相同期ループ回路には、複数の回路ブロック2、3、5、6が備わり、半導体基板上には、一の電源電圧から電圧値の異なる電圧を生成して、回路ブロックごとにそれぞれ電圧値の異なる電圧を供給する複数の電源電圧供給手段7、8、9と、かかる電源電圧供給手段から生成された電圧の何れか一つを回路ブロックのうちの少なくとも一つの回路ブロックに含まれるPMOSトランジスタ基板に選択的に供給することにより電圧の供給先となる回路ブロックの出力を制御する供給電圧制御手段10と、を備えることを特徴とする。

(もっと読む)

クロック再生装置、データ受信装置

【課題】 原クロックの周波数に対して再生クロックの周波数が定常的に大きいあるいは小さいという状況が継続しないようにしたクロック再生装置を提供する。

【解決手段】 クロック再生装置は、送信装置から受信中のデータから原クロック情報を取得する信号検出器101と、再生クロックを出力するVCXO111と、信号検出器101にて取得した原クロック情報の中から、同期合わせに用いる同期合わせ用クロック情報として原クロック情報を選択する信号選択器102とを備える。VCXO111は、原クロック情報から求められる同期合わせ用クロック情報の間隔と、再生クロックにより計測される同期合わせ用クロック情報の取得時間の間隔との差を、同期合わせ用クロック情報の間隔で除した値に基づいて制御される。信号選択器102は、再生クロックが原クロックに近づくに従って、同期合わせ用クロック情報を選択する頻度を低くする。

(もっと読む)

81 - 90 / 119

[ Back to top ]