国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

51 - 60 / 119

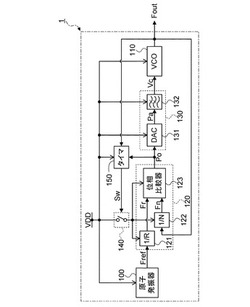

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

高分解能の時間/デジタル変換器

【解決手段】時間/デジタル変換器(TDC)は、インバータの伝播遅延よりも優れた分解能を有し得る。一例では、非整数遅延素子回路は、TDC入力信号を受信し、そこから、第1信号の時間シフトした複製である第2信号を生成する。第1信号は、第1遅延線タイムスタンプ回路(DLTC)に供給され、第2信号は第2DLTCに供給される。第1DLTCは、TDCへの参照入力信号のエッジと第1信号のエッジとの間の時間を示す第1タイムスタンプを生成する。第2DLTCは、参照入力信号のエッジと第2信号のエッジとの間の時間を示す第2タイムスタンプを生成する。第1及び第2タイムスタンプは合成されて、共に高い分解能の全体のTDCタイムスタンプを構成する。これは、第1または第2タイムスタンプよりも優れた分解能を有する。 (もっと読む)

位相同期回路および位相同期方法ならびにデコーダ装置

【課題】PCRジッタが比較的大きいストリームを受信した場合でも、SDI信号のジッタ特性の悪化およびPCR−PLL制御の追従性の悪化を防止することが可能な位相同期回路の提供。

【解決手段】本発明に係る位相同期回路は、所定の時間間隔で入力信号と出力信号の位相差を算出し、その位相差に応じた電圧を出力する比較部8と、比較部8からの電圧が入力されその電圧に応じた周波数の出力信号を出力する電圧制御発振器5と、電圧制御発振器5への電圧の入力を、比較部8に所定の時間間隔内で段階的に行わせる制御タイミング発生部7とを含んでいる。

(もっと読む)

シンセサイザと、これを用いた受信装置、および電子機器

【課題】精度の高い発振周波数を生み出す事ができるシンセサイザを提供する事を目的とする。

【解決手段】シンセサイザ1は、基準発振器2からの基準発振信号が入力される比較器4と、比較器4の出力信号に基づいて発振信号を出力する電圧制御発振器5と、この電圧制御発振器5の出力信号を制御部7からの制御信号に基づいて分周する第2分周器6とを備えており、比較器4は、第2分周器6からの出力信号と基準発振器2からの出力信号とを比較してこの比較結果を示す信号を電圧制御発振器5に出力し、シンセサイザ1を用いる電子機器の使用状態に基づいて、第2分周器6の分周比の値が決められている。これにより、温度検出部8とMEMS振動子11との間の温度差に起因したシンセサイザの発振周波数誤差を無くす事ができる。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】デジタルオーディオ回路で使用する第1クロック信号CLKAとDC−DCコンバータで使用する第2クロック信号CLKBとの周波数差によって生ずる可聴周波数帯域のノイズ信号を除去することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】発振周波数制御回路23は、第1クロック信号CLKAの第1周波数FAと第2クロック信号CLKBの第2周波数FBとの差が可聴周波数帯域に入ると、第2発振回路21に対して、該帯域に留まらないように第2周波数FBを変化させるようにし、第2周波数FBが可聴周波数帯域に入った場合は、第2発振回路21に対して、第2周波数FBを上昇させて最大可聴周波数以下にならないようにした。

(もっと読む)

位相比較器及び測定装置

【課題】2つの信号の位相比較結果を確実に保持できる位相比較器を提供する。

【解決手段】2つの信号CMP、REFの位相を比較して、その位相関係を出力する比較部10と、比較部より出力される位相比較結果を入力信号として受信し信号OUTとして出力するホールド回路30と、比較部の出力に基づいて位相比較結果が確定したか否かを判定し、位相比較結果が確定したと判定した場合にホールド信号Cを出力するホールド信号生成部20とを備え、ホールド回路は、ホールド信号が出力されている期間は前記入力信号を保持するようにして、比較部による位相比較結果が確定する前に状態が保持されることを防止し、位相比較結果を確実に保持できるようにする。

(もっと読む)

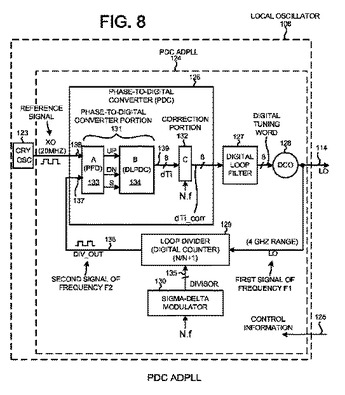

自己訂正する位相デジタル伝達関数を有する位相ロックループ

位相ロックループは、位相デジタル変換器部分、ならびに新規訂正部分を含む。位相デジタル変換器(PDC)部分は、第1の位相誤差ワードのストリームを出力する。新規訂正部分は、第1の位相誤差ワードを受け取り、そしてループフィルタへと供給される第2の位相誤差ワードのストリームを生成する。PDC部分は、ある種の不完全性を示す位相デジタル伝達関数を有する。第1の例においては、訂正部分は、第1の位相誤差ワードの対の間の平均差を決定し、そして遅延要素伝搬遅延の変化に起因したPDC部分の伝達関数の傾斜における変化について訂正するために第1の位相誤差ワードを正規化するためにこの平均差を使用する。第2の例においては、訂正部分は、PDC部分の伝達関数における利得ミスマッチについて訂正する。第3の例においては、訂正部分は、PDC部分の伝達関数におけるオフセットミスマッチについて訂正する。  (もっと読む)

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

DLL回路,撮像装置,メモリ装置

【課題】DLL回路における正常ロック状態の安定性を向上させる。

【解決手段】可変遅延回路10は、入力クロックCKinを順次遅延させ、それぞれ位相が異なる遅延クロックCK(1),・・・CK(k)を生成する。位相比較回路11は、遅延クロックCK(n−m),CK(n+m)の立ち上がりエッジ間の期間を有効期間として規定し、その有効期間中においてのみ遅延クロックCK(1),CK(n)のそれぞれの電圧レベルに基づいて位相比較する。遅延制御回路12は、位相比較回路11による比較結果に基づいて、可変遅延回路10における遅延時間を制御する。

(もっと読む)

51 - 60 / 119

[ Back to top ]