国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

21 - 30 / 119

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

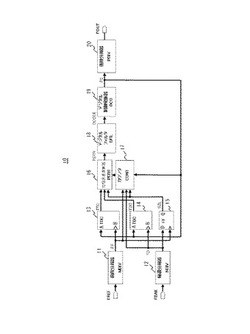

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

位相検出回路およびPLL回路

【課題】2つのクロック信号の位相比較に基づき生成する2つのパルス信号の遅延時間を極力短くすることができ、かつ確実にリセットできる位相検出回路および該位相検出回路を備えたPLL回路を提供すること。

【解決手段】位相検出回路は、位相比較を行う2つのクロック信号の論理和信号と論理積信号とに基づき、進相側と遅相側の2つのパルス信号の生成に用いる一方の出力を、前記位相比較を行う準備動作状態と、前記位相比較を行った回路動作状態とに切り替えて保持するラッチ回路を備えている。

(もっと読む)

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

PLL回路および通信装置

【課題】出力周波数を切り替えた際の追従性の悪化を抑止すること。

【解決手段】分周部2は、基準信号と出力信号との位相を同期させるための信号である帰還信号を所定の分周比に分周する。そして、位相比較部3は、出力信号を用いて基準信号および帰還信号の位相を比較することで、分周部2が分周した分周比の増減に追従して、出力信号を生成するための位相比較部出力のゲインが増減する。濾波部4は、位相比較部3によって生成されたアナログ信号を濾波する。出力信号発振部5は、濾波部4によって濾波されたアナログ信号に基づいて、出力信号を生成する。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

21 - 30 / 119

[ Back to top ]