国際特許分類[H03L7/085]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896)

国際特許分類[H03L7/085]の下位に属する分類

ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

アップダウンパルスを出力する位相または周波数検出器 (20)

サンプリング装置を用いる位相または周波数検出器 (49)

ループ中で特別なろ波または増幅特性を用いるもの (404)

ロック検出器を用いるもの (172)

2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/085]に分類される特許

41 - 50 / 119

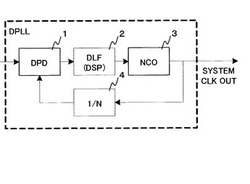

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

周波数誤差推定装置

【課題】雑音の影響によらず高精度な周波数誤差を推定できる周波数誤差装置を提供する。

【解決手段】周波数誤差推定装置は、周波数誤差検出範囲が可変である周波数誤差検出回路と、周波数誤差検出回路の検出値を入力とし、平滑化処理し、周波数誤差推定値として出力する第1の平滑化フィルタ回路と、周波数誤差検出回路の周波数誤差検出範囲又は第1の平滑化フィルタ回路のフィルタ帯域幅を調整する調整回路とを備え、調整回路は、周波数誤差検出範囲に含まれる有効領域を設定し、周波数誤差検出値が有効領域を超えたとき、有効領域の中心周波数を周波数誤差検出値に再設定し、有効領域の再設定が所定の時間内に起きない場合、周波数誤差検出範囲又は第1の平滑化フィルタ回路のフィルタ帯域幅を狭める。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

PLL回路およびそれを用いた角速度センサ

【課題】本発明は、正確に位相を調整することが可能なPLL回路およびそれを用いた角速度センサを提供することを目的とするものである。

【解決手段】本発明のPLL回路およびそれを用いた角速度センサは、AD変換器21が電圧制御発振器26の出力するタイミング信号により動作し、かつDA変換器24が分周器27の出力するタイミング信号でのAD変換器21の出力する値に応じたアナログ信号を出力する構成としたものである。

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

位相検出装置、位相検出方法、再生装置及び再生方法

【課題】

記録媒体から再生される再生信号とクロック信号との位相差を正確に検出することが可能な位相検出装置、位相検出方法、該位相検出装置を備えた再生装置、再生方法を提供する。

【解決手段】

位相同期回路39がリミット位相ディテクタ41を備えるので、例えば図4に示すゼロクロスのタイミング(C)が検出されたとき(ST605でYES)、クロックカウンタ47によるカウント値と所定の値とを比較し(ST606)、カウント値が所定の値より小さいときに(ST606でNO)Cから次のクロックの立ち上がりまでの間、位相カウンタ51をイネブルでない状態とすることができる。つまり、リミット位相ディテクタ41(の位相カウンタ51)の出力を無効にすることができる。この結果、例えばノイズ等の影響を受け易い所定カウント値より小さいパルス幅のRF信号(入力信号)に基づき位相エラー信号が求められることを防止することができる。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】各種大振幅雑音、伝送路ロスの増大、雑音レベルの増大が発生するような大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】このPLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づいて基準信号の位相及び/又は発振周波数を制御するVCXOと、抽出されたタイミング位相ベクトル信号の位相又は位相差に基づいて基準信号の位相及び/又は発振周波数を制御するための制御係数を出力する2次PLL回路102とを備えている。この2次PLL回路102は、抽出されたタイミング位相ベクトル信号について対数軸上で位相検出を行うとともに、対数軸上で制御係数を発生する制御係数発生回路111を有している。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】PLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づき基準信号の位相及び/又は発振周波数を制御するVCXOと、タイミング位相ベクトル信号の位相及び位相差に基づき制御係数を出力する2次PLL回路とを備える。この2次PLL回路は、タイミング位相ベクトル信号に基づき制御係数を発生する制御係数発生回路と、制御計数発生回路からの制御係数につき6dB単位での対数軸上におけるレベル調整を行う第1のレベル調整回路と、第1のレベル調整回路からの制御係数について±6dBレベルの微調整を行う第2のレベル調整回路とを有する。

(もっと読む)

41 - 50 / 119

[ Back to top ]