半導体装置とその製造方法

【課題】半導体チップの積層数が多くなっても、フィレットの水平方向の拡がりを大きくすることなく最上段の半導体チップの端面までアンダーフィル材を供給でき、半導体装置の大型化、配線基板の汚染、アンダーフィル材の上段の半導体チップ間への充填不良等を防止することができる半導体装置とその製造方法を提供する。

【解決手段】実施形態の半導体装置10は、配線基板2と、配線基板2上にフリップチップ接続により多段に積層された複数の半導体素子1a〜1eと、配線基板2の外周部に立設され、半導体素子1a〜1eを囲繞する側壁5と、積層された複数の半導体素子1a〜1eと側壁5との間隙、及び配線基板2と半導体素子1a〜1eの各間隙に充填されたアンダーフィル材6とを具備する。

【解決手段】実施形態の半導体装置10は、配線基板2と、配線基板2上にフリップチップ接続により多段に積層された複数の半導体素子1a〜1eと、配線基板2の外周部に立設され、半導体素子1a〜1eを囲繞する側壁5と、積層された複数の半導体素子1a〜1eと側壁5との間隙、及び配線基板2と半導体素子1a〜1eの各間隙に充填されたアンダーフィル材6とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

積層型半導体装置として、配線基板上に複数の半導体チップを縦方向に多段に積層することによって、集積密度や動作速度等の向上を図ったものが知られている。このような半導体装置においては、積層された各半導体チップ間、配線基板と半導体チップ間の間隙にアンダーフィル材(液状硬化性樹脂)を充填して固定する。アンダーフィル材の充填は、積層した半導体チップの側面に供給したアンダーフィル材が毛細管現象によってチップ間の隙間に浸透していくのを利用して行われる。すなわち、アンダーフィル材は半導体チップの側面に供給されると、頂部が最上段の半導体チップの端面に達するフィレットを形成する。そして、このフィレットを形成したアンダーフィル材が半導体チップ間あるいは半導体チップと配線基板の間の10μm程度という微小な隙間に毛細管現象で浸透することによって充填される。

【0003】

ところが、この場合、積層する半導体チップの数が多くなり高さが高くなると、アンダーフィル材も高い位置まで供給しなければならず、必然的にアンダーフィル材のフィレットの水平方向の拡がりも大きくなり、場合によって、配線基板の端面に流れ出るおそれがある。この結果、半導体装置の大型化、配線基板の汚染、アンダーフィル材の上段の半導体チップ間への充填が困難になる等の問題を生ずる。さらに、複数のチップ搭載エリアを有する基板を用いて半導体装置の多数個取りを行う場合、隣り合う半導体装置のアンダーフィル材のフィレットが接続するのを避けるため、取り数を多くできないという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−278334号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、半導体チップの積層数が多くなっても、フィレットの水平方向の拡がりを大きくすることなく最上段の半導体チップの端面までアンダーフィル材を供給でき、半導体装置の大型化、配線基板の汚染、アンダーフィル材の上段の半導体チップ間への充填不良等を防止することができる半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、配線基板と、前記配線基板上にフリップチップ接続により多段に積層された複数の半導体素子と、前記配線基板の外周部に立設され、前記半導体素子を囲繞する側壁と、積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙に充填されたアンダーフィル材とを具備する。

【図面の簡単な説明】

【0007】

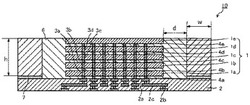

【図1】一実施形態による半導体装置の構造を示す断面図である。

【図2】図1に示す半導体装置の製造方法の一例を示す断面図である。

【図3】図1に示す半導体装置の製造方法の他の例を説明する図で、(a)は断面図、(b)は平面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して、実施形態を説明する。

【0009】

図1は、一実施形態による半導体装置の構造を示す断面図である。

【0010】

図1に示す半導体装置(半導体パッケージ)10は、いわゆる積層型半導体装置であり、複数の半導体素子(半導体チップ)1a〜1eが配線基板2上に多段に積層されている。なお、この実施形態では、半導体素子(半導体チップ)の積層数が5、つまり5段積層されている場合を中心に説明するが、半導体素子(半導体チップ)の積層数は特に限定されるものではなく、例えば、2層、8層、16層、32層等であってもよい。

【0011】

複数の半導体素子1a〜1eは、いずれもシリコン基板等の半導体基板からなる。そのうちの1つ、最上段に配置される半導体素子1eは、貫通電極を有さず、その一方の面に電極パッド(図示せず)が形成されたものである。一方、残りの半導体素子1a〜1dは、貫通電極3a〜3dを有するもので、その両面には、それぞれ各貫通電極3a〜3dに一体に設けられた電極パッド(図示せず)が設けられている。

【0012】

そして、最下段(1段目)の半導体素子1aは配線基板2上に、2段目の半導体素子1bは1段目半導体素子1a上に、3段目の半導体素子1cは2段目半導体素子1b上に、4段目の半導体素子1dは3段目半導体素子1c上に、最上段(5段目)の半導体素子1eは4段目半導体素子1d上に、それぞれフリップチップ接続されている。すなわち、配線基板2上面側に形成された接続パッド2aとそれに対向する1段目半導体素子1aの電極パッド、1段目半導体素子1aの2段目半導体素子1b側の電極パッドとそれに対向する2段目半導体素子1bの電極パッド、2段目半導体素子1bの3段目半導体素子1c側の電極パッドとそれに対向する3段目半導体素子1cの電極パッド、3段目半導体素子1cの4段目半導体素子1d側の電極パッドとそれに対向する4段目半導体素子1dの電極パッド、4段目半導体素子1dの5段目半導体素子1e側の電極パッドとそれに対向する5段目半導体素子1eの電極パッドが、それぞれ半田バンプ等の金属バンプ4a〜4eで接続されている。

【0013】

このように複数の半導体素子1a〜1eの積層体1が実装される配線基板2には、例えば樹脂基板、セラミックス基板、ガラス基板等の絶縁基板を基材として用いた多層配線基板が使用される。樹脂基板を適用した配線基板2としては、一般的な多層銅張積層板(多層プリント配線板)等が挙げられる。配線基板2の下面側には、外部と接続するための電極パッド2bが設けられている。電極パッド2b上には、図示は省略したが、半田ボール等の外部接続端子が固定される。外部接続端子は、電極パッド2bと、配線基板2の内部配線2cと、上述した接続パッド2a及び金属パッド3aを介して、半導体素子1aと電気的に接続される。

【0014】

配線基板2上の外周部には、複数の半導体素子1a〜1eの積層体1を取り囲むように側壁5が設けられており、また、この側壁5と積層体1の間隙、配線基板2と積層体1の間隙、つまり1段目半導体素子1aとの間隙、及び複数の半導体素子1a〜1eの各間隙には、アンダーフィル材6が充填されている。側壁5を備えることで、アンダーフィル材6を水平方向に拡げることなく配線基板2と各半導体素子1a〜1dの各間隙に充填することができる。

【0015】

このように、側壁5は、アンダーフィル材6の水平方向の拡がりを防止する機能を有するものである。したがって、側壁5は、アンダーフィル材6を充填したときに変形しない材料、例えば、金属、樹脂、セラミック等の材料で、配線基板2上に液密に形成されている。一般には、金属、樹脂、セラミック等からなる薄板(シート)の中央部分に、半導体素子1a〜1eの積層体1の収容できるだけの大きさの孔、厚さ方向に貫通する孔を設けたものを、配線基板2上に接着することによって形成される。図1において、7は、そのような薄板を配線基板2に接着するための接着剤層を示している。接着剤には耐熱性に優れたものを用いることが好ましい。

【0016】

側壁5は、加工の容易さの点からは金属材料で構成することが好ましい。金属材料の中でも、銅等の熱伝導性の高い材料を用いれば、半導体素子1a〜1eの熱を外部に放出する放熱材としての機能を併せ持たせることができる。また、42アロイで構成し、その表面に銀メッキを施した場合には、42アロイの線膨張率がシリコンと近似していることから、半導体素子1a〜1eを構成する半導体基板としてシリコン(Si)基板を用いた場合には好ましい。

【0017】

なお、側壁5は、樹脂層を被覆した金属シートあるいは金属層を被覆した樹脂シート等の複合材料を用いて形成することも可能である。このように側壁5を樹脂を含む複合材料、あるいは樹脂材料で形成した場合には、後述するように、大サイズの基板を用いて半導体装置を多数個取りする際の、ダイシング作業を容易なものとすることができる。

【0018】

半導体装置10の小型化、薄型化のためには、側壁5の高さhは、半導体素子1a〜1eの積層体1の高さと略同じ、つまり、側壁5の上面と積層体1の上面が略同一平面となる高さとすることが好ましい。すなわち、側壁5の高さhが積層体1の高さより低い場合には、最上段の半導体素子1eとその下段の半導体素子1dの間の間隙にアンダーフィル材6を充填するのに必要な高さまでアンダーフィル材を供給するために、側壁5と積層体1との離間距離dを大きくする必要がある。また、側壁5の高さhが積層体1の高さより高いと半導体装置10は厚くなる。具体的には、側壁5の高さhは、例えば、図1に示すような半導体素子の積層数が5、つまり5段積層の場合、積層する半導体素子1a〜1eの厚さや、配線基板2と各半導体素子1a〜1eの各間隙の大きさにもよるが、通常、0.25mm以上0.5mm以下である。また、積層数が8、つまり8段積層の場合、通常、0.4mm以上0.8 mm以下、積層数が16、つまり16段積層の場合、通常、0.8mm以上1.5mm以下である。

【0019】

また、側壁5の幅Wは、構成する材料にもよるが、通常、0.5mm以上2.0mm以下、好ましくは0.5mm以上1.0mm以下である。0.7mm程度がより好ましい。側壁5の幅Wが0.5mm未満では、配線基板2上への配置が困難になるおそれがある。また、側壁5の幅Wが2.0mmを超えると、半導体装置10が大型化するおそれがある。

【0020】

さらに、側壁5と積層体1との離間距離dは、0.2mm以上2.0mm以下の範囲が好ましく、0.3mm以上1.0mm以下の範囲がより好ましい。側壁5と積層体1との離間距離dが0.2mm未満では、側壁5と積層体1との間隙へのアンダーフィル材6の供給が困難になる。また、側壁5と積層体1との離間距離dが2.0mmを超えると、半導体装置10が大型化する。

【0021】

側壁5と積層体1の間隙、配線基板2と積層体1の間隙、及び複数の半導体素子1a〜1eの各間隙に充填されるアンダーフィル材6としては、例えばエポキシ系樹脂、アクリル系樹脂、アミン系樹脂、シリコーン系樹脂、ポリイミド系樹脂等が用いられる。アンダーフィル材6に用いる樹脂は、配線基板2と各半導体素子1a〜1eの各間隙が狭いため、流動の良い低粘度である材料を選択することが好ましい。具体的には、エポキシ系樹脂等が好ましい。

【0022】

次に、この実施形態による半導体装置10の製造工程について、図2を用いて説明する。

【0023】

まず、図2(a)に示すように、配線基板2を用意し、その上面の接続パッド2aが形成されている半導体素子搭載エリアに、複数の半導体素子1a〜1dを順にフリップチップ接続する。すなわち、まず、1段目半導体素子1a表面の電極パッド上に半田ボール等を搭載して金属バンプ4aを形成し、配線基板2上面側に形成された接続パッド2aと接合させる。次に、2段目半導体素子1b表面の電極パッド上に半田ボール等を搭載して金属バンプ4bを形成し、1段目半導体素子1a裏面の電極パッドと接合する。次に、3段目半導体素子1c表面の電極パッド上に半田ボール等を搭載して金属バンプ4cを形成し、2段目半導体素子1b裏面の電極パッドと接合する。次に、4段目半導体素子1d表面の電極パッド上に半田ボール等を搭載して金属バンプ4dを形成し、3段目半導体素子1c裏面の電極パッドと接合する。さらに、5段目半導体素子1e表面の電極パッド上に半田ボール等を搭載して金属バンプ4eを形成し、4段目半導体素子1a裏面の電極パッドと接合する。なお、複数の半導体素子1a〜1dを、別工程で予めフリップチップ接続しておき、その積層体1を配線基板2上にフリップチップ接続するようにしてもよい。

【0024】

このようにして、配線基板2上への複数の半導体素子1a〜1eの積層体1の実装が完了したら、図2(b)に示すように、例えば、中央部分に、半導体素子1a〜1eの積層体1の収容できるだけの大きさの孔、厚さ方向に貫通する孔を設けた金属薄板(シート)を、接着剤層7を介して接着し、側壁5を形成する。

【0025】

次に、図2(c)に示すように、側壁5と複数の半導体素子1a〜1eの積層体1との間隙に上方より、アンダーフィル材供給用ノズルを挿入または近接させて、アンダーフィル材6を供給し、側壁5と半導体素子1a〜1eの積層体1の側面との間隙、配線基板2と積層された前記半導体素子1a〜1eの各間隙に充填させる。充填が完了したところで、アンダーフィル材6を硬化させる。これにより図1に示す半導体装置10が作製される。

【0026】

なお、大サイズの基板を用いて半導体装置10を多数個取りする場合には、例えば、図3に示すような、配線基板2となる配線部2Aを有する基板32が用いられる。この基板32の上面には、それぞれに配線部2Aを含むように格子状に区画壁34が形成されている。この区画壁34は、その幅方向中央にダイシング領域(ダイシングライン)Lを備えており、このダイシングラインLに沿って切断することで、最終的に側壁5を形成するものである。したがって、区画壁34は、側壁5を構成する材料によって形成されている。すなわち、この区画壁34は、一般には、金属、樹脂、セラミック等からなる、基板32に対応する形状、大きさの薄板(シート)に、それぞれに半導体素子1a〜1eの積層体1を収容できるだけの大きさの孔、厚さ方向に貫通する孔を多数設けたものを、基板32上に接着することによって形成される。区画壁34の基板32上の接着には、耐熱性の良好な接着剤が使用される。

【0027】

そして、薄板(シート)に設けられた孔のそれぞれにおいて、配線部2A上の半導体素子搭載エリアに、図2の場合と同様にして、複数の半導体素子1a〜1eをフリップチップ接続により多段に積層し、さらに、この積層された複数の半導体素子1a〜1eからなる積層体1と区画壁34との間隙にアンダーフィル材6を供給して、積層体1と区画壁34との間隙、基板32(配線部2A)と半導体素子1a〜1eの各間隙にアンダーフィル材6を充填し、硬化させる。

【0028】

その後、基板32の下面をダイシングテープ等(図示せず)に固定した後、ダイシングラインLに沿って、ダイヤモンドブレード等のブレードを用いて、区画壁34及び基板32を切断する。これにより、図1に示すような、配線基板2と、配線基板2上にフリップチップ接続により多段に積層された複数の半導体素子1a〜1eと、配線基板2の外周部に設けられた側壁5と、積層された複数の半導体素子1a〜1eと側壁5との間隙、配線基板2と半導体素子1a〜1eの各間隙に充填されたアンダーフィル材6とを備えた半導体装置10が多数個取りされる。

【0029】

前述したように、側壁5材料として、樹脂層を被覆した金属シートあるいは金属層を被覆した樹脂シート等の樹脂を含む複合材料、あるいは全体が樹脂からなる材料を用いた場合には、上記ダイシングラインLに沿って行う区画壁34の切断作業が容易となる。

【0030】

以上説明した実施形態によれば、配線基板上の外周部に形成した側壁によって、アンダーフィル材の水平方向の拡がりを抑制できるので、半導体素子の積層数が多くなっても、最上段の半導体素子の端面まで少ない使用量でアンダーフィル材を供給し、各半導体素子間の間隙に充填することができる。しかも、側壁は薄く、かつ所要の高さに形成できるので、半導体装置がそのために大型化したり厚肉化したりすることもない。また、アンダーフィル材が配線基板の端面に流れ出るおそれがないので、配線基板は流れた出たアンダーフィル材によって汚染されることもない。

【0031】

さらに、半導体装置を多数個取りする場合、隣接する半導体装置のアンダーフィル材同士が接触するおそれがないため、半導体装置間のピッチを狭くすることができ、その取り数を多くすることができる。さらに、側壁が半導体装置の補強材としても機能するため、アンダーフィル材で固定した半導体素子をさらに樹脂等によって封止しなくてもよく、材料コスト及び製造コストを低減することができる。

【0032】

以上、本発明の実施形態を説明したが、この実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。この新規な実施形態は、その他の様々な形態で実施し得るものであり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。この実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0033】

1…積層体、1a〜1e…半導体素子(半導体チップ)、2…配線基板、3a〜3d…貫通電極、4a〜4e…金属バンプ、5…側壁、6…アンダーフィル材。

【技術分野】

【0001】

本発明の実施形態は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

積層型半導体装置として、配線基板上に複数の半導体チップを縦方向に多段に積層することによって、集積密度や動作速度等の向上を図ったものが知られている。このような半導体装置においては、積層された各半導体チップ間、配線基板と半導体チップ間の間隙にアンダーフィル材(液状硬化性樹脂)を充填して固定する。アンダーフィル材の充填は、積層した半導体チップの側面に供給したアンダーフィル材が毛細管現象によってチップ間の隙間に浸透していくのを利用して行われる。すなわち、アンダーフィル材は半導体チップの側面に供給されると、頂部が最上段の半導体チップの端面に達するフィレットを形成する。そして、このフィレットを形成したアンダーフィル材が半導体チップ間あるいは半導体チップと配線基板の間の10μm程度という微小な隙間に毛細管現象で浸透することによって充填される。

【0003】

ところが、この場合、積層する半導体チップの数が多くなり高さが高くなると、アンダーフィル材も高い位置まで供給しなければならず、必然的にアンダーフィル材のフィレットの水平方向の拡がりも大きくなり、場合によって、配線基板の端面に流れ出るおそれがある。この結果、半導体装置の大型化、配線基板の汚染、アンダーフィル材の上段の半導体チップ間への充填が困難になる等の問題を生ずる。さらに、複数のチップ搭載エリアを有する基板を用いて半導体装置の多数個取りを行う場合、隣り合う半導体装置のアンダーフィル材のフィレットが接続するのを避けるため、取り数を多くできないという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−278334号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、半導体チップの積層数が多くなっても、フィレットの水平方向の拡がりを大きくすることなく最上段の半導体チップの端面までアンダーフィル材を供給でき、半導体装置の大型化、配線基板の汚染、アンダーフィル材の上段の半導体チップ間への充填不良等を防止することができる半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、配線基板と、前記配線基板上にフリップチップ接続により多段に積層された複数の半導体素子と、前記配線基板の外周部に立設され、前記半導体素子を囲繞する側壁と、積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙に充填されたアンダーフィル材とを具備する。

【図面の簡単な説明】

【0007】

【図1】一実施形態による半導体装置の構造を示す断面図である。

【図2】図1に示す半導体装置の製造方法の一例を示す断面図である。

【図3】図1に示す半導体装置の製造方法の他の例を説明する図で、(a)は断面図、(b)は平面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して、実施形態を説明する。

【0009】

図1は、一実施形態による半導体装置の構造を示す断面図である。

【0010】

図1に示す半導体装置(半導体パッケージ)10は、いわゆる積層型半導体装置であり、複数の半導体素子(半導体チップ)1a〜1eが配線基板2上に多段に積層されている。なお、この実施形態では、半導体素子(半導体チップ)の積層数が5、つまり5段積層されている場合を中心に説明するが、半導体素子(半導体チップ)の積層数は特に限定されるものではなく、例えば、2層、8層、16層、32層等であってもよい。

【0011】

複数の半導体素子1a〜1eは、いずれもシリコン基板等の半導体基板からなる。そのうちの1つ、最上段に配置される半導体素子1eは、貫通電極を有さず、その一方の面に電極パッド(図示せず)が形成されたものである。一方、残りの半導体素子1a〜1dは、貫通電極3a〜3dを有するもので、その両面には、それぞれ各貫通電極3a〜3dに一体に設けられた電極パッド(図示せず)が設けられている。

【0012】

そして、最下段(1段目)の半導体素子1aは配線基板2上に、2段目の半導体素子1bは1段目半導体素子1a上に、3段目の半導体素子1cは2段目半導体素子1b上に、4段目の半導体素子1dは3段目半導体素子1c上に、最上段(5段目)の半導体素子1eは4段目半導体素子1d上に、それぞれフリップチップ接続されている。すなわち、配線基板2上面側に形成された接続パッド2aとそれに対向する1段目半導体素子1aの電極パッド、1段目半導体素子1aの2段目半導体素子1b側の電極パッドとそれに対向する2段目半導体素子1bの電極パッド、2段目半導体素子1bの3段目半導体素子1c側の電極パッドとそれに対向する3段目半導体素子1cの電極パッド、3段目半導体素子1cの4段目半導体素子1d側の電極パッドとそれに対向する4段目半導体素子1dの電極パッド、4段目半導体素子1dの5段目半導体素子1e側の電極パッドとそれに対向する5段目半導体素子1eの電極パッドが、それぞれ半田バンプ等の金属バンプ4a〜4eで接続されている。

【0013】

このように複数の半導体素子1a〜1eの積層体1が実装される配線基板2には、例えば樹脂基板、セラミックス基板、ガラス基板等の絶縁基板を基材として用いた多層配線基板が使用される。樹脂基板を適用した配線基板2としては、一般的な多層銅張積層板(多層プリント配線板)等が挙げられる。配線基板2の下面側には、外部と接続するための電極パッド2bが設けられている。電極パッド2b上には、図示は省略したが、半田ボール等の外部接続端子が固定される。外部接続端子は、電極パッド2bと、配線基板2の内部配線2cと、上述した接続パッド2a及び金属パッド3aを介して、半導体素子1aと電気的に接続される。

【0014】

配線基板2上の外周部には、複数の半導体素子1a〜1eの積層体1を取り囲むように側壁5が設けられており、また、この側壁5と積層体1の間隙、配線基板2と積層体1の間隙、つまり1段目半導体素子1aとの間隙、及び複数の半導体素子1a〜1eの各間隙には、アンダーフィル材6が充填されている。側壁5を備えることで、アンダーフィル材6を水平方向に拡げることなく配線基板2と各半導体素子1a〜1dの各間隙に充填することができる。

【0015】

このように、側壁5は、アンダーフィル材6の水平方向の拡がりを防止する機能を有するものである。したがって、側壁5は、アンダーフィル材6を充填したときに変形しない材料、例えば、金属、樹脂、セラミック等の材料で、配線基板2上に液密に形成されている。一般には、金属、樹脂、セラミック等からなる薄板(シート)の中央部分に、半導体素子1a〜1eの積層体1の収容できるだけの大きさの孔、厚さ方向に貫通する孔を設けたものを、配線基板2上に接着することによって形成される。図1において、7は、そのような薄板を配線基板2に接着するための接着剤層を示している。接着剤には耐熱性に優れたものを用いることが好ましい。

【0016】

側壁5は、加工の容易さの点からは金属材料で構成することが好ましい。金属材料の中でも、銅等の熱伝導性の高い材料を用いれば、半導体素子1a〜1eの熱を外部に放出する放熱材としての機能を併せ持たせることができる。また、42アロイで構成し、その表面に銀メッキを施した場合には、42アロイの線膨張率がシリコンと近似していることから、半導体素子1a〜1eを構成する半導体基板としてシリコン(Si)基板を用いた場合には好ましい。

【0017】

なお、側壁5は、樹脂層を被覆した金属シートあるいは金属層を被覆した樹脂シート等の複合材料を用いて形成することも可能である。このように側壁5を樹脂を含む複合材料、あるいは樹脂材料で形成した場合には、後述するように、大サイズの基板を用いて半導体装置を多数個取りする際の、ダイシング作業を容易なものとすることができる。

【0018】

半導体装置10の小型化、薄型化のためには、側壁5の高さhは、半導体素子1a〜1eの積層体1の高さと略同じ、つまり、側壁5の上面と積層体1の上面が略同一平面となる高さとすることが好ましい。すなわち、側壁5の高さhが積層体1の高さより低い場合には、最上段の半導体素子1eとその下段の半導体素子1dの間の間隙にアンダーフィル材6を充填するのに必要な高さまでアンダーフィル材を供給するために、側壁5と積層体1との離間距離dを大きくする必要がある。また、側壁5の高さhが積層体1の高さより高いと半導体装置10は厚くなる。具体的には、側壁5の高さhは、例えば、図1に示すような半導体素子の積層数が5、つまり5段積層の場合、積層する半導体素子1a〜1eの厚さや、配線基板2と各半導体素子1a〜1eの各間隙の大きさにもよるが、通常、0.25mm以上0.5mm以下である。また、積層数が8、つまり8段積層の場合、通常、0.4mm以上0.8 mm以下、積層数が16、つまり16段積層の場合、通常、0.8mm以上1.5mm以下である。

【0019】

また、側壁5の幅Wは、構成する材料にもよるが、通常、0.5mm以上2.0mm以下、好ましくは0.5mm以上1.0mm以下である。0.7mm程度がより好ましい。側壁5の幅Wが0.5mm未満では、配線基板2上への配置が困難になるおそれがある。また、側壁5の幅Wが2.0mmを超えると、半導体装置10が大型化するおそれがある。

【0020】

さらに、側壁5と積層体1との離間距離dは、0.2mm以上2.0mm以下の範囲が好ましく、0.3mm以上1.0mm以下の範囲がより好ましい。側壁5と積層体1との離間距離dが0.2mm未満では、側壁5と積層体1との間隙へのアンダーフィル材6の供給が困難になる。また、側壁5と積層体1との離間距離dが2.0mmを超えると、半導体装置10が大型化する。

【0021】

側壁5と積層体1の間隙、配線基板2と積層体1の間隙、及び複数の半導体素子1a〜1eの各間隙に充填されるアンダーフィル材6としては、例えばエポキシ系樹脂、アクリル系樹脂、アミン系樹脂、シリコーン系樹脂、ポリイミド系樹脂等が用いられる。アンダーフィル材6に用いる樹脂は、配線基板2と各半導体素子1a〜1eの各間隙が狭いため、流動の良い低粘度である材料を選択することが好ましい。具体的には、エポキシ系樹脂等が好ましい。

【0022】

次に、この実施形態による半導体装置10の製造工程について、図2を用いて説明する。

【0023】

まず、図2(a)に示すように、配線基板2を用意し、その上面の接続パッド2aが形成されている半導体素子搭載エリアに、複数の半導体素子1a〜1dを順にフリップチップ接続する。すなわち、まず、1段目半導体素子1a表面の電極パッド上に半田ボール等を搭載して金属バンプ4aを形成し、配線基板2上面側に形成された接続パッド2aと接合させる。次に、2段目半導体素子1b表面の電極パッド上に半田ボール等を搭載して金属バンプ4bを形成し、1段目半導体素子1a裏面の電極パッドと接合する。次に、3段目半導体素子1c表面の電極パッド上に半田ボール等を搭載して金属バンプ4cを形成し、2段目半導体素子1b裏面の電極パッドと接合する。次に、4段目半導体素子1d表面の電極パッド上に半田ボール等を搭載して金属バンプ4dを形成し、3段目半導体素子1c裏面の電極パッドと接合する。さらに、5段目半導体素子1e表面の電極パッド上に半田ボール等を搭載して金属バンプ4eを形成し、4段目半導体素子1a裏面の電極パッドと接合する。なお、複数の半導体素子1a〜1dを、別工程で予めフリップチップ接続しておき、その積層体1を配線基板2上にフリップチップ接続するようにしてもよい。

【0024】

このようにして、配線基板2上への複数の半導体素子1a〜1eの積層体1の実装が完了したら、図2(b)に示すように、例えば、中央部分に、半導体素子1a〜1eの積層体1の収容できるだけの大きさの孔、厚さ方向に貫通する孔を設けた金属薄板(シート)を、接着剤層7を介して接着し、側壁5を形成する。

【0025】

次に、図2(c)に示すように、側壁5と複数の半導体素子1a〜1eの積層体1との間隙に上方より、アンダーフィル材供給用ノズルを挿入または近接させて、アンダーフィル材6を供給し、側壁5と半導体素子1a〜1eの積層体1の側面との間隙、配線基板2と積層された前記半導体素子1a〜1eの各間隙に充填させる。充填が完了したところで、アンダーフィル材6を硬化させる。これにより図1に示す半導体装置10が作製される。

【0026】

なお、大サイズの基板を用いて半導体装置10を多数個取りする場合には、例えば、図3に示すような、配線基板2となる配線部2Aを有する基板32が用いられる。この基板32の上面には、それぞれに配線部2Aを含むように格子状に区画壁34が形成されている。この区画壁34は、その幅方向中央にダイシング領域(ダイシングライン)Lを備えており、このダイシングラインLに沿って切断することで、最終的に側壁5を形成するものである。したがって、区画壁34は、側壁5を構成する材料によって形成されている。すなわち、この区画壁34は、一般には、金属、樹脂、セラミック等からなる、基板32に対応する形状、大きさの薄板(シート)に、それぞれに半導体素子1a〜1eの積層体1を収容できるだけの大きさの孔、厚さ方向に貫通する孔を多数設けたものを、基板32上に接着することによって形成される。区画壁34の基板32上の接着には、耐熱性の良好な接着剤が使用される。

【0027】

そして、薄板(シート)に設けられた孔のそれぞれにおいて、配線部2A上の半導体素子搭載エリアに、図2の場合と同様にして、複数の半導体素子1a〜1eをフリップチップ接続により多段に積層し、さらに、この積層された複数の半導体素子1a〜1eからなる積層体1と区画壁34との間隙にアンダーフィル材6を供給して、積層体1と区画壁34との間隙、基板32(配線部2A)と半導体素子1a〜1eの各間隙にアンダーフィル材6を充填し、硬化させる。

【0028】

その後、基板32の下面をダイシングテープ等(図示せず)に固定した後、ダイシングラインLに沿って、ダイヤモンドブレード等のブレードを用いて、区画壁34及び基板32を切断する。これにより、図1に示すような、配線基板2と、配線基板2上にフリップチップ接続により多段に積層された複数の半導体素子1a〜1eと、配線基板2の外周部に設けられた側壁5と、積層された複数の半導体素子1a〜1eと側壁5との間隙、配線基板2と半導体素子1a〜1eの各間隙に充填されたアンダーフィル材6とを備えた半導体装置10が多数個取りされる。

【0029】

前述したように、側壁5材料として、樹脂層を被覆した金属シートあるいは金属層を被覆した樹脂シート等の樹脂を含む複合材料、あるいは全体が樹脂からなる材料を用いた場合には、上記ダイシングラインLに沿って行う区画壁34の切断作業が容易となる。

【0030】

以上説明した実施形態によれば、配線基板上の外周部に形成した側壁によって、アンダーフィル材の水平方向の拡がりを抑制できるので、半導体素子の積層数が多くなっても、最上段の半導体素子の端面まで少ない使用量でアンダーフィル材を供給し、各半導体素子間の間隙に充填することができる。しかも、側壁は薄く、かつ所要の高さに形成できるので、半導体装置がそのために大型化したり厚肉化したりすることもない。また、アンダーフィル材が配線基板の端面に流れ出るおそれがないので、配線基板は流れた出たアンダーフィル材によって汚染されることもない。

【0031】

さらに、半導体装置を多数個取りする場合、隣接する半導体装置のアンダーフィル材同士が接触するおそれがないため、半導体装置間のピッチを狭くすることができ、その取り数を多くすることができる。さらに、側壁が半導体装置の補強材としても機能するため、アンダーフィル材で固定した半導体素子をさらに樹脂等によって封止しなくてもよく、材料コスト及び製造コストを低減することができる。

【0032】

以上、本発明の実施形態を説明したが、この実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。この新規な実施形態は、その他の様々な形態で実施し得るものであり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。この実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0033】

1…積層体、1a〜1e…半導体素子(半導体チップ)、2…配線基板、3a〜3d…貫通電極、4a〜4e…金属バンプ、5…側壁、6…アンダーフィル材。

【特許請求の範囲】

【請求項1】

配線基板と、

前記配線基板上にフリップチップ接続により多段に積層された複数の半導体素子と、

前記配線基板の外周部に立設され、前記半導体素子を囲繞する側壁と、

積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙に充填されたアンダーフィル材と

を具備することを特徴とする半導体装置。

【請求項2】

積層された前記複数の半導体素子と、前記側壁とが略同じ高さであることを特徴とする請求項1記載の半導体装置。

【請求項3】

積層された前記複数の半導体素子と前記側壁との離間距離が0.2mm以上2.0mm以下であることを特徴とする請求項1または2記載の半導体装置。

【請求項4】

積層された前記半導体素子の数が3以上である請求項1乃至3のいずれか1項記載の半導体装置。

【請求項5】

半導体素子搭載エリアとこの半導体素子搭載エリアを囲むように形成された側壁とを有する配線基板上に、複数の半導体素子をフリップチップ接続により多段に積層する工程と、

積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙にアンダーフィル材を充填する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項1】

配線基板と、

前記配線基板上にフリップチップ接続により多段に積層された複数の半導体素子と、

前記配線基板の外周部に立設され、前記半導体素子を囲繞する側壁と、

積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙に充填されたアンダーフィル材と

を具備することを特徴とする半導体装置。

【請求項2】

積層された前記複数の半導体素子と、前記側壁とが略同じ高さであることを特徴とする請求項1記載の半導体装置。

【請求項3】

積層された前記複数の半導体素子と前記側壁との離間距離が0.2mm以上2.0mm以下であることを特徴とする請求項1または2記載の半導体装置。

【請求項4】

積層された前記半導体素子の数が3以上である請求項1乃至3のいずれか1項記載の半導体装置。

【請求項5】

半導体素子搭載エリアとこの半導体素子搭載エリアを囲むように形成された側壁とを有する配線基板上に、複数の半導体素子をフリップチップ接続により多段に積層する工程と、

積層された前記複数の半導体素子と前記側壁との間隙、及び前記配線基板と前記半導体素子の各間隙にアンダーフィル材を充填する工程と

を具備することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−69988(P2013−69988A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−209104(P2011−209104)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]