Fターム[5F044KK01]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 基板 (2,939)

Fターム[5F044KK01]の下位に属するFターム

Fターム[5F044KK01]に分類される特許

1 - 20 / 1,192

半導体装置の製造方法、半導体装置、及び半導体素子

【課題】はんだによる短絡不良を低減すること。

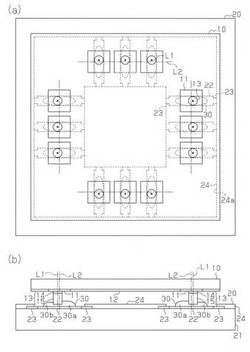

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。各々の電極端子13の中心軸L1は、電極パッド11の中心から、電極パッド11の配列方向と直交する方向に沿って半導体素子10の外側にずれた位置に形成されている。半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心L2は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】 半導体素子の実装時のボイドを抑制し、信頼性の高い半導体装置を製造可能な半導体装置の製造方法を提供すること。

【解決手段】 本発明は、被着体と、該被着体と電気的に接続された半導体素子と、該被着体と該半導体素子との間の空間を充填するアンダーフィル材を備える半導体装置の製造方法であって、基材と該基材上に積層されたアンダーフィル材とを備える封止シートを準備する工程と、半導体ウェハの接続部材が形成された面に上記封止シートを貼り合わせる工程と、上記半導体ウェハをダイシングして上記アンダーフィル材付きの半導体素子を形成する工程と、上記アンダーフィル材付きの半導体素子を100〜200℃で1秒以上保持する工程と、上記被着体と上記半導体素子の間の空間をアンダーフィル材で充填しつつ上記接続部材を介して上記半導体素子と上記被着体とを電気的に接続する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 半導体素子の実装時に半導体素子と被着体との電気的接続を良好に行い、接続信頼性の高い半導体装置を製造可能な半導体装置の製造方法を提供すること。

【解決手段】 本発明の半導体装置の製造方法は、アンダーフィル材を備える封止シートを準備する工程と、半導体ウェハの接続部材形成面と上記封止シートとを貼り合わせる工程と、上記半導体ウェハをダイシングして上記半導体素子を形成する工程と、上記被着体と上記半導体素子の間の空間をアンダーフィル材で充填しつつ上記接続部材を介して上記半導体素子と上記被着体とを電気的に接続する工程とを含み、上記接続工程は、上記接続部材と上記被着体とを下記条件(1)の温度α下で接触させる工程と、上記接触した接続部材を上記被着体に下記条件(2)の温度β下で固定する工程とを含む。

条件(1):接続部材の融点−100℃≦α<接続部材の融点

条件(2):接続部材の融点≦β≦接続部材の融点+100℃

(もっと読む)

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極上に選択的にはんだバンプ又ははんだ接合を形成できるリフローフィルムを提供し、更にこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】ポリビニルアルコールと、分子量500以下の水に溶解または分散する化合物と、分散したはんだ粒子とを含むフィルム21であって、前記分子量500以下の化合物はポリビニルアルコール100質量部に対して20〜300質量部であるリフローフィルム、および基板10の電極12面側に前記リフローフィルムを載置する工程、さらに平板12を載置する工程、加熱する工程、及び前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

電子部品用接着剤及び半導体チップ実装体の製造方法

【課題】ボイドの発生を抑制し、かつ、半導体チップ上面への這い上がりを生じにくい電子部品用接着剤を提供する。また、該電子部品用接着剤を用いた半導体チップ実装体の製造方法を提供する。

【解決手段】硬化性化合物と、硬化剤と、無機充填剤とを含有する電子部品用接着剤であって、25℃でE型粘度計を用いて測定した5rpmでの粘度をA1(Pa・s)、0.5rpmでの粘度をA2(Pa・s)としたとき、A1とA2/A1とが図1の実線及び破線で囲まれた範囲内(ただし、実線上は含むが破線上は含まない)であり、前記硬化性化合物100重量部に対して、前記硬化剤の配合量が5〜150重量部、前記無機充填剤の配合量が60〜400重量部である電子部品用接着剤。

(もっと読む)

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極のみに対して選択的にはんだバンプ又ははんだ接合を形成することができるリフローフィルムを提供し、さらにこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】溶媒に溶解可能な熱可塑性樹脂と、はんだ粒子とを含むフィルムであって、前記はんだ粒子は前記フィルム中に分散した状態であることを特徴とするリフローフィルム、および(ア)基板の電極面側に前記リフローフィルムを載置する工程、(イ)さらに平板を載置して固定する工程、(ウ)加熱する工程、及び(エ)前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

半導体装置

【課題】高い機械的強度を得ることができると共に、塗布形状の保持性を高く得ることができるエポキシ樹脂組成物を提供する。

【解決手段】半導体素子2を基板3に実装して形成された半導体装置4に関する。室温で液状のエポキシ樹脂組成物1を前記半導体素子2の周囲又はその一部のみに塗布し硬化させることによって前記半導体素子2と前記基板3とが接着されている。前記半導体素子2と前記基板3との隙間の全体にわたって充填させないようにしている。前記エポキシ樹脂組成物1が、エポキシ樹脂、硬化剤、無機充填材を含有する。前記無機充填材として、平均アスペクト比が2〜150の鱗片状無機物が、前記エポキシ樹脂組成物1全量に対して0.1〜30質量%含有されている。前記エポキシ樹脂組成物1のチクソ指数が3.0〜8.0である。

(もっと読む)

回路接続用接着フィルム、これを用いた回路接続構造体及び回路部材の接続方法

【課題】従来の回路基板より厚みの薄いガラス基板と半導体素子との接続に用いられた場合でも、優れた接続信頼性を維持しつつガラス基板の変形を抑制でき、しかもフィルム形成性にも優れる接着剤フィルム回路接続用接着フィルムを提供すること。

【解決手段】本発明は、接着剤組成物4b及び導電粒子5を含有する導電性接着剤層3bと、接着剤組成物4aを含有し、導電粒子を含有しない絶縁性接着剤層3aと、を備え、絶縁性接着剤層3aの厚みTiと、導電性接着剤層3bの厚みTcとが、下記式(1)の関係を満たす回路接続用接着フィルム10に関する。

Ti/Tc≧1.5 ・・・(1)

(もっと読む)

半導体デバイスの製造方法

【課題】接着剤が付着した半導体チップ個片を効率的に得ると共に、半導体チップと配線基板とを良好に接続する。

【解決手段】半導体デバイスの製造方法は、半導体ウェハ6の回路面6aがダイシングテープ9側を向くように、ダイシングテープ9、接着剤層3及び半導体ウェハ6がこの順に積層された積層体60を準備する。半導体ウェハ6の裏面6bから回路面6aの回路パターンPを認識することによってカット位置を認識する。少なくとも半導体ウェハ6及び接着剤層3を、積層体60の厚み方向に切断する。切断後、ダイシングテープ9と接着剤層3とを剥離させることによって半導体チップ26を作製する。この半導体チップ26の突出電極4と、配線基板40の配線12とを位置合わせする。配線12と突出電極4とが電気的に接続されるように、配線基板40と半導体チップ26とを接着剤層23を介して接続する。

(もっと読む)

電子デバイス、及び電子機器

【課題】電子デバイスを小型化、低背化し、且つコストを低減する手段を得る。

【解決手段】電子デバイスは、第1の電子素子20と、第1の電子素子20を搭載する絶縁基板11と、を備えた電子デバイスであって、絶縁基板11は一方の主面に第1の電子素子20を搭載する電極パッド12を有すると共に、他方の主面に実装端子13を備え、第1の電子素子20に設けた端子と電極パッド12とは、接続用導電部材15を介して導通接続されている。

(もっと読む)

エレクトロニクスアセンブリを製造する方法

【課題】アンダーフィル又は接着剤によって隣接する回路素子を汚染することなく、隣接する回路素子を物理的にできる限り近づけて配置できるようにするエレクトロニクスアセンブリを製造するための方法を提供する。

【解決手段】基板12上に液体障壁30を形成することと、液体障壁の一方の側に第1の回路素子22を配置することと、液体障壁の反対側に第2の回路素子24を配置する。液体44が第1の回路素子に塗布される。第1の回路素子と第2の回路素子との間の間隔を最小にすることができるように、液体障壁を用いて、第1の回路素子に塗布された液体が第2の回路素子を汚染するのを防ぐ。

(もっと読む)

半導体装置

【課題】半導体装置のI/O系および非I/O系の電源およびGNDをバランス良く強化して、低電圧動作性能および高速動作性能を向上させること。

【解決手段】配線基板2の一面は、接続パッド6Aの列を取り囲むように形成され、かつVSS用接続パッド6A−1と配線16を介して接続されたVSS用面状導体パターン18を備える。配線基板2の他面は、複数のVSSQ用外部端子7−3を連結するように配置されたVSSQ用面状導体パターン21と、複数のVDDQ用外部端子7−4を連結するように配置されたVDDQ用面状導体パターン22とを備える。

(もっと読む)

接続構造体の製造装置及びその製造方法

【課題】二段階の加熱を行う異方性導電接着剤を用いて基板に半導体チップを接続する場合に、基板や半導体チップを含んで構成される接続構造体の生産効率の向上を図るための接続構造体の製造装置及びその製造方法を提供すること。

【解決手段】プレヒートエリアAでは、異方性導電接着剤3の内部に存在する気泡を脱泡させる等のために接続構造体Wを第1温度で加熱するための予備加熱作業が行われ、圧着加熱エリアでは、半導体チップを基板1及び異方性導電接着剤に向かって加圧するとともに、異方性導電接着剤を加熱硬化させるために接続構造体Wを第1温度よりも高い第2温度で加熱するための圧着加熱作業が行われ、圧着加熱エリアにて先行する接続構造体Wについての圧着加熱作業が行われているときに、プレヒートエリアAにて後続の接続構造体Wについての予備加熱作業が行われる。

(もっと読む)

ハンダ接続シートおよびそれを用いた電子部品の実装方法

【課題】電子部品に形成された電極端子間距離が狭い場合であっても、隣接する電極端子間を短絡させることなく、しかも容易且つ確実に、回路基板の接続用端子に電子部品の各電極端子を接続させることが可能なハンダ接続シートと、それを用いた電子部品の実装方法を提供すること。

【解決手段】織布または不織布で構成してあり、表裏面を貫通する複数の貫通孔6が所定パターンで形成してあるシート基材4と、貫通孔6の内部に保持され、予めボール状に成形されたハンダ部材8と、を有するハンダ接続シート2である。

(もっと読む)

アンダーフィルとの間で化学的に硬化物を形成する無洗浄フラックス

【課題】 無溶剤の熱可塑性残渣を生成し、その熱可塑性残渣がアンダーフィル成分と反応して熱硬化性樹脂を形成する無洗浄フラックス、を提供すること。

【解決手段】 フラックス活性剤としてジカルボン酸、樹脂成分として平均官能基数が約2.0を有するエポキシのプレポリマー、および粘度調整剤として沸点260度以下の溶剤を含む無洗浄フラックスが、リフロー時にはんだの酸化膜を除去するとともに、ガラス転移温度が100℃以下でアンダーフィル塗布時に液状となる熱可塑性エポキシ硬化物を形成する。粘度調整剤としての溶剤は、リフロー中にそのほとんど全量が揮発し、リフロー後、洗浄することなく、アンダーフィルを塗布する際、その硬化物はアンダーフィルと相溶してアンダーフィルに含まれる硬化剤と反応し、アンダーフィルとともに3次元架橋構造を形成できる。

(もっと読む)

電子部品の実装構造体

【課題】好適に空間を封止することが可能な電子部品の実装構造体を提供する。

【解決手段】実装構造体1は、支持部材5と、該支持部材5上にバンプ8を介して実装された複数の圧電素子7と、複数の圧電素子7を共に覆い、複数の圧電素子7と支持部材5との間の空間Sを密閉する封止樹脂(樹脂部9)とを有する。複数の圧電素子7は、隣り合う圧電素子7の下面19a間の距離d1が下面19aよりも上方側の所定位置間(例えば上面19b間)の距離d2よりも大きい。そして、樹脂部9は、隣り合う圧電素子7間の間隙Wの少なくとも上方側の一部に充填された介在部9eを有する。

(もっと読む)

半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセス

【課題】 エレクトロマイグレーション(EM)の耐性があり、ハイエンドの半導体チップにも採用できるようなプロセスとして、半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセスの提供。

【解決手段】

電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。マザーボードへの積層時(二次)は高温はんだを溶融させる。マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持することができる。

(もっと読む)

半導体装置

【課題】アンダーフィルの収縮が半導体チップの電気特性に及ぼす影響を低減できる半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ2とベース材3との積層構造を有する。半導体チップ2の表面上に電極21が形成されており、ベース材3の表面上に電極31が形成されている。半導体チップ2の前記表面とベース材3の前記表面とが対向すると共に電極21と電極31とが突起電極4を介して電気的に接続されている。半導体チップ2の前記表面とベース材3の前記表面とに挟まれた領域のうち、電極配置領域B以外の他の領域に位置する部分のアンダーフィル5に分断領域6が設けられている。

(もっと読む)

半導体装置の製造方法、及び半導体製造装置

【課題】吸着ツールに対する半導体チップの位置ずれを補正して被搭載体に搭載可能となり、被搭載体に対する半導体チップの位置精度の向上が図れる半導体装置の製造方法、および、製造装置を提供する。

【解決手段】半導体チップ2を吸着ツール12で吸着する工程と、吸着ツールに吸着された半導体チップの裏面から赤外線カメラ13で赤外線画像を撮影することにより半導体チップの表面にあるアライメントマークの位置を検出する工程と、赤外線カメラによって検出されたアライメントマークの位置に基づいて吸着ツールに対する半導体チップの位置ズレを補正して半導体チップを被搭載体3に搭載する工程と、を含む。

(もっと読む)

1 - 20 / 1,192

[ Back to top ]