Fターム[2H092JA26]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 種類 (8,621) | TFT (8,450) | 逆スタガ構造(ボトムゲート構造) (2,339)

Fターム[2H092JA26]に分類される特許

61 - 80 / 2,339

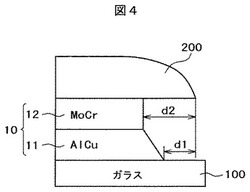

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

液晶表示装置

【課題】IPSタイプの液晶表示装置において、走査線引出し線に印加されるゲート電圧の影響によって対向基板の内側が帯電し、画面周辺に白抜けが生ずる現象を防止する。

【解決手段】走査線引出し線31は、対向電極108と同層で形成されたシールド電極107によって覆われている。走査線引出し線31はシール材20の下にも形成されている。シールド電極107はシール材20の下まで延在し、シールド電極107の下に形成されている走査線引出し線31の全数を被覆しているので、シールド効果は高い。また、シール材20の下に形成されたシールド電極107には抜きパターン1071が形成されているので、シールド電極107と、それをサンドイッチする無機パッシベーション膜106および上部絶縁膜109との間の接着強度の低下を防止することが出来る。

(もっと読む)

液晶表示装置

【課題】基板のずれを防止し、微小輝点の発生率を低減することを目的とする。

【解決手段】液晶表示装置は、第1基板28と第2基板36とのギャップを保持するスペーサ80と、第2配向膜22側に窪み66を有する下地層40と、対向する第1配向膜18の第1面20及び第2配向膜22の第2面24に挟まれた液晶層26と、を有し、第1配向膜18は、スペーサ80の形状に沿って、第1面20が突出する第1凸部82を有し、下地層40の窪み66の底面は、凹凸状に形成され、第2配向膜22の第2面24には、下地層40の形状に対応して窪み84が形成され、第2配向膜22の窪み84は、第2配向膜22の第2面24よりも低い第2凸部76と、第2凸部76よりも低い底面を有する凹部78とによって凹凸状に形成され、第1配向膜18の第1凸部82は、第2配向膜22の窪み84に入って第2凸部76に接触している。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を抑制することを可能とする。

【解決手段】 第1方向に沿って延出した第1ゲート配線及び第2ゲート配線と、第1ゲート配線と第2ゲート配線との間の略中間に位置した補助容量線と、第2方向に沿って延出した第1ソース配線及び第2ソース配線と、第1ゲート配線及び第1ソース配線と電気的に接続されたスイッチング素子と、補助容量線の上方に位置し前記スイッチング素子とコンタクトし第1方向に沿って延出したコンタクト部、コンタクト部の第1ソース配線側に繋がり第2方向に沿って延出した第1主画素電極、及び、コンタクト部の第2ソース配線側に繋がり第2方向に沿って延出した第2主画素電極を備えた画素電極と、を備えた第1基板と、第1主画素電極と第2主画素電極との間、第1ソース配線及び第2ソース配線の上方にそれぞれ位置し第2方向に沿ってそれぞれ延出した主共通電極を備えた共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を抑制する液晶表示装置を提供する。

【解決手段】第1信号配線Gと、第1信号配線Gと交差する方向Yに延びるとともに第1信号配線Gと交差する位置において第1信号線Gが延びる方向Xにおける幅が広くなった幅広部SAを備えた第2信号配線Sと、第2信号配線Sの間において第1信号配線Gと交差する方向に延びた主画素電極PAと、主画素電極PAと電気的に接続された副画素電極PBと、を含む画素電極PEと、を備えた第1基板ARと、画素電極PEの両側に配置された共通電極CEを備えた第2基板CTと、第1基板ARと第2基板CTとの間に挟持された液晶層LQと、を備え、第1信号配線Gの全体が幅広部SAと副画素電極PBとの少なくとも一方と重なっている液晶表示装置。

(もっと読む)

薄膜トランジスタアレイ、薄膜トランジスタアレイの製造方法、画像表示装置

【課題】高開口率を得るために形成する層間絶縁膜のパターニング性、歩留まりを向上させ、生産性に優れた薄膜トランジスタアレイを提供する。

【解決手段】ゲート絶縁膜2上には、ゲート電極11に重なる位置に、ドレイン電極16と、ソース電極17と、を隔てて設けてあり、ドレイン電極16には、画素電極15を接続し、ソース電極17には、ソース配線18を接続してある。また、ゲート絶縁膜2上には、ドレイン電極16及びソース電極17の双方に重なるように、半導体層3を設けてある。ゲート絶縁膜2上には、画素電極15の一部を露出させた状態で、ソース電極17、ソース配線18、ドレイン電極16、画素電極15、半導体層3を封止する一層目封止層4を設け、一層目封止層4上には、ソース電極17及びソース配線18に重なる位置に、二層目封止層5を設けてある。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を抑制することを可能とする。

【解決手段】第1方向に沿って延出した第1ゲート配線及び第2ゲート配線と、前記第1ゲート配線と前記第2ゲート配線との間の略中間に位置した補助容量線と、第2方向に沿って延出した第1ソース配線及び第2ソース配線と、前記第1ソース配線及び前記第2ソース配線と同一材料によって形成された画素電極であって、前記補助容量線の上方に位置する副画素電極、前記副画素電極の前記第1ソース配線側に繋がり第2方向に沿って延出した第1主画素電極、及び、前記副画素電極の前記第2ソース配線側に繋がり第2方向に沿って延出した第2主画素電極を備えた画素電極と、を備えた第1基板と、前記第1主画素電極と前記第2主画素電極との間、前記第1ソース配線の上方、及び、前記第2ソース配線の上方にそれぞれ位置し第2方向に沿ってそれぞれ延出した主共通電極を備えた共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

液晶表示装置

【課題】 IPSモード及びFFSモードに比べて光透過率の高い横電界モードあるいは斜め電界モードを採ることができ、光反射表示と光透過表示とを両立しても十分な輝度レベルの画像を表示することができる液晶表示装置を提供する。

【解決手段】 液晶表示装置は、第1基板と、前記第1基板に隙間を置いて対向配置された第2基板と、前記第1基板及び第2基板間に挟持された液晶層LQと、複数の画素と、第1偏光板PL1と、第2偏光板PL2と、を備えている。各画素は、光反射領域R3及び光透過領域R4を含んでいる。各画素は、第1基板上に形成され、光反射領域R3に重なった光反射層30と、第1基板上に形成され、第2方向Yに沿って延出した主画素電極と、第2基板上に形成され、第1方向に主画素電極を挟んで位置し第2方向Yに沿って延出した一対の主共通電極と、を有している。

(もっと読む)

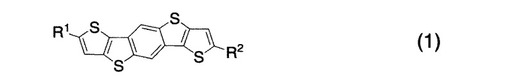

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の提供。

【解決手段】本発明の実施形態に係る液晶表示装置の場合、共通電極の真上または直下に共通電圧線を形成して、直接的に接触させることにより、共通電圧線の信号遅延を低減するとともに、液晶表示装置の開口率の低下を防ぐことができる。

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極およびドレイン電極と、保護膜と、を有し、該保護膜は金属酸化膜を有し、該金属酸化膜は、膜密度が3.2g/cm3以上である。

(もっと読む)

トランジスタおよびその製造方法、並びに表示装置

【課題】良好な特性を有するトランジスタおよびその製造方法、並びにそのトランジスタを備えた表示装置を提供する

【解決手段】制御電極と、制御電極に対向する能動層と、能動層に電気的に接続された第1電極および第2電極と、制御電極と第1電極および第2電極との間に設けられ、ジアリルイソフタレート樹脂を含有する絶縁層とを備えたトランジスタ。

(もっと読む)

液晶表示装置

【課題】 液晶表示装置のコントラストと応答速度の両立を図る。

【解決手段】 表示電極の長辺42と、配向制御窓50の直線部分51の距離dを短くすると、液晶の応答速度が速くなる。一方、配向制御窓50を大きくする(距離dを短くすることに相当する)と液晶のコントラストが小さくなり好ましくない。前記距離dが、25μm〜30μm以下になると、応答速度向上の効果が少なくなる。したがって、距離dを25μm〜30μmにすることが好ましい。また配向制御窓50はその幅を7μm程度とすることがより好ましい。

(もっと読む)

液晶表示装置

【課題】 信頼性の高い液晶表示装置を提供することにある。

【解決手段】 マトリクス状に配置された複数の画素PXを含むアクティブエリアACTと、アクティブエリアACTの周囲に配置された内蔵回路GDR、GDL、CLK、CSWを有する第1基板ARと、第1基板ARと対向して配置された第2基板CTと、第1基板ARと、第2基板CTとの間に挟持された液晶層LQと、を備え、内蔵回路の動作に用いられない電圧が印加され、内蔵回路と対向して配置されたシールド層100を備えた液晶表示装置。

(もっと読む)

61 - 80 / 2,339

[ Back to top ]