Fターム[2H092KA12]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | ゲート絶縁層 (1,439) | 無機材料 (1,279)

Fターム[2H092KA12]に分類される特許

21 - 40 / 1,279

半導体装置

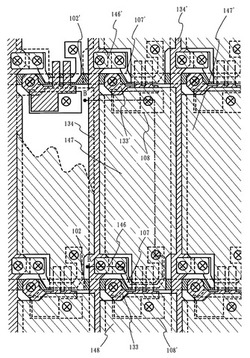

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

半導体装置の作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置の作製方法を提供する。

【解決手段】GRTA装置を用いて、第1の酸化物半導体膜に熱を加え、熱が加えられた第1の酸化物半導体膜に、酸素を添加して第2の酸化物半導体膜とし、GRTA装置を用いて、酸素が添加された第2の酸化物半導体膜に熱を加える。GRTA装置は、高温のガスを用いて加熱処理を行う装置であって、当該GRTA装置を用いると短時間での高温加熱処理が可能となる。

(もっと読む)

電気光学装置および電子機器

【課題】配線間の短絡等を発生させずに、複数の配線が並列する配線領域の幅寸法を狭めることのできる電気光学装置、および電子機器を提供すること。

【解決手段】電気光学装置100では、素子基板10の辺10eと画素電極配列領域10pとの間で複数の配線105が並列する配線領域11は、一部の配線105と他の配線105とが異なる層に位置する第2配線領域11bとを備えており、かかる第2配線領域11bでは、異なる層に位置する配線105の間に平面視で広い隙間を設けなくても短絡等の問題が発生しない。このため、第2配線領域11bについては、配線105間の短絡等を発生させず、幅方向の寸法を第1配線領域11aより狭くすることができる。

(もっと読む)

電気光学装置および電子機器

【課題】並列に電気的に接続された複数の保持容量を積層した場合でも、いずれの保持容量に不具合が発生したかを容易かつ確実に検査することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100においては、並列に電気的に接続された第1保持容量70aと第2保持容量70bとによって保持容量70が形成され、かつ、第1保持容量70aと第2保持容量70bとは積層された構造になっている。また、素子基板10の端部と画像表示領域との間には、第1保持容量70aと同一の層構造を備えた検査用第1容量と、第2保持容量70bと同一の層構造を備えた検査用第2容量が形成されているとともに、検査用第1容量に電気的に接続する第1容量検査用端子対と、検査用第2容量に電気的に接続する第2容量検査用端子対とが設けられている。

(もっと読む)

液晶表示装置

【課題】表示領域の周辺部分近傍に見られる表示ムラを無くし、優れた表示品位の液晶表示装置を得る。

【解決手段】各々にスイッチング素子を有する複数の画素13がマトリクス状に形成された表示領域3と表示領域3の外側であってスイッチング素子に信号を供給する引き出し配線6が形成された引き出し配線領域4とを有するアレイ基板2と、アレイ基板2上に、表示領域3と引き出し配線領域4の境界からアレイ基板2端部に向けて、相互に平行に延在する複数の畝状の凸部10と、表示領域3を覆う配向膜9と、を備える。

(もっと読む)

液晶表示装置の製造方法

【課題】 製造工程を単純化して第1の金属膜上に第2の金属層が積層された積層構造を有する領域および第1の金属膜のみで形成されている領域からなるゲート配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】 液晶表示装置の製造方法であって、第1の金属膜3b上に第2の金属膜3cが積層された積層構造を有する領域および第1の金属膜3bのみで形成されている領域からなるゲート配線3を、多階調マスクを用いて、感光性樹脂膜12を、積層構造となる領域では膜厚の厚い厚膜部12aになり、ゲート電極3aの少なくとも半導体層5と重なっている領域では厚膜部12aよりも膜厚の薄い薄膜部12bになるようにそれぞれ複数のゲート配線3のパターンにするとともに、隣接するゲート配線3のパターン間の領域では第2の金属膜3cが露出するようにパターニングする工程を含んでいる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】フォトリソグラフィ工程を増やすことなく液晶表示装置を製造することを目的とする。

【解決手段】液晶表示装置は、第1透明電極14の端部に載る第1絶縁層30と、第1絶縁層30下のゲート電極18と、第1絶縁層30上の半導体層34と、半導体層34上から第1透明電極14上に至るように形成されて第1透明電極14に電気的に接続する第1配線46と、第1配線46から間隔をあけて半導体層34上から引き出された第2配線48と、第1配線46、第2配線48、半導体層34及び第1透明電極14を覆う第2絶縁層54と、第2絶縁層54上に形成された第2透明電極60と、第2透明電極60の上に配置された液晶層66と、を有する。第1透明電極14と第2透明電極60の間に印加される電圧によって、基板10の面方向に電界を加えて、液晶層66の液晶分子を基板10と平行な面内で回転させる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜とゲート絶縁膜との界面において、電子の界面散乱を抑制することで、電気的特性に優れたトランジスタを提供する。

【解決手段】基板上に酸化物半導体膜を形成し、酸化物半導体膜上に酸化物半導体以外の半導体膜を形成した後、酸化物半導体膜と該半導体膜との界面において、酸化物半導体膜中の酸素原子と半導体膜中の原子とを結合させる。これにより、酸化物半導体膜と該半導体膜との界面において構造を連続させることができる。また、酸化物半導体膜から脱離した酸素が、該半導体膜に拡散することで、該半導体膜は酸化されるため、絶縁膜とすることができる。このようにして形成されたゲート絶縁膜を用いることで、酸化物半導体膜とゲート絶縁膜との界面において電子の界面散乱が抑制され、電気的特性に優れたトランジスタを作製できる。

(もっと読む)

酸化物半導体及び半導体装置

【課題】酸化物半導体の組成若しくは欠陥制御をすることを目的の一とし、また、薄膜ト

ランジスタの電界効果移動度を高め、オフ電流を抑えつつ十分なオンオフ比を得ることを

他の目的の一とする。

【解決手段】InMO3(ZnO)n(M=Ga、Fe、Ni、Mn、Co及びAlから

選ばれた一又は複数の元素、nは1以上50未満の非整数)でありさらに水素を含む。こ

の場合において、Znの濃度がIn及びM(M=Fe、Ga、Ni及びAlから選ばれた

一又は複数の元素)よりも低くする。また、当該酸化物半導体はアモルファス構造を有し

ている。ここでnの値は、好ましくは1以上50未満の非整数、より好ましくは10未満

の非整数とする。

(もっと読む)

積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法

【課題】バリア性の高い保護層を有する積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法を提供する。

【解決手段】導体または半導体を含む有機層と、絶縁材料により構成され、前記有機層を覆う保護層と、外周が前記絶縁材料と親和性を有する親和層に覆われ、前記保護層に分散された複数の粒体とを備えた積層構造。

(もっと読む)

電気光学装置、及び電子機器

【課題】液晶装置等の電気光学装置において、保持容量を十分に確保することができ、高品質な画像を表示可能とする。

【解決手段】ゲート電極30gと電気的に接続された走査線3aと、データ線側ソースドレイン領域30sと電気的に接続されたデータ線6aと、画素電極側ソースドレイン領域30dと電気的に接続された画素電極27と、容量線3bに電気的に接続された第1容量電極16aと、第1容量電極16aと対向して設けられた第2容量電極16cと、第1容量電極16aと第2容量電極16cとに挟持された誘電体層16bと、を有する容量素子16と、を備え、層間絶縁膜11eに設けられた複数の第1コンタクトホールCNT4を介して第1容量電極16aと容量線3bとは電気的に接続される。

(もっと読む)

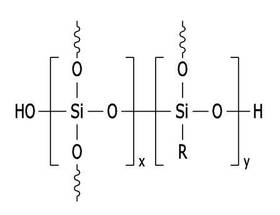

保護膜溶液組成物、薄膜トランジスター表示板及び薄膜トランジスター表示板の製造方法

【課題】保護膜溶液組成物を提供すること。

【解決手段】下記の化学式1で表わされる有機シロキサン樹脂を含む保護膜溶液組成物:

・・・化学式1

(式中、Rは1乃至25個の炭素を有する飽和炭化水素または不飽和炭化水素から選ばれた少なくとも一つの置換基であり、x、yはそれぞれ1乃至200であり、各波線は水素原子、xシロキサン単位またはyシロキサン単位との結合を示すか、あるいは、xシロキサン単位、yシロキサン単位またはこれらの組み合わせを含む他の有機シロキサン鎖のxシロキサン単位またはyシロキサン単位との結合を示す)。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】 第1方向に沿って延出し第2方向に沿って第1ピッチで配置された第1ゲート配線及び第2ゲート配線と、第2方向に沿って延出し第1方向に沿って第1ピッチよりも大きな第2ピッチで配置された第1ソース配線及び第2ソース配線と、半導体層と、第1ゲート配線と電気的に接続されたゲート電極と、半導体層にコンタクトし第1ソース配線と電気的に接続されたソース電極と、第1ソース配線及び第2ソース配線と同一材料によって形成されたドレイン電極であって半導体層にコンタクトした第1電極部、第1電極部に繋がり第1方向に沿って延出した第2電極部、及び、第1電極部に繋がり第1方向に沿って延出した第3電極部を備えたドレイン電極と、を備えた第1基板と、第2電極部と第3電極部との間に位置し第1方向に沿って延出した主共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】 有機樹脂膜を有するTFTアレイ基板の製造工程において、ブラシ洗浄の際に異物が有機平坦化膜表面にキズを生じさせることがある。このようにキズが生じた有機平坦化膜上に、画素電極となる透明電極膜を成膜した場合、キズ上の透明電極膜も断線してしまい、画素電極に信号が伝わらず表示不良を引き起こすことがある。

【解決手段】 有機平坦化膜を塗布する工程と、中間調露光を用いて有機平坦化膜に凹凸を形成する工程と、凹凸が形成された有機平坦化膜表面をロールブラシを用いて洗浄する工程と、洗浄工程後に、有機平坦化膜上に画素電極を構成する透明導電膜を成膜する工程とを備えた薄膜トランジスタアレイ基板の製造方法を提供する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置

【課題】アライメント精度良く半導体層を形成し、かつ、プロセス数を増やすことなくトランジスタの素子分離を行うことのできる薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置を提供する。

【解決手段】薄膜トランジスタ50は、基板1と、基板1上に形成されたゲート電極2と、基板1とゲート電極2とにわたって、これらの上に形成されたゲート絶縁体層4と、ゲート絶縁体層4上に形成された半導体層5と、半導体層5上に形成された保護層6と、ゲート絶縁体層4と半導体層5と保護層6とにわたって、これらの上に形成された、ソース電極7及びドレイン電極8と、を有し、半導体層5における、ソース電極7とドレイン電極8との間のチャネル部を流れる電流の方向の一端5aは、ソース電極7の一端7aと一致し、半導体層5における他端5bは、ドレイン電極8の一端8aと一致している。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

21 - 40 / 1,279

[ Back to top ]