Fターム[2H092MA07]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | CVD (1,864)

Fターム[2H092MA07]の下位に属するFターム

Fターム[2H092MA07]に分類される特許

41 - 60 / 739

薄膜半導体装置と薄膜半導体装置を用いた表示装置

【課題】IGZO等の酸化物半導体膜からなる薄膜半導体装置において、無酸素雰囲気中で加熱しても酸素が酸化物半導体膜に拡散してTFT特性を発現する薄膜半導体装置を提供すること。

【解決手段】薄膜半導体装置は、ガラスの基板20、ゲート電極23G,ゲート絶縁膜21、ソース電極23S、ドレイン電極23D、IGZOの酸化物半導体膜24、二酸化マンガン(MnO2)の酸素放出絶縁膜25、保護膜22からなる。薄膜半導体装置は、蛍光表示装置等の薄膜形成時における加熱工程、焼成工程、封着工程において加熱すると、酸素が酸素放出絶縁膜25から放出されて酸化物半導体膜24に拡散してTFT特性を発現する。

(もっと読む)

電気光学装置および投射型表示装置

【課題】反射性画素電極の上層側に絶縁膜が形成されているか否かにかかわらず端子電極を設けることができるとともに、深いコンタクトホールを形成しなくても端子電極の導通を図ることができる電気光学装置、および投射型表示装置を提供すること。

【解決手段】電気光学装置100において、端子電極102は、反射性の画素電極9aと同一の層に設けられているとともに、画素電極9aを構成する導電膜と同一種類の導電材料からなる。このため、画素電極9aの上層側に平坦化膜17等の絶縁膜が形成されているか否かにかかわらず、端子電極102を構成することができる。また、端子電極102を導通させるためのコンタクトホール45sが浅い。画素電極9aおよび端子電極102の上層側には平坦化膜17が設けられており、平坦化膜17の端子電極102と重なる領域には開口部17sが設けられている。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

半導体装置の作製方法

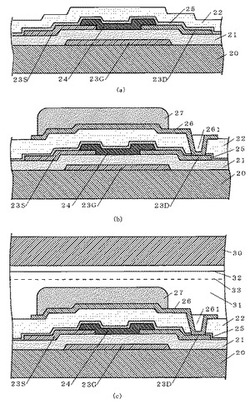

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】少なくとも微結晶半導体領域及び非晶質半導体領域が積層する半導体膜を有する逆スタガ型の薄膜トランジスタにおいて、半導体膜上に導電膜及びエッチング保護膜を積層形成し、エッチング保護膜上にマスクを形成し、エッチング保護膜、導電膜及び非晶質半導体領域の一部をエッチングする第1のエッチング処理の後、マスクを除去する。次に、上記エッチングされたエッチング保護膜をマスクとして、露出した非晶質半導体領域及び微結晶半導体領域の一部をドライエッチングする第2のエッチング処理により、微結晶半導体領域の一部を露出させ、バックチャネル領域を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

液晶パネル及びそれを用いた電子機器並びに投写型表示装置

【課題】半導体装置でパシベーション膜として一般的に使用されている減圧CVD法による窒化シリコン膜は、膜厚の10%程度のばらつきが生じるので、これを反射型液晶パネルに用いると、パシベーション膜の膜厚のばらつきによって反射率が大きく変化したり、液晶の屈折率が変動したりするという不具合がある。

【解決手段】基板(1)上に反射電極(14)がマトリックス状に形成されるとともに各反射電極に対応して各々トランジスタが形成され、前記トランジスタを介して前記反射電極に電圧が印加されるように構成された液晶パネル用基板において、パシベーション膜(17)として、膜厚が500〜2000オングストロームの酸化シリコン膜を使用し、入射光の波長に応じて膜厚を適当な値に設定するようにした。

(もっと読む)

電気光学装置用基板の製造方法および電気光学装置用基板

【課題】反射層の上層に屈折率の異なる複数の透光膜を積層した場合でも、透光膜の膜厚の測定結果に基づいて、透光膜の表面側からの研磨量やエッチング量を適正に設定することのできる電気光学装置用基板の製造方法、および電気光学装置用基板を提供すること。

【解決手段】電気光学装置の素子基板10の製造方法では、画素電極9aと同一の層あるいは画素電極9aより下層側にモニター用反射パターン7z、9zを形成しておき、画素電極9aおよびモニター用反射パターン7z、9zの上層側に第1透光膜181、および第2透光膜182を形成する。また、第2透光膜182のモニター用反射パターン7z、9zに重なる部分を除去した後、第3透光膜17を形成する。この状態で、モニター用反射パターン7z、9zに光を照射し、膜厚を測定する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

アクティブマトリクス基板及びそれを備えた表示パネル

【課題】フォトマスクの枚数を増やすことなく、酸化物半導体の半導体層を用いたTFTの特性の低下を抑制することにある。

【解決手段】マトリクス状の複数の画素電極Pと、各画素電極Pに接続されたTFT5と、互いに平行に延びる複数のソース線15aとを備え、TFT5が、絶縁基板10上のゲート電極11aと、ゲート電極11aを覆うゲート絶縁膜12aと、ゲート絶縁膜12a上でゲート電極11aに重なる酸化物半導体層13aと、酸化物半導体層13aに接続されたソース電極17a及びドレイン電極17bとを備え、ソース電極17a及びドレイン電極17bと酸化物半導体層13aとの間には、酸化物半導体層13aを覆う保護絶縁膜14aが設けられ、各ソース線15aは、金属材料により形成され、ソース電極17a及びドレイン電極17bは、各画素電極Pと同一材料により形成されている。

(もっと読む)

液晶表示装置

【課題】横電界方式で液晶層を駆動する液晶表示装置において、その画像表示性能を向上させる。

【解決手段】画素領域のそれぞれには、ドレイン信号線DLに接続された薄膜トランジスタTFTと、複数のスリットを有し且つ透明導電膜で形成される第1の電極と、前記薄膜トランジスタと前記第1の電極を接続する接続領域を有し、透明導電膜で形成される平面状の第2の電極を有し、前記第2の電極は、前記第1の電極と前記第1の基板間に形成され、且つ、前記第1の電極とゲート信号線GLに重畳し、さらに、隣接する前記画素領域の第2の電極と接続されていることを特徴とする液晶表示装置である。

(もっと読む)

デバイスおよび表示装置

【課題】基板上に形成された絶縁膜の応力を低減し、歩留まりが向上したデバイスおよびこのデバイスを備えた表示装置を提供する。

【解決手段】本開示の表示装置は、基板と、基板上の一部の領域に形成された金属層と、金属層上に設けられると共に、金属層未形成領域の少なくとも一部に溝を有する第1絶縁膜とを備える。

(もっと読む)

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

【課題】画素電極の電圧が保持され、画質が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基材110上で半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記チャネル領域を制御するゲート電極140と、前記ドレイン電極130と接続され液晶材料を駆動する画素電極190と、を複数有するアクティブマトリクス基板において、複数の前記画素電極190の間の空間に配された無機絶縁膜195と、前記画素電極190とは接触せずに、前記無機絶縁膜195と接触するようにして配された遮光膜200と、を有することを特徴とする。

(もっと読む)

液晶表示装置

【課題】層数を減らしたIPS方式の液晶表示装置において、画素電極パターニング時の現像液によって、映像信号線が断線することを防止する。

【解決手段】ゲート絶縁膜102の上に映像信号線20および画素電極106を形成するITOが存在している。ITOにはピンホールが存在している。ITOのパターニングのためのレジスト200は、画素電極パターンとともに、映像信号線を覆うように形成する。映像信号線を覆ってレジストが形成されているので、レジスト現像時の現像液によって、映像信号線が侵されて、映像信号線が断線することを防止することが出来る。その後、ITOをエッチングする。ITOは、画素電極部分と、映像信号線を、上面および側面を覆った形で存在する。よって、ITOパターニング時の現像液による映像信号線の断線を防止することが出来る。

(もっと読む)

薄膜トランジスタ構造、ならびにその構造を備えた薄膜トランジスタおよび表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、保護膜等の形成時に酸化処理層を必要とせずに、薄膜トランジスタの電気特性を安定させることが可能である酸化物半導体層を提供する。

【解決手段】基板上に少なくとも、基板側から順に、酸化物半導体層と、ソース・ドレイン電極と、保護膜とを備えた薄膜トランジスタ構造であって、前記酸化物半導体層は、金属元素全体に占めるZnの含有量が50原子%以上であり、ソース・ドレイン電極および保護膜側に形成される第1酸化物半導体層と、In、Ga、およびZnよりなる群から選択される少なくとも1種の元素を含み、基板側に形成される第2酸化物半導体層との積層体であり、かつ、前記第1酸化物半導体層と、前記ソース・ドレイン電極および保護膜とが、直接接触していることを特徴とする薄膜トランジスタ構造。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置及び表示装置の製造方法を提供すること。

【解決手段】表示装置は下部基板、有機膜パターン、第1画素電極、誘電膜、及び第2画素電極を含む。下部基板はスイッチング素子を具備する。有機膜パターンは、前記下部基板上に配置され、画素領域に段差部を含む。第1画素電極は画素領域の有機膜パターン上に配置される。誘電膜は第1画素電極上に配置される。第2画素電極は誘電膜上で第1画素電極と部分的に重畳される。第1画素電極のモルフォロジーによって不均一な垂直電界発生が抑制されて表示装置、特に画素電極と共通電極との間に発生されたフリンジフィールドを使用するPLSモード方式の液晶表示装置の輝度分布を改善することができる。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

41 - 60 / 739

[ Back to top ]