Fターム[2H092MA10]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | 塗布 (728)

Fターム[2H092MA10]に分類される特許

21 - 40 / 728

半導体装置及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】ソース電極層又はドレイン電極層に接する第1の酸化物半導体層と、第1の酸化物半導体層上に設けられ第1の酸化物半導体層とは異なるエネルギーギャップを有する第2の酸化物半導体層と、を少なくとも含む酸化物半導体積層を用いてトランジスタを構成する。第1の酸化物半導体層と第2の酸化物半導体層とは互いに異なるエネルギーギャップを有すればよく、その積層順は問わない。

(もっと読む)

表示素子の製造方法、表示素子の製造装置、及び表示素子

【課題】高精度な駆動回路又は薄膜トランジスタを可撓性の基板に形成する表示素子用の製造装置を提供する。

【解決手段】表示素子の製造装置(100)は、可撓性の基板(FB)を第1方向に搬送する搬送部(RL)と、可撓性の基板に基準マークを形成するマーク形成部(10)と、可撓性の基板に隔壁を形成する隔壁形成部(10)と、基準マークに基づいて隔壁に対して所定の位置に導電部材を塗布する塗布部(20)と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを

目的の一つとする。

【解決手段】酸化物半導体層に対して、窒素、または希ガス(アルゴン、ヘリウムなど)

の不活性気体雰囲気下、或いは減圧下で脱水化、又は脱水素化処理のための加熱処理を行

い、酸素、酸素及び窒素、又は大気(好ましくは露点−40℃以下、より好ましくは−5

0℃以下)雰囲気下で加酸化処理のための冷却工程を行うことで高純度化及びI型化した

酸化物半導体層を形成する。該酸化物半導体層を含む薄膜トランジスタを有する半導体装

置を作製する。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

画素アレイ

【課題】TFTをそれぞれ有する複数の画素からなる画素アレイにおいて、画素の電気的特性に影響を及ぼすことなく、容易に高密度化することが可能な画素アレイを提供する。

【解決手段】複数の画素を有する画素アレイにおいて、隣接する所定数の画素にそれぞれ設けられたTFTは互いに近接配置され、該TFTの半導体膜は近接する複数のTFTに渡って連続して形成される。画素アレイは、同一の列に配列された複数の画素にそれぞれ設けられたTFTに接続され、該TFTに信号を供給、または該TFTから信号を読み出す列信号線と、複数の画素の隣接する行間に設けられ、TFTをオフ状態にしうる電圧信号が印加された行共通線と、を有する。半導体膜が連続して形成された複数のTFTのうち、行方向に近接配置される各TFTは、2本の列信号線を挟んで近接配置されており、列方向に近接配置される各TFTは、行共通線を挟んで近接配置されている。

(もっと読む)

表示装置およびその製造方法

【課題】外部の装置の外部コネクタに嵌合するコネクタ部の設計の自由度を高めることが可能な表示装置を提供する。

【解決手段】フレキシブル基板と、当該フレキシブル基板に設定される回路配置領域に設けられる内部回路と、外部の装置から前記内部回路に供給される電気信号により駆動される表示体とを備える表示装置であって、前記フレキシブル基板は、回路配置領域から延在するはみ出し領域を有し、前記フレキシブル基板の前記はみ出し領域には、前記内部回路から当該はみ出し領域の端部にまで延在し、外部の装置に接続される接続用配線が形成され、はみ出し領域の端部には、前記外部の装置の2種類以上の外部コネクタに嵌合するコネクタ部がそれぞれ設けられ、前記コネクタ部は、前記外部コネクタとの嵌合に必要な厚みを補う補強板が、前記フレキシブル基板の前記はみ出し領域の端部に貼合されて構成される、表示装置に関する。

(もっと読む)

アクティブマトリクス基板

【課題】本発明は、アクティブマトリクス基板にマトリクス状に配列された各々の有機半導体トランジスタの形成面積が小さく、かつ表示装置に用いた場合に均一で視認性に優れた画像表示を行うことを可能とするアクティブマトリクス基板を提供することを主目的とする。

【解決手段】樹脂製基材と、上記樹脂製基材上に形成され、ゲート電極、ソース電極、ドレイン電極、および有機半導体材料を含む有機半導体層を備える有機半導体トランジスタとを有し、上記有機半導体トランジスタがマトリクス状に複数配列されているアクティブマトリクス基板であって、隣接する2つの上記有機半導体トランジスタが、1つの上記有機半導体層のみを共有していることを特徴とするアクティブマトリクス基板を提供することにより上記課題を解決する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】少なくとも微結晶半導体領域及び非晶質半導体領域が積層する半導体膜を有する逆スタガ型の薄膜トランジスタにおいて、半導体膜上に導電膜及びエッチング保護膜を積層形成し、エッチング保護膜上にマスクを形成し、エッチング保護膜、導電膜及び非晶質半導体領域の一部をエッチングする第1のエッチング処理の後、マスクを除去する。次に、上記エッチングされたエッチング保護膜をマスクとして、露出した非晶質半導体領域及び微結晶半導体領域の一部をドライエッチングする第2のエッチング処理により、微結晶半導体領域の一部を露出させ、バックチャネル領域を形成する。

(もっと読む)

コンタクト構造

【課題】液晶パネルなどにおいて、取り出し端子とFPCを接続するための異方性導電膜のコンタクトの信頼性を向上する。

【解決手段】アクティブマトリクス基板101上の接続配線183は端子部182において異方性導電膜195によって、FPC191に電気的に接続される。接続配線183はアクティブマトリクス基板101上のTFTのソース/ドレイン配線と同じ工程で作製され、金属膜と透明導電膜の積層膜でなる。異方性導電膜195との接続部分において、接続配線183の金属膜の側面は保護膜で覆われているためこの部分において、金属膜は透明導電膜、下地の絶縁膜109、保護膜に接して囲まれ外気に触れることがない。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

液晶表示装置

【課題】段差部にて、絶縁膜の両側に形成される電極同士が短絡する恐れのない液晶表示装置を提供する。

【解決手段】第1の基板は、アクティブ素子と、前記アクティブ素子よりも上層に形成された第1の絶縁膜と、前記第1の絶縁膜よりも上層に設けられた第1の電極と、前記第1の電極よりも上層に設けられた第2の絶縁膜と、前記第2の絶縁膜よりも上層に設けられた第2の電極とを有し、前記第1の絶縁膜は、第1のコンタクトホールを有し、前記第2の絶縁膜は、前記第1の電極と前記第2の電極との間と、前記第1のコンタクトホール内とに一体的に形成されており、前記第1のコンタクトホール内の前記第2の絶縁膜には、第2のコンタクトホールが形成されており、前記第2の絶縁膜は、第1の膜厚で形成した後、前記第2の電極を形成する前に前記第1の膜厚よりも薄い第2の膜厚まで薄膜化されて形成される。

(もっと読む)

液晶表示装置

【課題】層数を減らしたIPS方式の液晶表示装置において、画素電極パターニング時の現像液によって、映像信号線が断線することを防止する。

【解決手段】ゲート絶縁膜102の上に映像信号線20および画素電極106を形成するITOが存在している。ITOにはピンホールが存在している。ITOのパターニングのためのレジスト200は、画素電極パターンとともに、映像信号線を覆うように形成する。映像信号線を覆ってレジストが形成されているので、レジスト現像時の現像液によって、映像信号線が侵されて、映像信号線が断線することを防止することが出来る。その後、ITOをエッチングする。ITOは、画素電極部分と、映像信号線を、上面および側面を覆った形で存在する。よって、ITOパターニング時の現像液による映像信号線の断線を防止することが出来る。

(もっと読む)

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

【課題】画素電極の電圧が保持され、画質が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基材110上で半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記チャネル領域を制御するゲート電極140と、前記ドレイン電極130と接続され液晶材料を駆動する画素電極190と、を複数有するアクティブマトリクス基板において、複数の前記画素電極190の間の空間に配された無機絶縁膜195と、前記画素電極190とは接触せずに、前記無機絶縁膜195と接触するようにして配された遮光膜200と、を有することを特徴とする。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】シフトレジスタなどに用いられる新規な回路を提供する。

【解決手段】基本構成は、第1のトランジスタ〜第4のトランジスタと、第1の配線〜第

4の配線を有する。第1の配線には電源電位VDDが供給され、第2の配線には電源電位

VSSが供給されている。第3の配線、第4の配線には2値の値を持つデジタル信号が供

給される。このデジタル信号は、高レベルのときには電源電位VDDと同電位となり、低

レベルのときには電源電位VSSと同電位である。第3の配線と第4の配線の電位の組み

合わせは4とおりあるが、第1のトランジスタ〜第4トランジスタは、いずれかの電位の

組み合わせによりオフさせることができる。つまり、定常的にオン状態となるトランジス

タがないため、トランジスタの特性劣化が抑制することができる。

(もっと読む)

部材の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

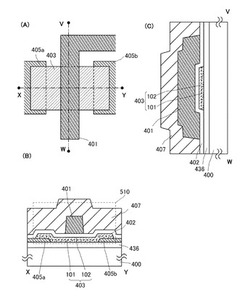

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

21 - 40 / 728

[ Back to top ]