Fターム[4G077AB01]の内容

結晶、結晶のための後処理 (61,211) | 結晶自体の特徴 (2,433) | 不純物濃度、キャリア濃度、転位濃度の特定 (795)

Fターム[4G077AB01]に分類される特許

41 - 60 / 795

炭素ドープシリコン単結晶の製造方法

【課題】炭素ドープシリコン単結晶の引き上げ時の有転位化を効果的に抑制して、歩留まりを向上させることができる炭素ドープシリコン単結晶の製造方法を提供することを目的とする。

【解決手段】炭素を添加したシリコン融液からシリコン単結晶を引き上げる炭素ドープシリコン単結晶の製造方法であって、前記シリコン単結晶の引き上げにおいて、シリコンの融点から1400℃の間の引き上げ軸方向の結晶温度勾配の平均値をG[℃/mm]で表した時、少なくとも固化率が20%までは、Gの値が1.0〜3.5[℃/mm]で、かつ、前記シリコン単結晶の成長中の固液界面の径方向面内中心部のSrcs値(von Mises相当応力[Pa]を、結晶温度1400℃におけるCRSS(Critical Resolved Shear Stress)[Pa]で割った値)が0.9以下になるようにシリコン単結晶を引き上げる炭素ドープシリコン単結晶の製造方法。

(もっと読む)

III族窒化物半導体結晶の製造方法、及び該製造方法により製造されるIII族窒化物半導体結晶

【課題】非極性面や半極性面の主面を有する結晶成長において、結晶成長に伴う積層欠陥を抑制し、かつ結晶面がc軸方向に反ってしまう結晶の反りを抑制することを課題とする。

【解決手段】結晶成長工程において、結晶表面に洗濯岩状の形状を呈するように結晶成長させることで、課題を解決する。具体的には、結晶表面に複数の凹部及び凸部を形成させ、且つ隣り合う前記凹部及び凸部の成長方向高さの差が500μm以上である箇所を連続して2以上形成させることで課題を解決する。

(もっと読む)

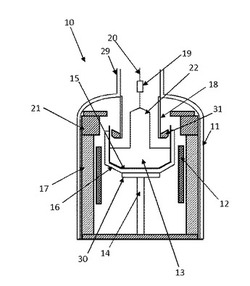

表面波プラズマCVD装置及びそれを用いて積層体を製造する方法

【課題】高い透明度を保持し、屈折率が高く、複屈折性が小さいという光学的な特性を有し、電気的絶縁性に優れ、各種基材に密着性良くコーティングでき、かつ低温での形成が可能な炭素膜を提供するプラズマCVD装置を提供すること。

【解決手段】本発明のプラズマCVD装置は、結晶欠陥が、六方晶ダイヤモンド及び積層欠陥を備える積層体を製造するための表面波プラズマCVD装置であり、前記表面波プラズマCVD装置は、試料台と、試料台上の冷却ステージと、表面波プラズマ源とを備え、該表面波プラズマ源を制御して反応器内のガス圧力を5×101から5×102Paに設定し、かつ試料台と冷却ステージと密着させ、前記基板と該表面波プラズマ源との距離を調節して基板温度を450℃以下に設定する。

(もっと読む)

III族窒化物半導体単結晶の製造方法

【課題】非極性面及び半極性面を主面とした結晶成長において、多結晶が発生することにより生じる、結晶の厚膜成長阻害を防ぐことを課題とする。

【解決手段】III族窒化物結晶からなり非極性面又は半極性面を主面とする下地基板上に、III族窒化物半導体結晶を成長させるIII族窒化物半導体結晶の製造方法において、前記主面からc軸方向に±90°傾斜した面をK面と定義したとき、該K面に対して特定の角度の面を有する側面を持った下地基板を用いることで多結晶発生の問題を解決する。

(もっと読む)

ドープされた窒化アルミニウム結晶及びそれを製造する方法

【課題】高濃度のドーパントを含有し、高い導電率及び移動度を有し且つ大きなスケールのAlN又はAlGaN結晶を製造する方法を提供する。

【解決手段】複数の不純物種を含む混晶を形成し、その混晶の少なくとも一部中において、1つの不純物種を電気的に活性化させる。混晶の形成には、多結晶ソースを用いた昇華−再凝縮法を利用する。その際、複数の不純物種を含むソース化合物を多結晶ソースに含有させるか、又はソース化合物のガス前駆体を蒸気混合物に導入することによって行う。

(もっと読む)

シリコン単結晶インゴット

【課題】 結晶軸方向で結晶品質の変化を抑制する。

【解決手段】窒素がドープされたシリコン融液12から引上げられ、横断面の少なくとも中央に空孔型点欠陥が発生する領域を有し、ボトム側インゴットの外径がトップ側インゴットの外径より大きいシリコン単結晶インゴット。

(もっと読む)

半導体多結晶ダイヤモンドおよびその製造方法

【課題】温度の計測が可能となる特性を有する半導体多結晶ダイヤモンドおよびその製造方法を提供する。

【解決手段】半導体多結晶ダイヤモンドは、平均粒径が10nm以上200nm以下のダイヤモンド結晶粒と、5×1014/cm3以上5×1019/cm3以下の硼素および不可避不純物とで構成され、温度が上昇した際に電気抵抗が減少する特性を有するように硼素をダイヤモンド結晶粒中に分散させる。該半導体多結晶ダイヤモンドは、気相合成で作製され硼素を5×1014/cm3以上5×1019/cm3以下含むグラファイトを、1200℃以上2500℃以下の温度、7GPa以上25GPa以下の圧力で直接ダイヤモンドに変換することで得られる。

(もっと読む)

シリコンウェーハの製造方法

【課題】シリコン単結晶インゴットの育成効率を低下させることなく、熱処理装置の大型化、煩雑化を防止し、かつ、熱処理時におけるスリップ転位の発生や不純物汚染を抑制することができ、ウェーハの表層部及びバルク部においてもCOPやBMD等の欠陥を低減させることができるシリコンウェーハの製造方法を提供する。

【解決手段】CZ法によりV−リッチ領域からなる酸素濃度が0.8×1018atoms/cm3(old−ASTM)以下であるシリコン単結晶インゴットを育成する工程と、インゴットを切断してV−リッチ領域からなるスライスウェーハを得る工程と、スライスウェーハの表裏面を平坦化処理し、更にエッチング処理する工程と、エッチング後のウェーハを、熱処理用部材を用いて枚葉で単数又は複数保持して酸化性ガス雰囲気中、1150℃以上1200℃以下の最高到達温度で5分以上10時間以下熱処理する工程と、酸化膜を除去する工程と、少なくとも半導体デバイス形成面となる表面を鏡面研磨する工程と、を備える

(もっと読む)

多結晶ダイヤモンドおよびその製造方法

【課題】熱伝導率の優れた多結晶ダイヤモンドおよびその製造方法を提供する。

【解決手段】ナノ多結晶ダイヤモンド1は、12Cあるいは13Cのいずれかの炭素同位体で実質的に構成された炭素と、炭素以外の複数の不純物とで構成され、複数の不純物の濃度がそれぞれ0.01質量%以下であり、結晶粒径が500nm以下である。上記ナノ多結晶ダイヤモンド1は、12Cあるいは13Cの炭素同位体の純度が99.9質量%以上である炭化水素ガスを熱分解して得られる黒鉛に、高圧プレス装置内で熱処理を施してダイヤモンドに変換することで作製可能である。

(もっと読む)

単結晶基板およびそれを用いた半導体素子

【課題】 耐電圧特性を向上させることが可能な単結晶基板を提供する。

【解決手段】 本発明の単結晶基板は、炭化ケイ素の単結晶からなり、イットリウム、ジルコニウム、マグネシウムおよびカルシウムのうち少なくとも1つを微量添加物として含む。このような微量添加物を含んでいることから、耐電圧特性を向上させることができる。

また、本発明の半導体素子は、上記の単結晶基板1と、単結晶基板1上に設けられた、炭化ケイ素からなるp型半導体層3と、単結晶基板1に設けられた第1電極4と、p型半導体層3に設けられた第2電極5とを有する。

(もっと読む)

窒素ドープ酸化亜鉛系薄膜の製造方法

【課題】表面平坦性に優れ、かつ高濃度の窒素ドーピングを実現できるZnO系薄膜を作製する方法を提供する。

【解決手段】主面の法線が結晶軸から傾斜した酸化亜鉛系基板1上に、窒素ドープ酸化亜鉛系薄膜2を形成するにあたって、少なくとも亜鉛と酸素と窒素を原料ガスとして使用し、これらを750〜900℃の温度条件で基板1に接触させて、基板1表面に、窒素をドープした酸化亜鉛系材料からなる結晶を成長させて窒素ドープ酸化亜鉛系薄膜2を形成する。原料ガスとしての酸素供給量に対する亜鉛供給量は、窒素ドープ酸化亜鉛系薄膜の亜鉛と酸素のモル比(亜鉛/酸素)が1より大きくなるようにされる。原料ガスとしての窒素は、窒素ガスを高周波で励起することによって発生させた窒素ラジカルを含む。

(もっと読む)

SiCエピタキシャルウェハ及びその製造方法、並びにSiCエピタキシャルウェハの製造装置

【課題】チャンバ内の部材の材料片を起点とする三角欠陥の面密度が低いSiCエピタキシャルウェハ及びその製造方法、並びにSiCエピタキシャルウェハの製造装置を提供する。

【解決手段】本発明のSiCエピタキシャルウェハは、オフ角を有するSiC単結晶基板上にSiCエピタキシャル層を有するSiCエピタキシャルウェハであって、前記SiCエピタキシャル層に存在する、チャンバ内の部材の材料片を起点とする三角欠陥の面密度が0.5個/cm2以下であることを特徴とする。

(もっと読む)

軸オフの種結晶上での100ミリメートル炭化ケイ素結晶の成長

【課題】 軸オフのウェーハを得るための従来技術において、より大きな結晶は、一般に結晶の垂線から離れて配向され、ついで軸オフの種結晶を産生するためにウェーハが配向方向に向かって切断される。垂線から離れて結晶を配向することは、結晶と同じサイズのウェーハを切断するために利用可能な有効な層厚を低減する。

【解決手段】 半導体結晶および関連する成長方法が開示される。結晶は、種結晶部分と、種結晶部分上の成長部分とを含んでいる。種結晶部分および成長部分は、実質的に直立した円筒形の炭化ケイ素の単結晶を形成する。種結晶面は、成長部分と種結晶部分との間の界面を規定し、種結晶面は、直立した円筒形の結晶の基部に実質的に平行であり、単結晶の基底平面に関して軸オフである。成長部分は、種結晶部分のポリタイプを複製し、成長部分は、少なくとも約100mmの直径を有する。

(もっと読む)

エピタキシャルウエハ及び半導体素子

【課題】エピタキシャル成長層の結晶品質を向上させることができ、厚膜のエピタキシャル成長層を形成する場合においてもキャリア移動度の低下が生じず、素子抵抗の低い炭化珪素エピタキシャルウエハおよび炭化珪素半導体素子を提供する。

【解決手段】炭化珪素半導体素子は、ドーピングにより格子定数が減少するドーパントを濃度Aでドーピングした基板と、ドーパントを基板よりも小さい濃度Bでドーピングしたエピタキシャル成長層と、基板とエピタキシャル層との間に、ドーパントをドーピングした2層以上積層した多層構造で形成されたバッファ層とを有し、多層構造の各層のドーパントのドーピング濃度Cが、バッファ層の厚さをd、エピタキシャル成長層からの各層までの平均距離をx、所定の割合をPとして、[B+(A−B)×x/d]×(1−P)≦C≦[B+(A−B)×x/d]×(1+P)とした。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

低マイクロパイプの100mm炭化ケイ素ウェハ

【課題】種結晶を用いた昇華システムにおいて形成された結晶の欠陥レベルが低く、より大きく、高品質のSiC単結晶ウェハを製造する方法を提供する。

【解決手段】少なくとも約100mmの直径と、約25cm−2未満のマイクロパイプ密度とを有し、また、3C、4H、6H、2Hおよび15Rポリタイプからなる群から選択されるポリタイプを有するSiC単結晶ウェハ。なお、マイクロパイプ密度は、表面上にある全マイクロパイプの総数を、ウェハの表面積で割ったものを表す。

(もっと読む)

窒化物半導体エピタキシャル基板及び窒化物半導体デバイス

【課題】低転位であり、クラック発生を抑制できるIII族窒化物半導体層を有する窒化物

半導体エピタキシャル基板及び窒化物半導体デバイスを提供する。

【解決手段】基板上にAlを含むIII族窒化物半導体のバッファ層を介して成長した、C

面を表面とするIII族窒化物半導体層を有する窒化物半導体エピタキシャル基板であって

、前記バッファ層が、その表面にインバージョンドメインを有する。

(もっと読む)

SiCエピタキシャル基板およびその製造方法

【課題】 低オフ角のSiC基板上においても、エピタキシャル層表面の三角欠陥およびステップバンチングの発生を抑制できるSiCエピタキシャル基板の製造方法およびそれによって得られるSiCエピタキシャル基板を提供する。

【解決手段】エピタキシャル成長シーケンスが、SiC基板21上に、第1の温度で第1のエピタキシャル層22を成長させるステップと、前記第1の温度よりも低温の第2の温度で第2のエピタキシャル層23を成長させるステップとを含む。

(もっと読む)

シリコン基板の製造方法およびシリコン基板

【課題】酸素濃度を低減させたシリコン基板を製造するシリコン基板の製造方法を提供する。

【解決手段】チョクラルスキー法により製造されたシリコン単結晶体から切り出されたシリコン基板のデバイス形成予定領域部分を厚さ50〜200μmに加工し、温度T(℃)、時間t(秒)、初期酸素濃度Oi(原子個/cm3)としたとき、t=f(Oi)2(Tsi/200)2/{[0.52exp[−2.94×104/(273+T)]} (ただし式中、f(Oi)=1.43×10−69Oi4−3.35×10−51Oi3+2.51×10−33Oi2−3.99×10−16Oi−83.43である)で与えられる温度T(℃)以上の温度で、時間t(秒)以上の時間アニールする。

(もっと読む)

窒化物結晶の製造方法及び窒化物結晶

【課題】酸素などの不純物濃度が低い窒化物半導体結晶を速い成長速度で製造する方法を提供する。

【解決手段】反応容器内で超臨界および/または亜臨界状態の溶媒3存在下にて窒化物半導体結晶2の成長を行う際に、鉱化剤としてハロゲン化亜鉛を使用する。なお、ハロゲン化亜鉛以外の化合物であるハロゲン原子、アルカリ金属、アルカリ土類金属、または希土類金属を含む化合物を併用してもよい。また、反応容器は、白金族又は白金族を含む合金からなるカプセルである。

(もっと読む)

41 - 60 / 795

[ Back to top ]