Fターム[4M104AA10]の内容

Fターム[4M104AA10]に分類される特許

81 - 100 / 956

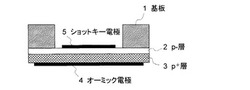

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】半絶縁性単結晶ダイヤモンド基板の一方の面に、p−ダイヤモンド層からなるドリフト層を成膜し、該ドリフト層の上にp+ダイヤモンド層からなるコンタクト層を成膜する工程と、前記基板の他方の面に開口部をエッチングにより形成して、前記基板を構造保持材として前記ドリフト層の一部が露出した露出部を形成する工程と、前記露出部にカソード電極を設け、前記コンタクト層にアノード電極を設ける工程とにより、ダイヤモンド電子素子の積層構造を形成する。ドリフト層を基板上に直接成膜するので、欠陥密度の減少した素子を得ることができる。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】ダイヤモンド半導体からなるドリフト層と、半絶縁性ダイヤモンド層を有する構造保持材と、ダイヤモンド半導体からなるコンタクト層とを備えるダイヤモンド電子素子であって、前記構造保持材は、開口部を有し、前記ドリフト層の一方の面に積層されており、前記コンタクト層は、前記開口部内において、前記ドリフト層に直接積層されており、また、アノード電極は、前記開口部内の前記コンタクト層に設け、カソード電極は前記ドリフト層の他方の面に設けて、例えば、ショットキーバリアダイオードを実現する。単結晶ダイヤモンド基板の一方の基板面に欠陥層を形成した後、該基板面上に前記ドリフト層を成膜し、半絶縁性ダイヤモンド層を選択的に成長させて開口部を有する構造保持材を形成した後、前記基板はスマートカット法により素子部より分離する。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

有機半導体素子の製造方法および該製造方法によって得られる有機半導体素子

【課題】 本発明の目的は、電気特性の安定性に優れた有機半導体素子の製造方法と、有機半導体素子を提供することである。

【解決手段】上記課題は、ゲート電極形成工程と、ゲート絶縁膜形成工程と、ソース/ドレイン電極形成工程と、有機半導体膜形成工程と、有機半導体膜上に保護膜を形成する工程とを含み、前記有機半導体膜上に保護膜を形成する工程において、(a)炭酸プロピレン、アセトニトリル、ジメチルスルホキシドから選ばれる少なくとも1つの有機溶剤と、(b)有機溶剤(a)に可溶な有機化合物とを含有する保護膜形成液を用いて、ウェットプロセスにより前記保護膜を形成することを特徴とする有機半導体素子の製造方法により達成される。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】 ウェット法により電極を形成した場合においても、マイグレーションによる不具合が起きず、配線抵抗も十分小さく、かつトランジスタ特性の優れた薄膜トランジスタを提供すること。

【解決手段】 基板10上にゲート電極、ゲート絶縁膜、ソース電極及びドレイン電極、有機半導体層を有する薄膜トランジスタにおいて、前記ソース電極及び前記ドレイン電極が3層の積層体からなり、かつ3層の積層体の膜厚が第1層目、第2層目、第3層目の順に薄くする薄膜トランジスタである。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 複合酸化物の単結晶をチャンネルに用いたFETに電界効果のみで1013cm-2以上の高濃度のキャリアを注入することと、キャリアの移動度が室温でも10cm2/Vsに達するほどに理想的なチャンネルとの界面を得ることを共に可能にするゲート絶縁膜を有する電界効果トランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 チャンネル層を構成するペロブスカイト構造の複合酸化物単結晶基板と、該複合酸化物単結晶基板上にパラキシリレンのポリマー膜及び酸化タンタルがこの順に積層された積層構造からなるゲート絶縁膜とを有する電界効果トランジスタ。

(もっと読む)

薄膜トランジスタの製造方法および薄膜トランジスタ

【課題】UV露光でも電気的絶縁性が損なわれず、表面濡れ性の変化を利用して印刷法でソース・ドレイン電極のパターニングが可能なゲート絶縁層を有する薄膜トランジスタの製造方法を提供する。

【解決手段】基板7上にゲート電極42およびゲート絶縁層2が順次形成され、該ゲート絶縁層が形成されたゲート電極上に適宜の間隔でソース電極5aおよびドレイン電極5bが対向配置され、該間隔を含む領域に半導体層6が形成された薄膜トランジスタを、活性水素基と反応可能なメラミン誘導体および活性水素基を有する樹脂を含有する溶液を塗布・焼成し、紫外線照射で表面濡れ性が可変のゲート絶縁層を形成し、紫外線照射で該ゲート絶縁層の露光部位を親水性域に変え、親水性域に電極材料含有溶液を印刷法で塗布・乾燥し、ソース電極及びドレイン電極を形成して薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

成膜方法、半導体装置及びその製造方法、並びに基板処理装置

【課題】真空装置を使用せずに、トランジスタ等の半導体装置に適用できるMOS構造の積層膜を形成する。

【解決手段】成膜方法は、半導体膜3を有する基板に、ポリシラン溶液を塗布し、半導体膜3上にポリシラン膜5を形成する工程(STEP1)と、ポリシラン膜5上に、金属塩溶液を塗布し、金属イオン含有膜7を形成することにより、ポリシラン膜5をポリシロキサン膜5Aへ、金属イオン含有膜7を金属微粒子含有膜7Aへ、それぞれ改質する工程(STEP2)を備え、MOS構造の積層膜100を形成する。

(もっと読む)

電子デバイス、電子デバイス製造方法、電子デバイス製造装置、電界効果トランジスタデバイス、有機電界発光素子及び制御方法

【課題】低仕事関数金属の使用や不純物ドーピングなしで伝導特性を制御し得る電子デバイスを提供することを目的とする。

【解決手段】本発明による電子デバイスは、電極層と半導体層とが吸着した吸着部を有する電子デバイスであって、前記吸着部において、前記電極層の原子表面と前記半導体層の原子表面との距離は、前記電極層の前記原子表面と前記半導体層の前記原子表面とが安定して吸着する安定吸着距離より短い。前記吸着部への加重によって、前記距離を前記安定吸着距離より短くする加重部を有する。

(もっと読む)

有機薄膜トランジスタ及びこれを備えた平板表示装置

【課題】有機薄膜トランジスタ及びこれを備えた平板表示装置を提供する。

【解決手段】基板の一面上に形成されるソース/ドレイン電極及び有機半導体層と、ソース/ドレイン電極及び有機半導体層と絶縁されるゲート電極と、ソース/ドレイン電極と前記ゲート電極との間に一層以上のゲート絶縁層と、を備え、ソース/ドレイン電極と前記ゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さは、有機半導体層のチャンネル領域とゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さ以上とした。

(もっと読む)

有機薄膜トランジスタ及びその製造方法

【課題】大気雰囲気下であっても酸化されにくく、機能的にも劣化しにくい電荷注入層を備えた有機薄膜トランジスタを提供する。

【解決手段】ゲート電極20Aと、第1のソース/ドレイン電極60Aと、第2のソース/ドレイン電極60Bと、前記第1および第2のソース/ドレイン電極と前記ゲート電極との間に設けられる有機半導体層40と、前記第1および第2のソース/ドレイン電極と前記有機半導体層の間において、前記第1および第2のソース/ドレイン電極に接して配置される電荷注入層50とを備える有機薄膜トランジスタ10において、前記電荷注入層は、電荷注入特性を有するイオン性ポリマーを含有する、有機薄膜トランジスタ。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

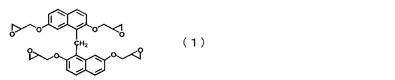

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】電圧−電流特性を改善した整流素子を用いたメモリセルを有する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の配線と、前記第1の配線に交差する第2の配線と、前記第1及び第2の配線に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子及び非オーミック素子を直列接続してなるメモリセルとを備え、前記非オーミック素子は、メタル層と、前記メタル層に接合された真性半導体層と、前記真性半導体層に接合された第1の不純物を含む不純物半導体層とを有することを特徴とする。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

感光性塗布型電極材料を用いたTFTの製造方法

【課題】従来の電極方法であるフォトリソグラフィ、マスクスパッタリングは、工程の簡略化、材料使用効率、コスト、多様な基板サイズに対応において解決するには困難な課題があり、インクジェット方式では高精細度なパターンが得られないという課題がある。

【解決手段】感光性塗布型電極材料を用いて、所望の電極パターンニングを行う。本発明による電極作成工程において、コストメリットがある拡散光を光源とするランプを用いて第1の露光と第1の露光よりも大きい露光量をもった第2の露光を施すことで、所望の電極パターンを得ることができる。拡散光を用いた2回露光プロセスによって、例えばTFT作成において従来の方法では解決できない材料使用効率、コスト、多様な基板サイズに対応という課題かつ、インクジェット方式では解決できない高精細パターニングを解決するものである。

(もっと読む)

81 - 100 / 956

[ Back to top ]