Fターム[4M104AA10]の内容

Fターム[4M104AA10]に分類される特許

141 - 160 / 956

電極構造体の製造方法および太陽電池

【課題】スパッタリングを利用した場合でも、電極構造体に、微細な凹凸構造を欠点なく正確に、かつ簡便に形成することのできる電極構造体の製造方法、ならびに電極構造体に欠点のない微細な凹凸構造が正確に形成されてなる太陽電池を提供する。

【解決手段】表面に微細な凹凸構造を有するスタンパー1の表面上に、導電体層2を剥離可能に形成し、スタンパー1上の導電体層2と、硬化性材料4とを接触させ、その状態で硬化性材料4を硬化させて、微細な凹凸構造を有する凹凸基層5を形成するとともに、凹凸基層5と導電体層2とを接着し、スタンパー1と、凹凸基層5に接着された導電体層2とを分離し、もって凹凸基層5上に導電体層2を転写して形成し、このようにして、微細な凹凸構造を有する電極構造体10を製造する。

(もっと読む)

p型有機薄膜トランジスタ、p型有機薄膜トランジスタの製造方法、および、塗布溶液

【課題】電荷注入効率の高いp型有機薄膜トランジスタ、および、金属酸化物を電荷注入層として用いても、金属酸化物が溶解することで電極剥離を起こすことのないp型有機薄膜トランジスタの製造方法、ならびに、この製造方法に用いる塗布溶液を提供する。

【解決手段】p型有機薄膜トランジスタ10Aは、絶縁基板11上に設けられたゲート電極12と、ゲート電極12を被覆して設けられたゲート絶縁層13と、ゲート絶縁層13上に設けられたソース電極14aおよびドレイン電極14bと、ソース電極14aおよびドレイン電極14bの表面に設けられた金属酸化物層15と、ゲート絶縁層13上、かつ金属酸化物層15が形成されたソース電極14aとドレイン電極14bとの間に設けられたp型有機半導体層16と、を備えたことを特徴とする。

(もっと読む)

グラフェン膜と金属電極とが電気的接合した回路装置

【課題】グラフェン膜と金属電極との間の接触抵抗を低減してグラフェン膜と金属電極とが良好に電気的接合された回路装置を提供する。

【解決手段】本発明に係るグラフェン膜と金属電極とが電気的接合した回路装置は、単層または複数層からなるグラフェン膜を利用した回路装置であって、前記グラフェン膜と直接接触する下地層としての酸化アルミニウム膜が前記グラフェン膜の下部のみに形成されており、前記酸化アルミニウム膜の組成がAl2-xO3+x(x ≧ 0)であり、前記グラフェン膜と金属電極とが直接接合し、該接合箇所には凹凸構造が形成され、前記凹凸構造は、前記酸化アルミニウム膜に形成された少なくとも1つのコーン状凹部と、前記コーン状凹部を含む前記酸化アルミニウム膜の表面に沿って該表面と平行に成長した前記グラフェン膜と、前記グラフェン膜を覆いかつ前記コーン状凹部を埋めるように形成された前記金属層とから構成されていることを特徴とする。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた高耐圧半導体整流装置を提供する。

【解決手段】第1導電型のワイドバンドギャップ半導体基板と、ワイドバンドギャップ半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが20μm以上の第1導電型のワイドバンドギャップ半導体層と、ワイドバンドギャップ半導体層表面に形成される第1導電型の第1のワイドバンドギャップ半導体領域と、第1のワイドバンドギャップ半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域と、第1および第2のワイドバンドギャップ半導体領域上に形成される第1の電極と、ワイドバンドギャップ半導体基板の下面に形成される第2の電極と、を備え、第2のワイドバンドギャップ半導体領域の幅が15μm以上であることを特徴とする半導体整流装置。

(もっと読む)

裏面オーミックコンタクトを備えた縦型の半導体デバイス

【課題】オーミックコンタクトを有する半導体デバイスを、経済的に製造できるようにする。

【解決手段】半導体デバイス10は、半導体基板12と、該半導体基板の表面上にあり、半導体基板の解離温度未満の解離温度を有するエピタキシャル層14と、半導体基板内に形成された漸増キャリヤー濃度帯16と、金属層18とから構成される。漸増キャリヤー濃度帯は、約1000Åの厚さを有し、エピタキシャル層と反対の半導体基板の表面から該表面と反対側の表面に向かって伸びており、該反対側の表面に向かってドーパントの濃度が漸次低下している。金属層は、漸増キャリヤー濃度帯との境界20においてオーミックコンタクトを形成する。

(もっと読む)

電気光学装置用基板及びその製造方法、電気光学装置並びに電子機器

【課題】電気光学装置用基板において、製造コストを低減すると共に、アライメント精度を高める。

【解決手段】電気光学装置用基板は、基板上に設けられた第1の絶縁膜(310)と、複数の画素(20)と、複数の画素にわたって第1の絶縁膜に設けられた第1の凹部と、第1の凹部の底面に設けられた第2の凹部と、第2の凹部に設けられた有機半導体層(241)と、該有機半導体層の上に設けられたゲート絶縁膜(245)と、該ゲート絶縁膜の上に設けられたゲート電極と、を含み、複数の画素のうち一の画素に対応づけられた薄膜トランジスタ(24)と、ゲート絶縁膜の上層であって、複数の画素にわたって第1の凹部に設けられた走査線(40)と、薄膜トランジスタと電気的に接続されたデータ線(50)と、を備える。

(もっと読む)

整流素子

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子を提供する。

【解決手段】ショットキー電極3は、SiCよりなるn-半導体層2とショットキー接触し、かつSiCよりなるp型半導体層5a,5bと電気的に接続している。ショットキー電極3とカソード電極4との電位差が変化することにより、ショットキー電極3とカソード電極4との間に電流を流す状態と、p型半導体層5a,5bに囲まれるn-半導体層2を空乏層化させてショットキー電極3とカソード電極4との間の電流経路を遮断する状態とを選択可能である。n-半導体層2とショットキー電極3との間のショットキー障壁φBn1が、0.68eV<φBn1<1.05eVであり、かつ250℃の温度でも、そのショットキー接触を確保できる。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

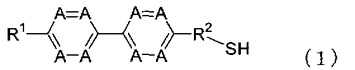

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な、酸化物半導体を用いた薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極およびゲート絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられた金属酸化物膜と、金属酸化物膜上に設けられた金属膜と、を有し、酸化物半導体膜は、金属酸化物膜と接し、且つ、酸化物半導体膜の他の領域よりも金属濃度が高い領域(金属高濃度領域)を有する。金属高濃度領域には、酸化物半導体膜に含まれる金属が、結晶粒または微結晶として存在していてもよい。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

スパッタリングターゲット及びその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われる回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置とする。

(もっと読む)

半導体装置、集積回路、マトリックス回路、表示素子、無線通信装置、電子機器、半導体装置の製造方法

【課題】エッチングによりソース・ドレイン電極を形成しても、有機半導体層が損傷を受けることなく、良好なオン/オフ比を示す有機半導体装置、及びその製造方法を提供することを目的とする。

【解決手段】基板1と、前記基板上に形成されたゲート電極2と、ゲート電極2及び基板1上に形成されたゲート絶縁層3と、ゲート絶縁層3上に形成されたp型有機半導体層4と、有機半導体層4上に形成された保護層5と、保護層5上に形成されたソース電極8及びドレイン電極9と、を有する半導体装置を構成する。

(もっと読む)

透明電極パターンの形成方法

【課題】表面荒れが少なく、光の透過率の高い透明電極パターンを容易に形成できる技術を提供する。

【解決手段】本発明の透明電極パターンの形成方法によれば、基材の一面に透明電極層を形成する透明電極層形成工程と、前記透明電極層の一部を覆い、前記透明電極層の他部を露出するようにパターニングされたマスクを形成するマスク形成工程と、前記マスクおよび前記透明電極層の表面に金属膜を成膜する金属膜成膜工程と、エッチングにより前記金属膜の一部を残し金属配線を形成し、前記マスクの一部と前記透明電極層の前記他部の一部を露出させる第1エッチング工程と、前記第1エッチング工程で露出した前記透明電極層を前記マスクの一部をマスクとしてエッチングすることにより透明電極のパターンを形成する第2エッチング工程と、を有する。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

半導体装置及び半導体装置を用いた表示装置

【課題】電極を精度良く形成できると共に、設計マージンを低減することが可能な構造の半導体装置を提供する。

【解決手段】薄膜トランジスタのゲート電極22と、このゲート電極22を覆って形成されたゲート絶縁膜23と、このゲート絶縁膜23上に形成され、薄膜トランジスタのソース領域、チャネル領域、ドレイン領域を構成する有機半導体層24と、この有機半導体層24上に形成された構造体31と、ゲート絶縁膜23上から構造体31よりも外側の有機半導体層24上にわたって形成された、薄膜トランジスタのソースドレイン電極25,26と、このソースドレイン電極25,26と同じ材料により、構造体31の上に形成された、電極材料層32とを含む半導体装置を構成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一とする。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層を薄いインジウム層または薄いインジウム合金層とする。なお、酸化物半導体層は、インジウムを含む。二層目以降のソース電極層またはドレイン電極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】酸化物半導体をチャネル形成領域に用いたトランジスタを有する半導体装置の作製において、酸化物半導体膜を形成した後、水分、ヒドロキシ基、または水素などを吸蔵或いは吸着することができる金属、金属化合物または合金を用いた導電膜を、絶縁膜を間に挟んで酸化物半導体膜と重なるように形成する。そして、該導電膜が露出した状態で加熱処理を行うことで、導電膜の表面や内部に吸着されている水分、酸素、水素などを取り除く活性化処理を行う。

(もっと読む)

141 - 160 / 956

[ Back to top ]