Fターム[4M104AA10]の内容

Fターム[4M104AA10]に分類される特許

201 - 220 / 956

グラフェンと金属電極との電気的接合デバイス、それを用いた電子デバイス,電子集積回路及び光/電子集積回路

【課題】グラフェンと金属電極との間の接触抵抗を低減する。

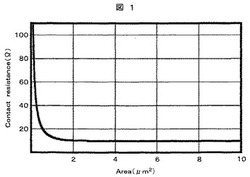

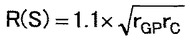

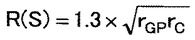

【解決手段】グラフェンの単位面積あたりの電気抵抗をrGP[Ω/μm2]、グラフェンと金属電極との単位面積当たりの界面抵抗をrC[Ωμm2]とすると、接触面積をSとして、接触抵抗は

と計算できる。rGPを10Ω/μm2、rCを10Ωμm2とした場合の計算結果を示し、接触面積を

にすることにより、接触抵抗を収束値の10%増し、あるいは30%増しの値にまで、低減することができる。

(もっと読む)

自己整合印刷

【課題】表面エネルギーパターンの手助けなしに印刷材料の第1および第2の領域を分離するマイクロメータおよびサブマイクロメータの寸法の臨界形状を形成することのできる方法を提供する。

【解決手段】 溶液処理および直接印刷によって導電性、半導体および/または絶縁性の層を蒸着する工程、および第2の材料の溶液をはじく第1のパターンの周りに表面エネルギー障壁を自己整合的に形成することによって電気活性ポリマーの高解像度パターンを形成する工程を含む、有機性または部分的に有機性のスイッチング装置を形成する方法。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

薄膜トランジスタおよび該薄膜トランジスタの製造方法

【課題】低温で簡便なプロセスにより形成可能で、移動度、on/off比に優れ、立ち上がり電圧のマイナス側へのシフト、S値劣化、素子間の性能バラツキを改良した、安定性の高い薄膜トランジスタ、および該薄膜トランジスタの製造方法を提供する。

【解決手段】基板106上にゲート電極104、ゲート絶縁層105、ソース電極102、ドレイン電極103、及び半導体層101を有する薄膜トランジスタにおいて、半導体層101が塗布によって形成された酸化物半導体からなり、フッ素化合物含有層107がゲート電極104と半導体層101との間に設けられる。

(もっと読む)

電子素子

【課題】簡便な方法で製造することができる電子素子を提供する。

【解決手段】第1の電極及び第2の電極を有し、該第1の電極と該第2の電極との間に有機材料を含む有機層を有し、該有機材料が該第1の電極又は該第2の電極と直接又は他の層を介して電子の授受を行う電子素子において、該第1の電極が金属又は金属の合金を含み、該金属又は金属の合金の融点が100℃以下であることを特徴とする電子素子。金属の合金がガリウムを含むことが好ましい。電子素子としては、有機エレクトロルミネッセンス素子、光電変換素子等が挙げられる。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】プロセス時間を増大させることなく、金属箔基板上に十分な絶縁性と平坦性が確保された絶縁膜を設けることが可能な半導体装置の製造方法を提供する。

【解決手段】金属箔基板5上に絶縁性のシート状樹脂1を貼り合わせ、貼り合わせたシート状樹脂1の上に半導体素子を形成する工程を行う。シート状樹脂1を貼り合わせた後、半導体素子を形成する前に、シート状樹脂1を硬化させる工程を行う。

(もっと読む)

積層構造体、電子素子、電子素子アレイ、画像表示媒体及び画像表示装置

【課題】表面自由エネルギーを変化させる際に照射する紫外線による濡れ性変化層の絶縁性の低下を抑制することが可能な積層構造体並びに該積層構造体を有する電子素子、電子素子アレイ、画像表示媒体及び画像表示装置を提供する。

【解決手段】積層構造体10は、基板11上に、紫外線を照射することにより表面自由エネルギーが変化する材料を含む濡れ性変化層12の紫外線照射領域12aに導電体層13が形成されている積層構造を有し、紫外線を照射することにより表面自由エネルギーが変化する材料は、ポリアミド酸を脱水閉環反応させることにより得られる有機溶媒に可溶な特定ポリイミドである。

(もっと読む)

半導体装置及びその製造方法

【課題】読み出しマージンの大きなSRAMセルを提供する。

【解決手段】第1インバータ回路と、出力ノードが前記第1インバータ回路の入力ノードに接続され、入力ノードが前記第1インバータ回路の出力ノードに接続された、第2インバータ回路と、ソース及びドレインの一方が前記第1インバータ回路の出力ノードに接続され、他方がビット線に接続された、第1アクセストランジスタとを具備する。前記第1インバータ回路は、第1トランジスタを含む。前記第1アクセストランジスタ及び前記第1トランジスタのそれぞれは、基板上に形成され、前記基板面に対して垂直に延びる半導体柱と、前記半導体柱を前記基板面に平行な方向で取り囲むように形成され、前記半導体柱にチャネル領域を形成させる、ゲート電極と、前記半導体柱の下端部又は上端部にそれぞれ接続されるソース及びドレインとを備える。前記第1トランジスタの電流駆動力は、前記第1アクセストランジスタのそれよりも高い。

(もっと読む)

薄膜トランジスタアレイの製造方法及び表示装置

【課題】ソース電極とドレイン電極を均一且つ効率的に製造でき、薄膜トランジスタの半導体特性を低下させない薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】基板1上にスキャンライン2を形成する工程と、外部接続用開口部11以外の領域に絶縁層2を形成する工程と、塗布型電極材料を全面に塗布、焼成して塗布電極層を形成した後にエッチングして少なくともソース電極4s及びドレイン電極4dを形成する工程と、ソース電極4s及びドレイン電極4dとを跨ぐ半導体層5を形成する工程と、封止層6を、外部接続用開口部11に露出しているスキャンライン2a上には少なくとも形成しないようにして形成する工程と、封止層6上に表示電極層8を形成した後にエッチングして表示電極8を形成する工程とを有する。この場合において、表示電極形成時のエッチングにより、外部接続用開口部11に露出しているスキャンライン2a上に残った余分な塗布電極層を除去する。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】生産性に優れたフレキシブル半導体装置を提供する。

【解決手段】可撓性を有するフレキシブル半導体装置100であり、樹脂フィルム30と、樹脂フィルム30の上に形成された金属層10とを備え、金属層10は、絶縁壁51によって分断され、且つ、絶縁壁51の一端53は樹脂フィルム30に接しており、絶縁壁51によって金属層10から、ゲート電極10g、ソース電極10sおよびドレイン電極10dが形成されている。ゲート電極10gの上には、絶縁壁51に接するゲート絶縁膜22が形成されており、ゲート絶縁膜22の上には半導体層20が形成されている。

(もっと読む)

透明導電膜のパターニング方法及び該方法による透明導電パターン膜

【課題】

透明導電膜の微細パターニングを可能とするリフトオフ法によるパターニング方法、及び該パターニング方法を用いて形成された透明導電パターン膜を提供する。

【解決手段】

基材上に有機溶媒可溶性でかつ水不溶性のフォトレジストパターンを形成するパターンレジスト形成工程、前記フォトレジストパターンが形成された基材上の全面に導電性酸化物微粒子と無機バインダーと溶媒とからなる透明導電膜形成用塗布液を塗布、乾燥、硬化して導電性酸化物微粒子と無機バインダーマトリックスを主成分とする透明導電膜を形成する透明導電膜形成工程、前記フォトレジストパターンを有機溶媒で溶解除去による現像をすることでフォトレジストパターン上に形成された透明導電膜を除去して透明導電パターン膜を得る透明導電膜パターニング工程を具備し、前記透明導電膜形成用塗布液の溶媒は、水又は水−アルコール混合溶液を主成分とすることを特徴とする。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

ダイヤモンド電極構造

【課題】 高温あるいは強反応性化学物質中においても金属、ダイヤモンド接合の品質を保持したまま、機能を発揮するダイヤモンド電極構造を提供する。

【解決手段】

ダイヤモンド表面にルテニウム(Ru)もしくは酸化ルテニウム(RuO2)からなる電極を設けることにより、電気的接合を行うことを特徴とするダイヤモンド電極構造。

(もっと読む)

有機薄膜トランジスタ、その作製方法、および、それに使用されるゲート絶縁層

【課題】アゾール−金属錯化合物をゲート絶縁層として使用される有機薄膜トランジスタの製造方法を提供する。

【解決手段】自己組織化ゲート絶縁層を作成する方法は、水性溶液中でパターン化ゲート電極上にアゾール−金属錯化合物が自己形成され且つゲート絶縁層の役割を果たすことを可能とする水性処理法。有機薄膜トランジスタ(OTFT)は上記ゲート絶縁層に使用される上記アゾール−金属錯化合物を含むことから、簡素で迅速かつ容易な様式で低コストにて大量に製造される。

(もっと読む)

有機トランジスタ用インク、有機トランジスタの電極及びその形成方法並びに有機トランジスタ

【課題】印刷性については版部材へのインキングが良好で、電気特性については移動度およびオンオフ比が高く、閾値、駆動電圧、オフ電流を低くすることのできる有機トランジスタ用インク、有機トランジスタの電極及びその形成方法並びに有機トランジスタを提供する。

【解決手段】印刷法で形成される有機トランジスタ用インクであって、金属ナノ粒子と、1つまたは2つ以上の非イオン性界面活性剤と、金属ナノ粒子及び1つまたは2つ以上の非イオン性界面活性剤を溶解または分散させる溶媒と、を含むことを特徴とする有機トランジスタ用インク。

(もっと読む)

有機トランジスタとその製造方法

【課題】熱処理による電気特性の劣化の少ない有機FETを提供することを目的とする。

【解決手段】ゲート絶縁層4の上に、ソース電極5とドレイン電極6とが配置され、ソース電極5とドレイン電極6との上に、有機半導体層8を有する有機トランジスタであって、ソース電極5と有機半導体層8との間、およびドレイン電極6と有機半導体層8との間には、単分子膜7を備えることを特徴とする。また、単分子膜7は、チオール類の単分子を含む膜であることを特徴とする。

(もっと読む)

炭素電極及び炭素電極の製造方法、有機トランジスタ及び有機トランジスタの製造方法

【課題】製造コストの低く、簡易な工程で微細加工が可能な炭素電極を備える有機トランジスタを製造する。

【解決手段】基体11上にゲート電極12を形成する工程と、ゲート電極12を覆ってゲート絶縁層13を形成する工程と、ゲート絶縁層13上にカーボン溶液を塗布して炭素材料層を形成する工程と、炭素材料層にレーザ光18を照射して選択的に炭素薄膜を形成してソース電極15及びドレイン電極を形成する工程と、ソース電極15及びドレイン電極を覆って有機半導体層を形成する工程とにより有機トランジスタを製造する。

(もっと読む)

酸化亜鉛系半導体素子の製造方法

【目的】

p型ZnO系化合物半導体の電極の剥離や金属の凝集が生じず高い接着性を有するとともに良好なオーミック接触を有するコンタクト電極の形成方法及び当該電極が形成されたZnO系化合物半導体素子の製造方法を提供する。

【解決手段】

基板上にn型ZnO系半導体層及びp型ZnO系半導体層を含む積層体をp型ZnO系半導体層が表面に形成されるように形成する工程と、p型ZnO系半導体層をその表面温度が250℃ないし500℃の範囲内で熱処理する工程と、550℃未満の温度で、p型ZnO系半導体層上にp側電極金属を上記熱処理の後に形成する工程と、n型n型ZnO系半導体層上にn側電極金属を形成してZnO系半導体素子を形成する工程と、からなる。

(もっと読む)

201 - 220 / 956

[ Back to top ]