Fターム[4M104AA10]の内容

Fターム[4M104AA10]に分類される特許

121 - 140 / 956

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つソース電極及びドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、加熱処理を行う。この加熱工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設けることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発生するのを防止する。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

新規な電極

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順に3価Cr濃化域、Cr欠乏部、金属Cr濃化域を形成して母材とオーミック接合で一体化しているダイオード用n型半導体担持電極材料。

(もっと読む)

トランジスタ及びその作製方法

【課題】スイッチング特性が良好で、且つ信頼性が高いトランジスタを提供する。

【解決手段】例えば、ボトムゲートトップコンタクト構造のトランジスタを作製するに際して、第1の配線層を形成し、該第1の配線層を覆って第1の絶縁膜を形成し、該第1の絶縁膜上に半導体層を形成し、該半導体層上に導電膜を形成し、該導電膜に少なくとも2段階のエッチングを行って第2の配線層を離間させて形成し、前記2段階のエッチングが、少なくとも前記導電膜に対するエッチングレートが前記半導体層に対するエッチングレートより高い条件により行う第1のエッチング工程と、前記導電膜及び前記半導体層に対するエッチングレートが、前記第1のエッチング工程よりも高い条件により行う第2のエッチング工程と、を有する方法によりトランジスタを作製する。

(もっと読む)

疎水性材料表面上に金属電極を配設する方法

トランジスタおよびその製造方法

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタおよびその製造方法を提供する。

【解決手段】本発明の一態様に係るトランジスタ100は、導体領域10aと表面に原子が結合した半導体領域10bとを有し、チャネルとして機能するグラフェン膜10と、グラフェン膜10上にゲート絶縁膜11を介して形成されたゲート電極12と、を有し、導体領域10aと半導体領域10bが形成するショットキー接合のトンネル電流をスイッチング動作に用いる。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタレイの製造方法及び表示装置の製造方法

【課題】有機薄膜トランジスタを高い歩留まりで製造する製造方法を提供する。

【解決手段】基板上又は基板上における絶縁膜上にソース電極及びドレイン電極を形成する電極形成工程と、有機半導体インクが供給された際、前記ソース電極及び前記ドレイン電極上における前記有機半導体インクの接触角を前記基板上又は前記絶縁膜上における接触角よりも高くする電極処理工程と、形成された前記ソース電極及び前記ドレイン電極の間に前記有機半導体インクを供給することにより有機半導体層を形成する半導体層形成工程と、を有し、前記ソース電極と前記ドレイン電極とにより形成されるチャネルのチャネル幅をW、前記有機半導体インクが供給される際の液滴の液滴径をφ、前記液滴が供給される位置の誤差である着弾位置誤差幅をXとした場合、W>φ+Xを満たしていることを特徴とする有機薄膜トランジスタの製造方法を提供することにより上記課題を解決する。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】絶縁性が高く、かつ均一な膜厚を有するゲート絶縁膜を効率よく形成することができる電界効果型トランジスタの製造方法、及び該電界効果型トランジスタの製造方法により製造され、安定した特性を有する高性能な電界効果型トランジスタの提供。

【解決手段】前記第一の基材上にゲート電極を形成するゲート電極形成工程と、第二の基材上にゲート絶縁膜形成用樹脂溶液を塗布し、ゲート絶縁膜を形成する塗布工程と、前記ゲート絶縁膜表面の流動性が消失するまで乾燥する乾燥工程と、前記ゲート電極と、前記ゲート絶縁膜表面とを接触させて接触体を形成する接触工程と、前記接触体に対し、ゲート絶縁膜形成用樹脂のガラス転移温度以上の熱を加える加熱工程と、前記接触体から前記第二の基材を剥離し、第一の基材上にゲート絶縁膜を形成する剥離工程とを少なくとも含む電界効果型トランジスタの製造方法である。

(もっと読む)

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

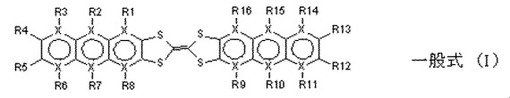

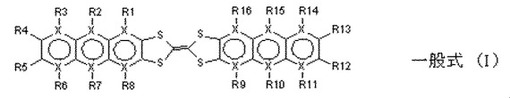

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体の一部が、チャネル保護膜6d(5d)における膜厚の厚い一端側に重なる構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

有機電極を用いた有機薄膜トランジスタとその製造方法

【課題】少なくとも2種類以上の同じ有機化合物を用いてp型、n型両方の有機薄膜トランジスタを作り分けることができ、かつ、有機電極も同時に作製可能となるプロセスアビリティーの高い有機半導体素子およびそれを使った電気回路を提供することにある。さらに、有機電導体、有機超電導体、有機磁性体、有機熱電素子、有機エレクトロクロミック素子、有機エレクトロルミネセンス素子等への応用が可能であること。

【解決手段】少なくとも2種類以上の有機化合物からなる有機電極と、少なくとも1種類以上の有機電極構成成分から選ばれた有機化合物を主成分とする有機半導体活性層から構成された有機半導体素子膜を有する有機薄膜トランジスタ。

(もっと読む)

有機積層膜

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

有機電子装置のための電極処理方法

【課題】有機電子装置のための電極処理方法を提供する。

【解決手段】本発明は、有機電子(OE:organic electronic)装置、特に、有機電界効果トランジスタ(OFET:organic field effect transistor)にける電極の処理方法と、そのような方法によって調製される装置と、そのような方法において使用される材料および配合物とに関する。

(もっと読む)

121 - 140 / 956

[ Back to top ]