Fターム[4M104AA10]の内容

Fターム[4M104AA10]に分類される特許

61 - 80 / 956

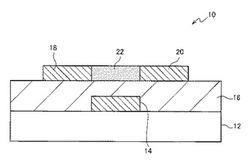

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材21と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜22とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順にFe主体アモルファス酸化物、Cr濃化したFe−Cr結晶酸化物を形成して母材とオーミック接合で一体化しており、n型半導体中のドナー密度が1E16cm−3〜1E18cm−3の範囲で含まれているダイオード用n型半導体担持電極材料。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

薄膜トランジスタ用ゲート絶縁膜および該絶縁膜を備えた薄膜トランジスタ素子

【課題】低温条件下かつ溶液塗布プロセスにより形成可能であり、薄膜トランジスタにおける電気特性であるヒステリシス、On/Off比が良好な薄膜トランジスタ用ゲート絶縁膜及び該絶縁膜を備えた薄膜トランジスタを提供する。

【解決手段】必須成分として(A)アルケニル基を有する化合物、(B)SiH基を有する化合物、(C)ヒドロシリル化触媒を含有する硬化性組成物を低温条件下によるポストベイクしたゲート絶縁膜を用いることにより、良好なトランジスタ特性が発現する。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

ショットキーダイオードおよびその製造方法

【課題】 強誘電体層を有し、逆方向バイアス電圧印加時のリーク電流を低減させ、順方向バイアス電圧印加時の電圧降下を小さくすることができるショットキーダイオードを提供する。

【解決手段】 ショットキーダイオード1は、支持基板11を備え、さらに、支持基板11の表面上に形成された絶縁膜12と、絶縁膜12上に形成された密着層13と、密着層13上に形成されたショットキー金属層14と、ショットキー金属層14の表面上に、ショットキー金属層14とショットキー接触されるように形成され、Mnが添加された第一の誘電体層15と、第一の誘電体層15の表面上に形成され、Mnなどの添加物が添加されていない第二の誘電体層16と、第二の誘電体層16上に、第二の誘電体層16とオーミック接触するように形成されたオーミック金属層17を備えている。

(もっと読む)

薄膜トランジスタ

【課題】寄生容量を小さくでき、応答速度低下を抑制することが可能なTFTを提供する。

【解決手段】基材110上に配設した有機半導体層150と、有機半導体層150と接触し、対向してチャネル領域を形成するソース電極120及びドレイン電極130と、有機半導体層150と絶縁層160を介して設けられるゲート電極140と、ソース電極120と導電接続するソース電極配線部125と、ドレイン電極130と導電接続するドレイン電極配線部135と、ゲート電極140と導電接続するゲート電極配線部145と、からなるTFT100であって、積層方向からみて、有機半導体層150が、ゲート電極140を含み、ゲート電極140が、ソース電極120とドレイン電極130とチャネル領域とからなる領域を含み、有機半導体層150の周縁でソース電極配線部125とドレイン電極配線部135との間にはゲート電極配線部145が配される。

(もっと読む)

配線用Cu合金及びそれを用いた接続構造

【課題】Moなどの密着層を省略し、熱処理もすることなく、ガラスなどの絶縁層に直接配線をCu合金により形成でき、また、表面平滑性の良好な配線を形成する技術を提供する。

【解決手段】本発明は、0.01at%〜0.5at%のBiと、0.05at%〜0.5at%のInと、残部がCu及び不可避不純物とからなることを特徴とする配線用Cu合金とした。また、本発明は、絶縁層とCu合金配線とが直接接合された接続構造において、Cu合金はBi及びInを含有しており、Cu合金配線は、絶縁層との接合界面側にBi偏析層が形成されていることを特徴とするものである。

(もっと読む)

貫通電極基板及びその製造方法

【課題】貫通孔への金属のめっき充填性を向上させることができる技術を提供することである。

【解決手段】貫通孔5が設けられた基板1へ金属を充填するために、貫通孔5が設けられた基板1と導電層4を有する基板2とが結合された基板3を用意する。導電層4から通電して貫通孔5内の一部に第1のめっき層6を形成する。第1のめっき層6上に第2のめっき層7を形成する。第1のめっき層6をエッチング除去し、第1のめっき層6がエッチング除去された孔内に、第2のめっき層7から通電して第3のめっき層9を形成してもよい。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

微細加工構造及び電子デバイス

【課題】プロセス工程の数が従来のリフトオフ方法より少なく、基板との密着性が良好な薄膜パターンの形成が可能な微細加工方法を提供すること。基板との密着性に優れたパターニングされた被加工薄膜を有する微細加工構造を提供すること。移動度が優れた有機トランジスタの作成が可能な微細加工方法及び電子デバイスを提供すること。

【解決手段】基体1上にレジスト膜2を形成する工程、レジスト膜2をパターン露光する工程、現像を行うことなくレジスト膜2上に被加工薄膜4を形成する工程、レジスト膜2の非露光部2bとその上の被加工薄膜4とをリフトオフする工程、を順次行うことを特徴とする。パターン化された被加工薄膜4aと基板1との間に、露光されたレジストパターン2aが介在していることを特徴とする。

(もっと読む)

有機薄膜トランジスタの製造方法及び該方法で製造された有機薄膜トランジスタ

【課題】大面積の素子の製造が容易であり、ソース電極及びドレイン電極を形成する際にゲート絶縁層を損傷せず、有機絶縁材料が有する柔軟性を損なわない、有機薄膜トランジスタの製造方法を提供すること。

【解決手段】ゲート電極、及び該ゲート電極を被覆し、有機絶縁材料を含むゲート絶縁層を形成する工程;該ゲート絶縁層上に塗布法、無電解めっき法又は原子層堆積法を用いて導電性材料からなる第1導電層を成膜する工程;該第1導電層上にパターンニングされた第2導電層を形成する工程;該第2導電層で被覆されていない第1導電層の部分を除去して、第1導電層及び第2導電層からなるソース電極及びドレイン電極を形成する工程;及びソース電極、ドレイン電極、及び該ソース電極と該ドレイン電極に挟まれた領域のゲート絶縁層が被覆されるように、有機半導体層を形成する工程;を有する、有機薄膜トランジスタの製造方法。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

硬化性組成物およびそれを用いた薄膜トランジスタ

【課題】光硬化性を有し、かつ耐溶剤性、メタル配線への密着性に優れた薄膜を与える硬化性組成物を提供することである。

【解決手段】 必須成分として(A)光重合性官能基を有する化合物、(B)アルケニル基を有する化合物、(C)SiH基を有する化合物、(D)光重合開始剤 (E)ヒドロシリル化触媒を含有する硬化性組成物であり、

成分A、Dよる光重合反応と成分B、Cおよび成分Eによるヒドロシリル化反応の2種の反応が進行することにより、光硬化性を有しながら耐溶剤性、メタル配線への密着性に優れた薄膜を与える得ることが可能となる。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】半絶縁性単結晶ダイヤモンド基板の一方の面に、p−ダイヤモンド層からなるドリフト層を成膜し、該ドリフト層の上にp+ダイヤモンド層からなるコンタクト層を成膜する工程と、前記基板の他方の面に開口部をエッチングにより形成して、前記基板を構造保持材として前記ドリフト層の一部が露出した露出部を形成する工程と、前記露出部にカソード電極を設け、前記コンタクト層にアノード電極を設ける工程とにより、ダイヤモンド電子素子の積層構造を形成する。ドリフト層を基板上に直接成膜するので、欠陥密度の減少した素子を得ることができる。

(もっと読む)

61 - 80 / 956

[ Back to top ]