Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

321 - 340 / 2,965

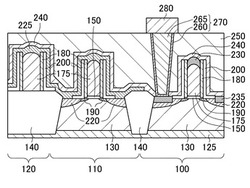

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体素子

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】有機TFTは、ゲート電極2および有機半導体層6と、それらの間に位置すると共に有機半導体層6に隣接するゲート絶縁層3とを備えている。このゲート絶縁層3は、スチレンおよびその誘導体のうちの少なくとも一方である第1単量体(α−メチルスチレンなど)と、炭素間二重結合および架橋性反応基を有する第2単量体(メタクリル酸グリシジルなど)とが共重合および架橋された材料を含んでいる。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化する複数のトレンチ162、各複数のトレンチ162の側壁および底面に形成されたゲート絶縁膜120、ゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112およびゲート長方向の他方の側に形成されたドレイン領域113を有するトランジスタを含む。ここで、トレンチ162の側壁の基板102の表面から底面に向かう途中の位置から底面までの下部分におけるゲート絶縁膜120の膜厚が、当該側壁の途中の位置から表面までの上部分におけるゲート絶縁膜120の膜厚よりも厚く、かつ底面におけるゲート絶縁膜120の膜厚以上である。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

半導体装置

【課題】シリコン基板裏面をソース電極として使用するLDMOSFETにおいて、出力効率向上のため、基板抵抗を下げようとして高濃度ボロンドープ基板を用いると、ソースドレイン間のリーク不良が、多発することが、本願発明者等によって明らかにされた。更に、この不良解析の結果、ソース不純物ドープ領域からP型エピタキシ層を貫通してP型基板に至るP型ポリシリコンプラグに起因する不所望な応力が、このリーク不良の原因であることが明らかにされた。

【解決手段】本願発明は、LDMOSFETを含む半導体装置であって、LDMOSFETのソース不純物ドープ領域の近傍の上面から下方に向けてエピタキシ層内をシリコン基板の近傍まで延び、前記エピタキシ層内にその下端があるシリコンを主要な成分とする導電プラグを有する。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

導電性薄膜の形成方法及び導電性薄膜形成装置

【課題】スパッタ成膜において、あらゆる膜特性を同時に満足させる手法を提供すること。

【解決手段】スパッタ現象を利用して基板上に導電性薄膜を形成する方法であって、薄膜形成中に、スパッタ電力、スパッタガス、および反応性ガスを含む成膜パラメータの少なくとも1つを2つの値に変動させ、その時間分割比を制御することを特徴とする導電性薄膜の形成方法である。また、p型またはn型の導電型を有する半導体上に導電性薄膜を形成する方法において、半導体上への成膜開始時点に、強度にプラズマ照射を行うことを特徴とする導電性薄膜の形成方法も採用できる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

半導体装置、貼り合せ基板およびそれらの製造方法

【課題】低コストで高品質の半導体装置、および当該半導体装置の製造に用いる貼り合せ基板、およびこれらの製造方法を提供する。

【解決手段】半導体素子の製造方法は、単結晶半導体部材を準備する工程(S10)と、支持基材を準備する工程(S20)と、支持基材と単結晶半導体部材とを、炭素を含む接合層を介して接合する工程(S30)と、単結晶半導体部材の表面にエピタキシャル層を形成する工程(S40)と、エピタキシャル層を利用して半導体素子を形成する工程(S50)と、半導体素子を形成する工程(S50)の後、接合層を酸化することにより分解して支持基材から単結晶半導体部材を分離する工程(S60)と、支持基材から分離された単結晶半導体部材を分割する工程(S80)とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つチャネルの劣化を抑制可能なトレンチゲートを有する半導体装置を提供する。

【解決手段】n型のドレイン層11と、ドレイン層11の主面に配設され、ドレイン層11よりも不純物濃度が低いn型のドリフト層12と、ドリフト層12上に配設されたp型のベース層13と、ベース層13の表面領域に配設され、ドリフト層12よりも不純物濃度が高いn型のソース層14と、ソース層14及びベース層13を貫通し、ドリフト層12に達する深さを有して配設されたストライプ状のゲートトレンチ16と、ゲートトレンチ16を形成する側面及び底面に沿って配設されたトレンチ形状のゲート絶縁膜17と、ゲート絶縁膜17の開口幅の狭い対向する側面に設けられた触媒層18と、トレンチ形状のゲート絶縁膜17内に、触媒層18に接続されたカーボンナノチューブ19が配設されたゲート電極21とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

321 - 340 / 2,965

[ Back to top ]