Fターム[4M104BB25]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | TiSi (828)

Fターム[4M104BB25]に分類される特許

81 - 100 / 828

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体デバイスとその製造方法

【課題】裏面電極/半導体基板の間のエネルギー障壁が低く、半導体デバイスのオン抵抗が低減され、裏面電極の露出面の耐腐食性が良好で、かつ、裏面電極と半導体基板との密着性が良好で、裏面電極の材料コストを抑えることが可能な半導体デバイスを提供する。

【解決手段】裏面電極300は、Si基板101側から順にTiシリサイド層301とTi層302とNi層303とAg層304とAu層305とが積層された積層構造、又はSi基板101側から順にTiシリサイド層301とNi層303とAg層304とAu層305とが積層された積層構造を有する。裏面電極300は、Si基板101にTi層302とNi層303とAg層304とを順次成膜した後にシンター処理を行ってTiシリサイド層301を生成し、その後Au層305を成膜して製造されたものであることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置がSBDとして良好なショットキー特性を得ることができるようにする。

【解決手段】主面2a側がn型領域12とされると共に当該主面2aにp型領域15を形成してなる炭化珪素基板の主面2aのうち、p型領域15の表面15aのみを荒らす粗面化工程と、前記炭化珪素基板2の主面2aを洗浄液により洗浄する洗浄工程と、一種類の金属材料からなる一体の電極用金属層を、前記n型領域12の表面12a及び前記p型領域15の表面15aの両方に接触させるように、前記主面2aに形成する接続工程とを備える半導体装置の製造方法を提供する。

(もっと読む)

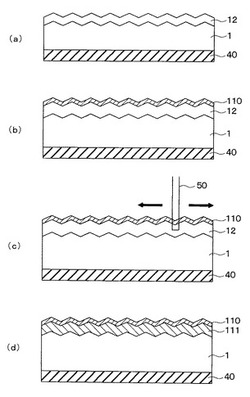

熱処理方法および熱処理装置、ならびに半導体装置の製造方法

【課題】従来技術よりも小さい熱エネルギーで、SiC基板上に低抵抗のオーミック電極を形成することができ、熱処理における半導体装置の素子部の損傷および特性の劣化を防止することができる熱処理方法および熱処理装置、ならびに前記熱処理方法を用いた半導体装置の製造方法を提供する。

【解決手段】熱処理装置1の電源部21によって、複数のパルスを含むパルス列で構成される複数パルス電流を発生させ、導線22および電流端子部23を介して、SiC基板11上の電極金属膜12に供給する。これによって電極金属膜12にジュール熱を発生させ、発生したジュール熱によって電極金属膜12を加熱する。

(もっと読む)

ショットキーバリアダイオード

【課題】順方向サージ耐圧と順方向降下電圧VFとのトレードオフ特性を改善することが可能で、かつ、逆方向漏れ電流IRが増加してしまうことのないショットキーバリアダイオードを提供する。

【解決手段】第1主面及び当該第1主面の反対面である第2主面を有し、炭化珪素からなるn型の半導体基体110と、半導体基体110における第1主面上に形成されたバリアメタル層118と、半導体基体110における第1主面側の表面に部分的に形成され、高濃度のp型不純物を含有する小数キャリア注入層128と、小数キャリア注入層128の直下にのみカーボンが導入されたカーボン導入層132とを備えるショットキーバリアダイオード100。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗体の上に急速熱酸化処理により形成され、シリサイド化ブロック用酸化膜の一部として用いる熱酸化膜の膜厚が多種のポリシリコン抵抗体間でばらつくことにより、ポリシリコン抵抗体が部分的にシリサイド化されることを回避する。

【解決手段】多種のポリシリコン抵抗体全てにおいて、急速熱酸化処理によりポリシリコン抵抗体上に生成される熱酸化膜の膜厚と、ポリシリコン抵抗体を含む非シリサイド化領域に形成された保護酸化膜の膜厚との和が、シリサイド化ブロック用酸化膜としてのブロック性能を確保するために必要な膜厚以上となるように、保護酸化膜の膜厚を決定する。多種のポリシリコン抵抗体間で急速熱酸化処理により生成される熱酸化膜の膜厚に差が生じる場合でも、熱酸化膜と保護酸化膜とをシリサイド化ブロック用酸化膜として用いることにより、充分なブロック性能を確保することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のオン抵抗をより低減させる。

【解決手段】第1導電型の半導体層と、前記半導体層の上側に、前記半導体層の主面に対して平行な方向に沿って周期的に配置された第1導電型の半導体ピラー領域と、前記第1導電型の半導体ピラー領域の表面に選択的に設けられた第2導電型のベース領域と、前記第2導電型のベース領域の表面に選択的に設けられたソース領域と、前記第1導電型の半導体ピラー領域間に設けられ、前記ベース領域の表面にまで達する第2導電型の半導体ピラー領域と、前記ソース領域に電気的に接続された第1の主電極と、前記半導体層の下側に設けられ、前記半導体層に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間の通電を制御する制御電極と、を備える。

(もっと読む)

シーケンシャル化学気相成長法

【課題】本発明は、高い反応性をもつガス(ラジカル)を利用できるようにラジカル発生装置を用いて、いかなる元素の薄膜の成長をも容易に行うことができる方法を提供する。

【解決手段】複数のサイクルを含むシーケンシャル気相成長法による、基板上へのAl2O3薄膜の成長方法において、それぞれのサイクルは、ガス状のトリメチルアルミニウム(TMA)にパーツを接触させること、ガス状のTMAの供給を停止すること、チャンバからガス状のTMAを除去すること、及び原子状酸素にパーツを接触させることを含む。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

81 - 100 / 828

[ Back to top ]