Fターム[4M104BB25]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | TiSi (828)

Fターム[4M104BB25]に分類される特許

101 - 120 / 828

半導体装置

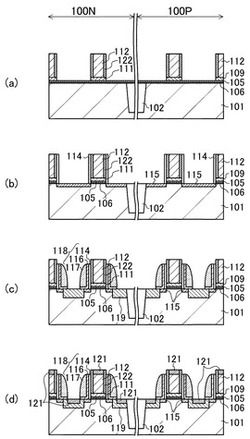

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

半導体装置の製造方法

【課題】最近の多層メタルスパッタリング成膜プロセスにおいては、従来のマルチチャンバ型の装置に代わって、単一チャンバ&マルチ成膜サイト型の装置が広く使用されるようになっている。しかし、本願発明者が検討したところによると、このような単一チャンバ&マルチ成膜サイト型スパッタリング成膜装置は、磁性メタル膜と非磁性メタル膜を積層形成する場合は、被処理ウエハを別の成膜サイトに移送して成膜する必要があり、スループットを大きく低下させていることが明らかとなった。

【解決手段】本願発明は、単一チャンバ&マルチ成膜サイト型多層スパッタリング成膜装置を用いた半導体装置の製造方法において、少なくとも一つの成膜サイトにおいて、磁性および非磁性ターゲットの両方を切り替えて用い、磁性および非磁性膜の両方の膜を成膜するものである。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SiGe等の半導体膜が形成された領域と、酸化シリコン膜から成るゲート絶縁膜が形成された領域とが同一基板上に形成される際に、ゲート絶縁膜を精度良く形成する。

【解決手段】基板10を熱酸化することにより、第1素子領域101及び第2素子領域201に、第1ゲート絶縁膜110及び第2ゲート絶縁膜210を形成し、かつ第3素子領域301及び第4素子領域401それぞれに位置する基板10に熱酸化膜を形成する。次いで、第4素子領域401に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する基板10上に半導体膜414を成膜する。次いで、第3素子領域301に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する半導体膜414上、及び第3素子領域301に位置する基板10上に第3ゲート絶縁膜310及び第4ゲート絶縁膜410を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体素子及びその製造方法

【課題】埋め込みビットラインコンタクトホール内にディフュージョンバリアーを形成して素子の特性を改善する。

【解決手段】半導体基板100をエッチングして複数個のピラーパターンを形成する段階と、前記ピラーパターンの表面に絶縁層を蒸着する段階と、前記ピラーパターンの一側の前記絶縁層の一部を除去して前記ピラーパターンが露出されるコンタクトホールを形成する段階と、前記コンタクトホール内にバリアー膜170aを形成する段階と、前記コンタクトホールと接する前記ピラーパターン内に接合180を形成する段階と、前記ピラーパターンの間の底部に前記コンタクトホールと接続して形成された埋め込みビットラインとを含む。

(もっと読む)

トレンチ金属酸化物半導体電界効果トランジスタの製造方法

【課題】多孔質のトレンチ金属酸化物半導体電界効果トランジスタ(MOSFET)を提供する。

【解決手段】多孔質のMOSFETの製造方法は、トレンチ領域をパターニングするために第1のエピタキシャル(エピ)層の上に第1のフォトレジストを堆積する段階と、メサ領域をパターニングするために第1のゲート導体層の上に第2のフォトレジストを堆積する段階と、ハンプを有する第2のゲート導体層を形成するために前記メサ領域の前記第1のゲート導体層の部分をエッチング除去する段階と、Tiゲート導体層を形成するために前記第2のゲート導体層を結晶的にチタン化する段階と、を含む。メサ領域の端部は、トレンチ領域の端部に位置合わせされる。従って、第2のゲート導体層のポリシリコンの約半分超は、結晶的にチタン化される。スペーサは、第1のゲート導体層の角部を保護し、ゲート構造体を機械的な支持体に対してより強固にするために形成される。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

電子回路用の保護素子

集積半導体構成体を有する保護素子と、この保護素子の製造方法が記載される。この保護素子は、少なくも1つのショットキーダイオード(S)と少なくとも1つのツェナーダイオード(Z)とを有し、電流供給部と電子回路との間に接続される。ここでは前記ショットキーダイオード(S)のアノードが電流供給部と接続されており、前記ショットキーダイオード(S)のカソードが電子回路および前記ツェナーダイオードのカソードと接続されており、該ツェナーダイオードのアノードがアースと接続されている。ショットキーダイオード(S)は、トレンチ・MOS・バリア・ジャンクション・ダイオードまたはトレンチ・MOS・バリア・ショットキーダイオード(TMBSダイオード)またはトレンチ・ジャンクション・バリア・ショットキーダイオード(TJBSダイオード)であり、少なくとも1つのトレンチ・MOS・バリア・ショットキーダイオードと、ツェナーダイオード(Z)のアノードとして用いられるpドープ基板とを有する集積半導体構成体を含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

101 - 120 / 828

[ Back to top ]