Fターム[4M104DD63]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048)

Fターム[4M104DD63]の下位に属するFターム

Fターム[4M104DD63]に分類される特許

241 - 260 / 588

駆動回路及び表示装置

【課題】酸化物半導体にチャネル形成領域を設ける薄膜トランジスタで構成された駆動回路を有する表示装置において、回路が占める面積を大きくすることなく、薄膜トランジスタのしきい値電圧のシフトを低減し、且つ薄膜トランジスタをオフにした際にソースとドレインの間を流れる電流を低減する。

【解決手段】複数のインバータ回路及び複数のスイッチを有し、インバータ回路は、第1の酸化物半導体膜を有する第1の薄膜トランジスタと、第2の酸化物半導体膜を有する第2のトランジスタと、を有し、第1の薄膜トランジスタ及び第2の薄膜トランジスタは、エンハンスメント型であり、第1の酸化物半導体膜及び第2の酸化物半導体膜上に接してOH基を有する酸化珪素膜が設けられ、酸化珪素膜上に接して窒化珪素膜が設ける。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置、および電子機器

【課題】エッチング耐性良好なゲート絶縁膜によってトランジスタ特性を維持しながらも微細化が可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1は、表面層を構成するポリパラキシリレン層7bとこれとは異なる材料からなる有機絶縁層7aとを積層してなるゲート絶縁膜7を備えている。ゲート絶縁膜7のポリパラキシリレン層7b上にはソース電極9sおよびドレイン電極9dがパターン形成されている。またソース電極9s−ドレイン電極9d間にわたるゲート絶縁膜7のポリパラキシリレン層7b上には有機半導体層11が設けられている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

半導体装置の製造方法

【課題】 はんだ接合可能な上側電極と下側電極を有する半導体装置を好適に製造することができる半導体装置の製造方法を提供する。

【解決手段】 上側電極46と下側電極48を有する半導体装置10を製造する方法であって、半導体基板100の上面にオーミック接触する上側オーミック金属層46eを形成する上側オーミック金属層形成工程S4と、半導体基板100の下面にオーミック接触する下側オーミック金属層48fを形成する下側オーミック金属層形成工程S10と、メッキ法によって、上側オーミック金属層46eの表面と下側オーミック金属層48fの表面に、ニッケルと銅の少なくとも一方を含む表面金属層46c、48dを形成する表面金属層形成工程S12を有する。

(もっと読む)

半導体装置

【課題】 高い耐圧と低いオン抵抗を兼ね備えた縦型の半導体装置を提供する。

【解決手段】 縦型のパワーMOS100は、第2導電型のボディ領域14と第1導電型のドリフト領域4とトレンチ11と第2導電型の不純物含有領域6とゲート電極12と浮遊電極8を備えている。不純物含有領域6は、トレンチ11の底面11aを囲む範囲に配置されている。不純物含有領域6の中心D2は、ドリフト領域4の中間深さD3より深い位置に配置されている。ゲート電極12は、トレンチ11内に配置されており、壁面が絶縁膜22で被覆されており、ボディ領域14の底面14aより深い位置まで伸びている。浮遊電極8は、トレンチ11内のゲート電極12より深い位置に配置されており、壁面が絶縁膜22で被覆されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ソフトリカバリー特性の良好なダイオードを単純な製造方法で得る。

【解決手段】n−層102中には、軽元素のイオン注入によって形成されたn側結晶欠陥層107が、図1(b)における上下方向に延びたストライプ状に局所的に形成されている。p側結晶欠陥層108も同様であり、図1(a)に示されるように、p側結晶欠陥層108とn側結晶欠陥層107とは隣接して交互に形成されている。また、アノード電極104の厚さは均一ではなく、薄い箇所と厚い箇所が交互に存在する不均一な厚さをもつ電極である。その薄い箇所に対応してn側結晶欠陥層107が形成され、厚い箇所に対応してp側結晶欠陥層108が形成されている。

(もっと読む)

表示装置

【課題】オフリーク電流を低減させた薄膜トランジスタを備える表示装置の提供。

【解決手段】表示部が形成される基板上に薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、ゲート電極と、前記ゲート電極を被って形成されたゲート絶縁膜と、前記ゲート絶縁膜の上面に、平面的に観て前記ゲート電極からはみ出すことなく、前記ゲート電極に重畳して形成された島状の半導体層と、前記半導体層を被って形成された絶縁膜と、前記絶縁膜に形成された一対のスルーホールのそれぞれを通して前記半導体層と電気的に接続された一対の電極とを備え、

前記半導体層は、結晶性半導体層と非晶質半導体層の順次積層体からなり、前記電極のそれぞれは、不純物がドープされた半導体層と金属層の順次積層体からなっている。

(もっと読む)

表示装置およびその製造方法

【課題】低いコンタクト抵抗および高い耐食性を両立したAl合金膜を有する表示装置を提供する。

【解決手段】酸化物導電膜とAl合金膜とが直接接触しており、前記Al合金膜の接触表面に合金成分が析出して存在する表示装置であって、前記Al合金膜が、Ni、Ag、Zn及びCoよりなる群から選ばれる元素(以下X1と称することがある)の少なくとも1種以上、且つ前記元素X1と金属間化合物を形成することのできる元素(以下X2と称することがある)の少なくとも1種以上を含み、最大径150nm以下のX1−X2又はAl−X1−X2で示される金属間化合物が形成されており、前記Al合金膜の接触表面の算術平均粗さRaが2.2nm以上20nm以下ある。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

半導体素子およびその製造方法並びに表示装置

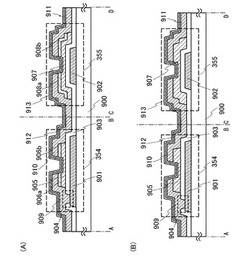

【課題】過剰なエッチングを生じることなく、同一のエッチング行程において、複数のコンタクトホールを同時に形成することができ、歩留まりおよび生産性に優れた半導体素子およびその製造方法並びに表示装置を提供することを目的とする。

【解決手段】TFT12は、ボトムゲート電極20、ボトムゲート絶縁膜17、半導体層13、トップゲート絶縁膜18、トップゲート電極14及び層間絶縁膜19がこの順に積層された構造を有する。また、トップゲート絶縁膜18および層間絶縁膜19には、コンタクトホール25〜28が形成されている。また、層間絶縁膜19の表面には、ボトムゲート電極20、半導体層13、およびトップゲート電極14の各々に接続される配線30〜32が形成されている。そして、ボトムゲート電極20の、配線31との接続領域34に、ボトムゲート電極20の下方に配置されるとともに、ボトムゲート電極20を支持する段差部材35が設けられている。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

半導体装置の作製方法、半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置な

らびに半導体装置において、TFTを作製する工程数を削減して製造コストの低

減および歩留まりの向上を実現することを目的としている。

【解決手段】 基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶

縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と

、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部

に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲ

ート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層

とから形成されていることを特徴としている。このような構成とすることで、フ

ォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる

。

(もっと読む)

半導体装置及びその製造方法

【課題】高いスイッチング速度と低いオン抵抗とを両立させたIGBTを得る。

【解決手段】このIGBT10においては、結晶欠陥層25が、活性領域20においてはn層102中に、非活性領域40においてはp型基板101中に形成されている。すなわち、活性領域20における結晶欠陥層25は、非活性領域40における結晶欠陥層25よりも表面からみて浅い位置に形成されている。このIGBT10においては、上記の構成により、正孔注入量が非活性領域40において少なくされることにより、スイッチング速度が高くなる。一方、活性領域20における正孔注入量の減少は非活性領域40よりも小さくなる。従って、この際のオン抵抗の増大は抑制される。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】複数個あるTFTの少なくとも一部について、半導体膜とゲート電極膜が対向する面積のチャネル領域に対する相対的な面積が異なることにより、光リーク電流の発生を抑えつつ、容量増加を抑制する構造の平面ディスプレイを提供する。

(もっと読む)

表示装置およびその製造方法

【課題】低リークで特性のばらつきの少ない薄膜トランジスタを備える表示装置の提供。

【解決手段】表示部を備える基板に薄膜トランジスタが形成された表示装置であって、

前記薄膜トランジスタは、ゲート電極と、前記ゲート電極を被って形成されたゲート絶縁膜と、

前記ゲート絶縁膜の上面に前記ゲート電極を跨って形成された、少なくとも、多結晶半導体膜、非晶質半導体膜、および高濃度ドープト非晶質半導体層の順次積層体からなる半導体膜積層体と、

前記半導体膜積層体の上面に前記ゲート電極に重なる領域を間にして互いに対向して配置される第1電極と第2電極を備え、

前記第1電極と第2電極の間の前記高濃度ドープト非晶質半導体層はその下層の非晶質半導体膜が露出する程度に除去され、

前記第1電極から延在される配線の直下および前記第2電極から延在される配線の直下のそれぞれに前記半導体膜積層体が形成された構成からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

窒化物半導体装置

【課題】高耐圧でスイッチングスピードに優れ高い高周波特性を有するノーマリオフ型のHEMTを提供すること。

【解決手段】第1のバンドギャップを有する第1の窒化物半導体層2と前記第1のバンドギャップよりも大きい第2のバンドギャップを有し前記第1の窒化物半導体層上とヘテロ接合される第2の窒化物半導体層3とを備える主半導体領域と、前記主半導体領域上に形成されるソース電極5と、前記主半導体領域上において前記ソース電極5と離間して形成されるドレイン電極6と、前記第1の窒化物半導体層上において前記ソース電極5と前記ドレイン電極6との間に形成される第3の窒化物半導体層10と、前記第3の窒化物半導体層10上に形成されるゲート電極7とを備え、前記第3の窒化物半導体層10が前記第1のバンドギャップよりも小さい第3のバンドギャップを有することを特徴とする窒化物半導体装置。

(もっと読む)

有機薄膜トランジスタ

【課題】誘電体層と半導体層の間の所定の構造の2つの界面層を有する、オン/オフ比や移動度の改良された薄膜トランジスタを提供する。

【解決手段】OTFT10は、誘電体層40と半導体層70の間に2つの界面層80,90があり、一方の界面層が、シロキサンポリマーまたはシルセスキオキサンポリマーから形成されており、他方の界面層が、式(I)のシランから形成されている。

式(I)

(上記式(I)中、R’は、約1個から約24個までの炭素原子を有するアルキルであり、R”は、約1個から約24個までの炭素原子を有するアルキル、ハロゲン、アルコキシ、ヒドロキシルまたはアミノであり、Lは、ハロゲン、酸素、アルコキシ、ヒドロキシル、またはアミノであり、kは、1または2であり、mは、1、2または3である。)

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】複数の物質層間の溶解度差を利用してダブルパターニングを具現する半導体素子の微細パターンの形成方法を提供する。

【解決手段】半導体素子の微細パターンの形成方法は、基板100上に、空間を介して相互に離隔されている複数の第1マスクパターン120を、基板100の主面と平行方向に形成するステップと、溶解剤に対して第1溶解度を有する第1物質からなる複数のキャッピング層130を、複数の第1マスクパターン120のそれぞれの側壁及び上面に形成するステップと、溶解剤に対して第1溶解度より低い第2溶解度を有する第2物質からなる第2マスク層を、空間内に形成するステップと、溶解剤を利用してキャッピング層130を除去し、かつ、第2マスク層の一部を除去した後、空間に残った第2マスク層の残留部分を、複数の第2マスクパターン140Aとして形成するステップと、を含む。

(もっと読む)

241 - 260 / 588

[ Back to top ]