Fターム[4M104DD63]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048)

Fターム[4M104DD63]の下位に属するFターム

Fターム[4M104DD63]に分類される特許

261 - 280 / 588

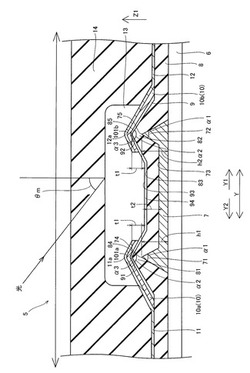

表示装置

【課題】表示装置を駆動させるためのトランジスタとして量子細線を用いた場合に、小型

化および薄型化をより図ることが可能な表示装置を提供する。

【解決手段】この表示装置100は、ガラス基板6の表面から上方(矢印Z1方向側)に

向かって延びるように形成された凸部71(72)を含むゲート電極7と、ゲート電極7

の凸部71(72)と平面的に見て重なるとともに、ゲート電極7上にゲート絶縁膜8を

介して形成される量子細線9と、量子細線9にそれぞれ接続されるソース電極11および

ドレイン電極12とを含む量子細線トランジスタ5を備える。また、ゲート電極7の凸部

71(72)と量子細線9との間の距離t1は、ゲート電極7の凸部71(72)以外の

部分と量子細線9との間の距離t2よりも小さい。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた順スタガ型(トップゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、弊害なく半導体装置の高耐圧化、耐圧安定化、電極の電位安定化、耐圧保持領域のシュリンクなどに活用される半絶縁性膜を形成することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体基板表面にP型領域を形成する工程と、該P型領域上にAl電極を形成する工程と、該Al電極と接し、Alと比較してSiと反応しづらい物質からなる層間膜を形成する工程と、該層間膜上にSiを含有する半絶縁性膜を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産性高く作製する方法を提案することを課題とする。

【解決手段】ゲート電極層と、該ゲート電極層上にゲート絶縁層と、該ゲート絶縁層上に該ソース電極層及び該ドレイン電極層と、ソース電極層及びドレイン電極層上にバッファ層と、該バッファ層上に半導体層とを含む薄膜トランジスタを有し、ゲート電極層と重なる半導体層の一部は、ゲート絶縁層上に接し、且つ、ソース電極層とドレイン電極層の間に設けられ、半導体層はインジウム、ガリウム、及び亜鉛を含む酸化物半導体層であり、バッファ層はn型の導電型を有する金属酸化物を含み、半導体層とソース電極層及びドレイン電極層とはバッファ層を介して電気的に接続する。

(もっと読む)

酸化物薄膜トランジスタ、及びその製造方法

【課題】 安定した特性を有する酸化物薄膜トランジスタ、およびその製造方法を提供すること。

【解決手段】

酸化物半導体層9上面に積層するゲート絶縁層5を、酸化物半導体層9を覆う非フッ素系有機樹脂層51と、非フッ素系有機樹脂層51を覆うアモルファスパーフルオロ樹脂層52とから構成した。ゲート絶縁層5の構成要素としてアモルファスパーフルオロ樹脂層52を用いることにより、安定した特性を有する酸化物薄膜トランジスタ1が得られることが確認された。また、非フッ素系有機樹脂層51の材質として、アモルファスパーフルオロ樹脂よりも誘電率の高いPVPを採用したことにより、駆動電圧の低い酸化物薄膜トランジスタ1が得られることが確認された。これにより、性能の良い酸化物薄膜トランジスタ1を、簡単、且つ安価に得ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】アクティブマトリクス型の表示装置においては、回路を構成する薄膜トランジスタの電気特性が重要であり、この電気特性が表示装置の性能を左右する。従って、逆スタガ型の薄膜トランジスタにIn、Ga、及びZnを含む酸化物半導体膜を用い、電気特性のバラツキを低減する。

【解決手段】課題を解決するため、大気に触れることなくゲート絶縁膜と、酸化物半導体層と、チャネル保護膜との三層をスパッタ法により連続成膜を行う。また、酸化物半導体層においてチャネル保護膜と重なる領域の膜厚が導電膜と接する領域の膜厚よりも厚くなる特徴的な構造とする。

(もっと読む)

配線、その製造方法、薄膜トランジスタおよび表示素子

【課題】良好な形状制御性を確保しつつ、銅配線層の酸化および銅の拡散を抑制できる配線を提供する。

【解決手段】金属拡散防止膜51上に形成したシード層52を、レジストを用いて選択的に除去する。レジストを除去した後、シード層52を覆って無電解めっき法により銅配線層53と、銅配線層53上に位置するメタルマスク層54とを形成する。メタルマスク層54を用いて金属拡散防止膜51を選択的に除去する。良好な形状制御性を確保しつつ、金属拡散防止膜51の形成時のエッチングなどによる銅配線層53の表面荒れなどを防止して、銅配線層53の酸化および銅の拡散を抑制できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

ゲイン変化補償を伴うトランジスタ

半導体装置(10)およびこれを製造方法は、活性素子領域(12)および隔離領域(14)を提供する工程を含み、隔離領域は、活性素子領域との境界(32)を形成する。パターン化ゲート材料(16)は、境界の第1部分(34)と第2(36)部分との間において、活性素子領域と重なる。パターン化ゲート材料は、活性素子領域内において、チャネルを画定し、ゲート材料は、境界領域の第1部分および第2部分の付近において、境界の第1部分と第2部分との間よりも大きい(24+26,28+30)、ゲート材料の主要寸法に沿って中心線(18)と直交するゲート長さ寸法を有する。チャネルは、境界の第1部分に隣接する第1端と、境界の第2部分に隣接する第2端とを含み、更に、チャネルの両端においてテーパが付けられたゲート長さ寸法によって特徴付けられる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】工程効率が向上し、かつ、信頼性が向上した酸化物半導体薄膜トランジスタ基板とその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、絶縁基板上に形成され、ゲート電極を含むゲート線と、ゲート線と交差しドレイン電極接続部を含むデータ線と、ゲート電極の周辺に形成される酸化物半導体活性層パターンと、データ線と酸化物半導体活性層パターンの上に形成されドレイン電極接続部を露出する第1開口部、及び酸化物半導体活性層パターンを露出する第2開口部を有するパシベーション層と、第1開口部及び第2開口部によって酸化物半導体活性層パターンとドレイン電極接続部とを電気的に接続するドレイン電極とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】

基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

発光素子

【課題】拡散電極へ全体的に均一に電流を流すことができ、発光素子の発光効率を向上させたフリップチップ型発光素子を提供する。

【解決手段】発光層へ電流を供給し所定方向へ延びる延在部11aを有する拡散電極11と、拡散電極11上に設けられ延在部11aの幅方向中央に延在部11aの長手方向に並べられ、互いの長手方向ピッチの寸法の半分の寸法が延在部11aの外縁までの寸法と同じ若しくは短い複数の中間電極12と、拡散電極11上に形成される絶縁層と、絶縁層上に形成され中間電極12を介して拡散電極11へ電流を供給する接合電極と、を備えた。

(もっと読む)

フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法

【課題】フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法に関する。

【解決手段】当該アレイ基板の製造方法は、基板にゲート・ラインとゲート電極パターンを形成するステップと、データ・ラインと、ソース電極と、ドレイン電極と、TFTチャネル領域パターンとを形成し、フォトレジストを残し、パッシべーション層を堆積し、剥離工程によってフォトレジスト及びその上のパッシべーション層を除去するステップと、フォトレジストを塗布し、フォトレジストに山状の縁部のバリを形成し、透明導電薄膜を堆積し、剥離工程によってドレイン電極に直接に接続する画素電極パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 所望のVthが異なる複数種類のMOSFETに対してVthを選択的に制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板40上の複数種類のMOSFET(Tr1−Trn)を形成する領域に、二酸化シリコンを含む第1ゲート絶縁膜45と、金属酸化物を含む第2ゲート絶縁膜46を形成する工程と、第1ゲート絶縁膜45及び第2ゲート絶縁膜46上にポリシリコンを含むゲート電極47を形成する工程とを有する。この方法は更に、ゲート電極47の形成後、複数種類のMOSFET(Tr1−Trn)のうち、1種類以上のMOSFET(Trn)の温度を、他の種類のMOSFET(Tr1−Tr3)の温度と異ならせるように熱処理する工程を有する。

(もっと読む)

液晶表示装置用アレイ基板製造用のエッチングテープ

【課題】本発明は液晶表示装置用アレイ基板製造用のエッチングテープを提供する。

【解決手段】本発明のエッチングテープは、ベースシート及びベースシート上にゲルタイプのエッチング物質が塗布されて形成されたエッチング物質層を含む。このエッチングテープは、透明絶縁基板上にゲート電極、ストレージキャパシターの第1電極、ゲート配線を形成する段階、ゲート絶縁膜、アクティブ層、オーミック接触層、ソース電極及びドレーン電極を形成し、誘電体層及びストレージキャパシターの第2電極を形成し、データ配線を形成する段階、画素電極を形成し、ゲートパッド電極を形成し、データパッド電極を形成する段階、保護層を形成する段階及びゲートパッド電極上に形成された保護層とデータパッド電極上に形成された保護層をエッチングすることでコンタクトホールを形成する段階を含む液晶表示装置用アレイ基板の製造方法に利用される。

(もっと読む)

半導体装置およびその製造方法

【課題】より微細化が可能な半導体装置を提供する。

【解決手段】基板の表面から所定の深さまでの領域に設けられたソース電極およびドレイン電極と、これら2つの電極よりも基板内の深い位置に設けられたゲート電極とを含むMOSトランジスタが複数設けられ、複数のMOSトランジスタのソース電極またはドレイン電極と接続され、基板においてソース電極およびドレイン電極と同層または基板の表面よりも深い位置に設けられた配線を有する。

(もっと読む)

半導体装置の製造方法

【課題】WPP技術を使用する半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】半導体ウェハW3に形成されている製品チップ領域(例えば、製品チップ領域CAや製品チップ領域CB)に製品パターンを形成する。そして、製品チップ領域の外側にある外周領域の大部分にも製品パターンの一部を形成する。一方、外周領域に形成されているネーミング領域NRを覆うように開口部を有さないレジストパターンRMを形成する。外周領域に形成されているレジストパターンRMと製品チップ領域CBとの間に開口パターンKP1を形成する。このようなパターンが形成された半導体ウェハW3に対して、電解めっきを実施する。

(もっと読む)

261 - 280 / 588

[ Back to top ]