Fターム[4M104DD63]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048)

Fターム[4M104DD63]の下位に属するFターム

Fターム[4M104DD63]に分類される特許

61 - 80 / 588

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

貫通電極基板及びその製造方法

【課題】貫通孔への金属のめっき充填性を向上させることができる技術を提供することである。

【解決手段】貫通孔5が設けられた基板1へ金属を充填するために、貫通孔5が設けられた基板1と導電層4を有する基板2とが結合された基板3を用意する。導電層4から通電して貫通孔5内の一部に第1のめっき層6を形成する。第1のめっき層6上に第2のめっき層7を形成する。第1のめっき層6をエッチング除去し、第1のめっき層6がエッチング除去された孔内に、第2のめっき層7から通電して第3のめっき層9を形成してもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

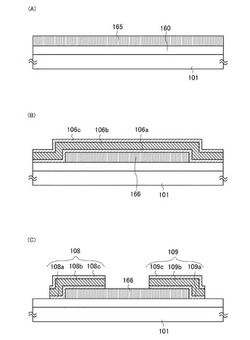

半導体装置

【課題】表示装置に用いられるトランジスタは、より高耐圧なものが求められており、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図る。

【解決手段】チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられたトランジスタを有する半導体装置である。バッファ層は、チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にあって、特にドレイン端近傍の電界を緩和して、トランジスタの耐圧を向上させるように設けられる。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、酸化物半導体層と、例えばソース電極やドレイン電極を構成する金属膜との安定した界面の形成が可能である配線構造を提供する。

【解決手段】基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、半導体層と金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層はTi酸化膜から構成されており、且つ、Ti酸化膜は半導体層と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好な半導体装置及びその作製方法を提供する。

【解決手段】絶縁層上に形成された酸化物半導体層と、酸化物半導体層の一部と重なるソース電極層及びドレイン電極層と、酸化物半導体層の一部と接するゲート絶縁層と、ゲート絶縁層上にゲート電極層と、を有するトランジスタにおいて、ソース電極層と酸化物半導体層、及びドレイン電極層と酸化物半導体層のそれぞれの間にn型の導電型を有するバッファ層を形成することで、寄生抵抗を低減させ、トランジスタのオン電流特性を向上させる。

(もっと読む)

成膜方法、半導体装置及びその製造方法、並びに基板処理装置

【課題】真空装置を使用せずに、トランジスタ等の半導体装置に適用できるMOS構造の積層膜を形成する。

【解決手段】成膜方法は、半導体膜3を有する基板に、ポリシラン溶液を塗布し、半導体膜3上にポリシラン膜5を形成する工程(STEP1)と、ポリシラン膜5上に、金属塩溶液を塗布し、金属イオン含有膜7を形成することにより、ポリシラン膜5をポリシロキサン膜5Aへ、金属イオン含有膜7を金属微粒子含有膜7Aへ、それぞれ改質する工程(STEP2)を備え、MOS構造の積層膜100を形成する。

(もっと読む)

トレンチゲート型トランジスタの製造方法

【課題】トレンチゲート型トランジスタの製造方法において、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12の表面にトレンチ14を形成し、該表面とトレンチ14内に、熱酸化によりシリコン酸化膜15Aを形成し、これを覆うホトレジスト補強膜16、及びホトレジスト補強膜16を覆うホトレジスト層R2を形成する。そしてホトレジスト層R2及びホトレジスト補強膜16をエッチバックしてトレンチ14内にのみに残す。このホトレジスト層R2及びホトレジスト補強膜16をマスクとして、トレンチ14の側壁の上方のシリコン酸化膜15Aをエッチングして除去する。上記マスクを除去した後、熱酸化により、トレンチ14の側壁の上方にシリコン酸化膜15Aより薄いシリコン酸化膜15Bを形成する。その後、シリコン酸化膜15A,15B上にゲート電極18を形成する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】酸化物絶縁層上に膜厚が1nm以上10nm以下の第1の酸化物半導体層を形成し、加熱処理により結晶化させ、第1の結晶性酸化物半導体層を形成し、その上に第1の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を形成する。

(もっと読む)

半導体装置のレイアウト方法及びその半導体装置

【課題】トランジスタのしきい電圧の変化を減らすことにより、半導体装置の信頼性を向上させることができる半導体装置のレイアウト方法及びその半導体装置を提供する。

【解決手段】半導体基板内に形成された少なくとも1つの第1電極と第2電極を有する複数個のトランジスタのアクチブ領域を配置する段階と、前記複数個のトランジスタのアクチブ領域のそれぞれの少なくとも1つの第1電極と第2電極との間に位置し、前記半導体基板上に所定の幅と長さを有する1つ以上の実質的に同一間隔に分離された前記複数個のトランジスタのゲートを配置する段階と、前記複数個のトランジスタの間に、所定の幅と長さを有し、前記半導体基板上に前記複数個のトランジスタの分離されたゲートの間隔と実質的に同一間隔に配置された複数個のダミーゲートを配置する段階とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

61 - 80 / 588

[ Back to top ]