Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

341 - 360 / 1,113

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

酸化マンガン膜の形成方法、半導体装置の製造方法および半導体装置

【課題】 Cuとの密着性を良好とすることが可能な酸化マンガン膜の形成方法を提供すること。

【解決手段】 酸化物102上にマンガンを含むガスを供給し、酸化物102上に酸化マンガン膜103を形成する酸化マンガン膜103の形成方法であって、酸化マンガン膜103を形成する際の成膜温度を、100℃以上400℃未満とする。

(もっと読む)

表示装置及び表示装置製造方法

【課題】表示装置の薄膜トランジスタ基板において、窒化ケイ素膜上への銅の微細配線を、より簡易に行う。

【解決手段】微細配線がされたTFT基板は、無アルカリガラスからなるガラス基板101と、インジウム錫酸化物からなる透明導電膜102と、アルミニウムを4原子%含有し銅を主成分とする合金からなる第一の導電層103及び109と、99.99%純度の純銅からなる銅配線である第二の導電層104及び110と、窒化ケイ素からなるゲート絶縁膜106と、非晶質ケイ素からなる半導体層107と、n+型非晶質ケイ素からなるコンタクト層108と、透明導電膜102と第一の導電層103との界面の金属酸化物層105と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】ショットキーバリアダイオード100は、GaNを含む半導体層1と、ショットキー電極2とを備えている。ショットキー電極2は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成された、W、TiW、WN、TiN、およびTaよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部に対するウエルコンタクトホールの位置合わせ精度を向上する。

【解決手段】半導体基板にウエル領域2を形成する第1の工程と、前記半導体基板に、第1のアライメントマークと、前記ウエル領域2にアクティブ領域を分離する素子分離部7とを形成する第2の工程と、前記半導体基板の上に、第2のアライメントマークと、MOSトランジスタのゲート電極9とを形成する第3の工程と、前記ゲート電極9とともにソース電極又はドレイン電極となるべき半導体領域を形成する第4の工程と、前記半導体基板及び前記ゲート電極9の上に絶縁膜14を形成する第5の工程と、前記第1のアライメントマークを基準として決められた位置に、ウエルコンタクトホールを形成する第6の工程と、前記第2のアライメントマークを基準として決められた位置に、前記絶縁膜14を貫通するコンタクトホールを形成する第7の工程とを備える。

(もっと読む)

半導体装置及びその製造方法

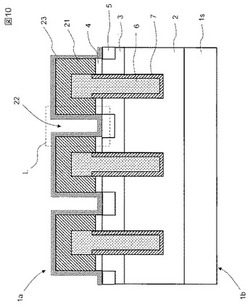

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置の製造方法及び半導体基板

【課題】表面に段差部分を有する構造物を覆う上部絶縁膜を基板全面に亘って均一に表面平坦化し、上部絶縁膜の表面平坦化及び膜厚均一化を共に実現して、所期の半導体素子を安定且つ確実に形成する。

【解決手段】半導体基板1上に、多層配線構造の下層部分2を適宜形成した後、半導体基板1のベベル部1aを覆うように、下層部分2と略同等の膜厚に縁部絶縁膜14を形成し、上部絶縁膜11aをCMPで表面研磨して平坦化する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、Ru膜上にCVD法によりCu膜を成膜するにあたり、チャンバー1の壁部の温度を、副生成物であるCu(hfac)2の蒸気圧が成膜処理時のチャンバー1内の圧力と等しくなる温度以上で成膜原料であるCu(hfac)TMVSの分解温度未満に制御する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の局所配線を簡単な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に局所配線構造を形成する際に、半導体素子の2つの導電領域を絶縁している絶縁領域に、この2つの導電領域を接続するようにシリコン膜104又は第1金属膜109を形成し(第1工程)、形成されたシリコン膜又は第1金属膜上に無電解めっき法により選択的に第2金属膜110を形成する(第2工程)。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】キャパシタの表面積を増大させて容量が増加した有機電界発光表示装置及びその製造方法。

【解決手段】薄膜トランジスタ及びキャパシタ領域を含む基板と;バッファー層と;トランジスタ領域に位置する金属触媒を利用して結晶化した半導体層パターンと;ゲート絶縁膜と;前記パターンの一定領域に対応されるゲート電極及びキャパシタ領域のキャパシタ下部電極と;層間絶縁膜と;前記パターンと一部が連結されるソース/ドレイン電極及びキャパシタ下部電極に対応される上部電極と;同じく層間絶縁膜上のソース/ドレイン電極と電気的に連結される第1電極と;発光層を含む有機膜層;及び第2電極をこの順で含み、キャパシタ領域に対応されるバッファー層、ゲート絶縁膜、及び層間絶縁膜の一定領域、キャパシタ下部電極、及びキャパシタ上部電極の表面には半導体層パターンを形成する結晶粒の結晶粒界及びシードの形状と一致する形状の突出部を形成する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】容量素子の酸素雰囲気中での焼結を制限を設けず実施した場合も、スタックコンタクトの信頼性や製造歩留まりを向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1と、その上に形成された第1の層間絶縁膜1,2および第2の層間絶縁膜3,4,5と、第1の層間絶縁膜1,2中に形成された第1のプラグ8bおよび第2のプラグ8aと、第2の層間絶縁膜3,4,5中に形成され第1のプラグ8bと接続された容量素子たるメモリセル30と、第2の層間絶縁膜3,4,5中に形成され第2のプラグ8aと接続された第3のプラグ19とを備え、第2のプラグ8aの中央部の上面は第1の層間絶縁膜1,2の上面よりも半導体基板1側に位置するように構成する。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】ウエハW上の絶縁膜にビアホールとトレンチを形成し、この上にバリア層としてCVD−Ru膜を成膜する。チャンバー1内にウエハWを収容し、チャンバー1内に1価Cuβジケトン錯体であるCu(hfac)TMVSと、これを還元するアンモニア、還元性Si化合物、カルボン酸などの還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー内にウエハを搬入し、安定化させた後、ウエハを加熱しつつチャンバー内にCu錯体からなる成膜原料を気相状態で導入してウエハ上にCVD法によりCu膜を成膜し、成膜後、チャンバー内をパージして残留ガスを除去し、その後、チャンバーから基板を搬出するCu膜の成膜方法を実施するにあたり、パージの際に、ウエハへの入熱をCu膜成膜の際よりも低下させる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

スルーシリコンビア(TSV)内にチップ−チップ間、チップ−ウェハー間及びウェハー−ウェハー間の銅インターコネクトを電着するプロセス

シリコン基板内のビア内に高純度の銅を電着し、スルーシリコンビア(TSV)を形成するプロセスである。本プロセスは、電解銅めっきシステム内の電解槽内にシリコン基板を浸漬するステップと、高純度の銅を電着してTSVを形成するのに十分な時間の間、電圧を印加するステップとを含み、電解槽が酸、銅イオンの発生源、第一鉄イオン及び/又は第二鉄イオンの発生源、及び析出した銅の物理−機械的特性を制御するための少なくとも1つの添加剤とを含み、銅金属の発生源からの銅イオンを溶解することによって電着されることになる付加的な銅イオンを提供するために、前記槽内でFe2+/Fe3+レドックス系が、確立される。 (もっと読む)

341 - 360 / 1,113

[ Back to top ]