Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

261 - 280 / 1,113

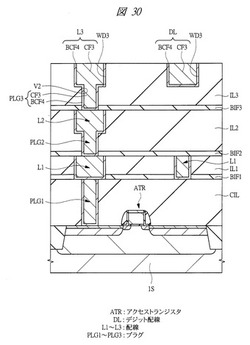

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】酸化物半導体をチャネル形成領域に用いたトランジスタを有する半導体装置の作製において、酸化物半導体膜を形成した後、水分、ヒドロキシ基、または水素などを吸蔵或いは吸着することができる金属、金属化合物または合金を用いた導電膜を、絶縁膜を間に挟んで酸化物半導体膜と重なるように形成する。そして、該導電膜が露出した状態で加熱処理を行うことで、導電膜の表面や内部に吸着されている水分、酸素、水素などを取り除く活性化処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

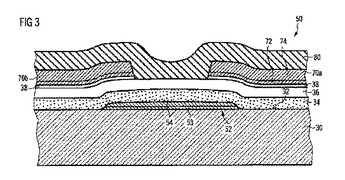

半導体デバイスを製造する方法および設備と半導体デバイス

半導体デバイスを生産する方法が提供され、この半導体デバイス(50)は、基板(30)と、半導体層(36、38)と、基板および半導体層から選択された少なくとも1つの要素に隣接する少なくとも1つのメタライゼーション層(52、70)とを含み、この方法は、基板および半導体層から選択された少なくとも1つの要素の近くに酸素を含む少なくとも1つのメタライゼーション層を形成するステップを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 高信頼性を有するデュアルダマシン構造を用いた半導体装置及びその製造方法を提供することができる。

【解決手段】 半導体基板上に形成された第一の絶縁膜と、前記第一の絶縁膜に形成されたコンタクトと、前記第一の絶縁膜上に形成され、前記第一の絶縁膜よりも誘電率の低い第二の絶縁膜と、前記第二の絶縁膜に形成され、前記コンタクトと電気的に接続される配線とを備え、前記コンタクト底面及び、前記配線の側面に第一のバリアメタルが形成され、前記コンタクト側面及び前記第一のバリアメタル上に第二のバリアメタルが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

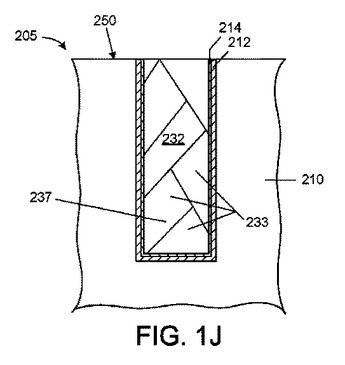

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

金属酸化膜の成膜方法、酸化マンガン膜の成膜方法及びコンピュータ読み取り可能な記憶媒体

【課題】 Cuとの密着性を良好とすることが可能な金属酸化膜の成膜方法を提供すること。

【解決手段】 下地上に有機金属化合物を含むガスを供給し、下地上に金属酸化膜を成膜する金属酸化膜の成膜方法であって、下地上に有機金属化合物を供給して下地上に金属酸化膜を成膜し(工程2)、かつ、金属酸化膜の成膜プロセスの最後に、金属酸化膜を酸素含有ガス又は酸素含有プラズマに曝す(工程4)。

(もっと読む)

半導体装置の製造方法

【課題】溝側面に側壁膜を形成する際に、側壁膜表面にエッチングダメージを受けることなく、側壁膜上面の溝開口部からの深さのばらつきを抑制して形成可能な方法を提供する。

【解決手段】半導体基板主表面に形成された溝の側壁に第1の層を形成する工程、溝を保護膜で埋設する工程、保護膜の表面の高さが溝の開口部よりも低い位置になるようにドライエッチング法でエッチバックし、該エッチバックにより露出した第1の層をエッチング除去する工程、とを含む半導体装置の製造方法。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

スパッタリング装置およびスパッタリング方法並びに成膜システム

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料の埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、スパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマ22を磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34BとAlターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってAlターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al堆積膜200のカバレッジ性が、プラズマ放電電流ID、ターゲットバイアス電圧VB、および、ターゲット−基板間距離Lに基づいて調整される。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

261 - 280 / 1,113

[ Back to top ]