Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

241 - 260 / 1,113

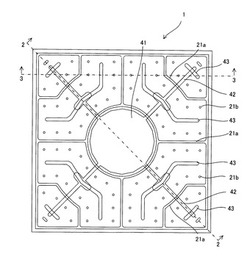

半導体発光装置

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

薄膜の製造方法

【課題】本発明は、薄膜材料となる微粒子を分散した液体を、被処理部材の表面に塗布して薄膜を製造する方法であって、均一な薄膜を製造する方法の提供を目的とする。

【解決手段】金属または半導体を含む薄膜の製造方法であって、溝(または凹部)4を有する被処理部材10の表面に、金属の微粒子、半導体の微粒子、金属の酸化物を含む微粒子、および半導体の酸化物を含む微粒子、のうちの少なくともいずれかを溶媒中に分散した液体8を塗布する塗布工程と、被処理部材10の表面に塗布した液体8の溶媒を揮発させる第1の熱処理工程と、マイクロ波を照射することにより、溶媒を揮発させた液体8に分散された微粒子を加熱し、液体8に含まれる微粒子または液体8に含まれる微粒子の成分で溝(または凹部)4を埋める第2の熱処理工程と、を備えたことを特徴とする薄膜の製造方法が提供される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

金属膜を埋め込む工程を有する電子部品の製造方法

【課題】金属膜を埋め込む工程を有する電子部品の製造方法を提供する。

【解決手段】複数のマグネットが多角形格子の格子点の位置にかつ隣接するマグネットが異極性となるように配置された磁石ユニットによりターゲット表面に磁場を形成させながら、PCMスパッタリング法により、凹部が形成された被処理体に窒化チタンを含むバリア層を成膜する第1の工程と、前記バリア層上に直接低融点金属層を、前記低融点金属層が流動可能な温度条件下で充填する第2の工程と、を有することを特徴とする電子部品の製造方法。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

半導体装置

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む金属窒化物含有多結晶金属層32からなるバリア層と、これに積層された金属層31とを有している。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法および基板処理装置

【課題】低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】基板上に形成された絶縁膜と、絶縁膜に隣接して設けられた金属膜と、を有し、金属膜は、第1の金属膜と第2の金属膜との積層構造を有しており、第1の金属膜は第2の金属膜よりも耐酸化性が高い物質で構成され、第2の金属膜は4.8eVよりも高い仕事関数を有する第1の金属膜とは異なる物質で構成され、第1の金属膜は第2の金属膜と絶縁膜との間に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】最近の多層メタルスパッタリング成膜プロセスにおいては、従来のマルチチャンバ型の装置に代わって、単一チャンバ&マルチ成膜サイト型の装置が広く使用されるようになっている。しかし、本願発明者が検討したところによると、このような単一チャンバ&マルチ成膜サイト型スパッタリング成膜装置は、磁性メタル膜と非磁性メタル膜を積層形成する場合は、被処理ウエハを別の成膜サイトに移送して成膜する必要があり、スループットを大きく低下させていることが明らかとなった。

【解決手段】本願発明は、単一チャンバ&マルチ成膜サイト型多層スパッタリング成膜装置を用いた半導体装置の製造方法において、少なくとも一つの成膜サイトにおいて、磁性および非磁性ターゲットの両方を切り替えて用い、磁性および非磁性膜の両方の膜を成膜するものである。

(もっと読む)

密着性を改良するための基板のプラズマアニーリング

【課題】許容可能な拡散バリア特性と基板への密着性を耐熱性金属窒化物が有するように、基板上への窒化チタンなどの耐熱性金属窒化物膜の形成を提供する。

【解決手段】材料の層が、ウェハ上に部分的に形成された集積回路内の基板上に形成される。基板はプラズマアニールを受け、その間に基板はイオンでボンバードされる(工程300)。プラズマアニールは、エネルギーを注入された窒素含有ガスから生成されたプラズマへ基板を曝すことにより実行できる。基板がプラズマアニールされた後、耐熱性金属窒化物の層が基板上に堆積される(工程301)。耐熱性金属窒化物の層は、次に、第1セットのイオンでボンバードされる。第1セットのイオンによる耐熱性金属のこのボンバードは、プラズマアニールを実行することにより達成できる。耐熱性金属窒化物は、更に、第2セットのイオンによりボンバードされる(工程302)。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

半導体素子及びその製造方法

【課題】埋め込みビットラインコンタクトホール内にディフュージョンバリアーを形成して素子の特性を改善する。

【解決手段】半導体基板100をエッチングして複数個のピラーパターンを形成する段階と、前記ピラーパターンの表面に絶縁層を蒸着する段階と、前記ピラーパターンの一側の前記絶縁層の一部を除去して前記ピラーパターンが露出されるコンタクトホールを形成する段階と、前記コンタクトホール内にバリアー膜170aを形成する段階と、前記コンタクトホールと接する前記ピラーパターン内に接合180を形成する段階と、前記ピラーパターンの間の底部に前記コンタクトホールと接続して形成された埋め込みビットラインとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

241 - 260 / 1,113

[ Back to top ]