Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

221 - 240 / 1,113

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

低抵抗率およびロバストな微接着特性を有するタングステン薄膜の成膜方法

【課題】良好な均一性、および下部層に対して良好な接着性を有する低抵抗率のタングステン膜を形成する方法が提供される。

【解決手段】低温下でパルス核生成層プロセスを用いてタングステン核生成層を形成する。その後、バルクタングステン充てん物を堆積させる前に、成膜された核生成層を処理する。本処理により、堆積されるタングステン成膜の抵抗率が低減される。ある実施形態では、核生成層の成膜は、水素を利用せずに、ホウ素ベースの化学作用により行われる。またある実施形態では、処理は、核生成層を、還元剤およびタングステン含有前駆体の交互のサイクルに曝す工程を含む。

(もっと読む)

広バンドギャップショットキー障壁デバイス用の多層拡散障壁

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

パワー素子を備えた半導体装置の製造方法

【課題】電子線照射等の後に行う水素アニール時に水素が十分にデバイスを構成する半導体のダメージ部分まで到達し、ダメージ回復が行えるようにすると共に、表面電極の劣化を抑制することができるようにする。

【解決手段】IGBTが形成されたセル領域全面に形成された表面電極11に含まれるバリアメタル12の第1金属膜12aをチタン(Ti)ではなく、ニッケル(Ni)やコバルト(Co)等のVIII族の金属材料により構成する。これにより、水素アニールの際に、電子線照射等によってダメージを受けたシリコン表面に水素が到達するようにできる。また、バリアメタル12の第1金属膜12aを構成する金属材料が水素と結合しないようにできる。したがって、水素アニール時に水素が十分にシリコン表面のダメージ部分まで到達し、ダメージ回復が行えるようにすることができると共に、表面電極11の劣化を抑制することができる。

(もっと読む)

表示装置および表示装置の製造方法

【課題】Cu合金をソース・ドレイン電極に用いたTFTにおいて、コンタクト膜に対して酸化処理を施す場合であっても、良好なオン特性を維持する表示装置を提供することを目的とする。

【解決手段】半導体層4と、銅と1種類の添加元素とを含む銅合金層を有するソース電極10およびドレイン電極9と、ソース電極10及びドレイン電極9のそれぞれの電極と半導体層4との間に形成されるコンタクト膜5と、それぞれの電極とコンタクト膜5との間に形成される酸化物膜8と、を含む薄膜トランジスタ基板を有する表示装置であって、コンタクト膜5は、不純物とシリコンとを含み、酸化物膜8は、シリコン、不純物および酸素を含むとともに、酸化物膜8における不純物濃度がコンタクト膜5における不純物濃度よりも低い、ことを特徴とする表示装置。

(もっと読む)

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

半導体処理システムのための前駆物質を生成する方法及び装置

【課題】半導体処理システム(320)の前駆物質を生成する装置を提供する。

【解決手段】装置は、側壁(402)、上部、底部を有するキャニスタ(300)を含んでいる。キャニスタ(300)は、上の領域(418)と下の領域(434)を有する内容積(438)を画成している。一実施形態においては、装置は、更に、キャニスタ(300)を部分的に取り囲んでいるヒータ(430)を含んでいる。ヒータ(430)によって、上の領域(418)と下の領域(434)間に温度勾配が生じる。また、精製ペンタキス(ジメチルアミド)タンタルから原子層堆積によってバリヤ層、例えば、窒化タンタルバリヤ層を形成する方法も特許請求される。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチパワーDMOSトランジスタにおいて、ソース引き出し電極とゲート引き出し電極の短絡を確実に防止する。併せて上記DMOSトランジスタのサイズの縮小を図ること及びソース・ドレイン間絶縁破壊電圧VDSの低下を防止する。

【解決手段】N+型ソース層13の底面の直下のP型ベース層9内に形成されたP+型コンタクト層14を、コンタクト用開口25の内の少なくとも一部の該コンタクト用開口25の底面に露出するN+型ソース層13を貫通するくぼみ部16に露出させる。次にコンタクト用開口25の底面に露出するN+型ソース層13及びくぼみ部16に露出するN+型ソース層13、P+型コンタクト層14に接続し、コンタクト用開口25内をその上端まで埋設して延在するソース引き出し電極17aを形成する。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

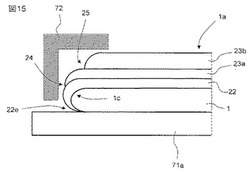

半導体発光装置

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

221 - 240 / 1,113

[ Back to top ]