Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

521 - 540 / 620

エピタキシャル基板および半導体素子

【課題】逆方向耐圧を向上可能な構造を有するIII族窒化物半導体素子を提供する。

【解決手段】ショットキダイオード11では、p型の窒化ガリウム支持基体13は、第1の面13aと第1の面の反対側の第2の面13bとを有しており、1×1017cm−3を超えるキャリア濃度を示す。p型の窒化ガリウムエピタキシャル層15は、第1の面13a上に設けられている。オーミック電極17は、第2の面13b上に設けられている。ショットキ電極19は、窒化ガリウムエピタキシャル層15に設けられている。窒化ガリウムエピタキシャル層15の厚さD1は5マイクロメートル以上1000マイクロメートル以下である。また、窒化ガリウムエピタキシャル層15のキャリア濃度は、1×1014cm−3以上1×1017cm−3以下である。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び液晶表示装置

【課題】

本発明は、アルミ二ウム配線で発生するヒールロックを減少させる、薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】

本発明による薄膜トランジスタ基板は、下部アルミ二ウム層と、前記下部アルミ二ウム層の上に形成されている窒化アルミ二ウム層と、前記窒化アルミ二ウム層の上に形成されている上部アルミ二ウム層を含むことを特徴とする。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

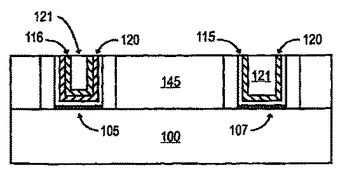

CMOSデバイスの自己形成金属シリサイド化ゲート

【課題】 CMOSデバイスの自己形成金属シリサイド化ゲートを提供すること。

【解決手段】 シリサイドが自己形成され(すなわち、別個の金属/シリコン反応ステップを必要とせずに形成され)、シリコン材料のCMP又はエッチ・バックを必要としない、金属シリサイド・ゲートをFETデバイスに形成するためのプロセス。第1のシリコン材料層(3)(ポリシリコン又はアモルファス・シリコン)が、ゲート誘電体(2)の上に形成され、次いで、金属層(4)が第1のシリコン材料層(3)の上に形成され、金属層(4)の上に第2のシリコン材料層(5)が形成される。その後、ソース/ドレイン活性化アニールのような高温(700℃より高い)処理ステップが実施され、このステップは、金属層(4)の金属を第1のシリコン材料層(13)におけるシリコン材料と反応させることにより、ゲート誘電体(2)の上にシリサイド層(30)を形成するのに有効である。第2の高温処理ステップ(ソース/ドレインのシリサイド化のような)を実施することができ、これは第2のシリコン材料層(5)におけるシリコン材料から第2のシリサイド層(50)を形成するのに有効である。シリサイド層の厚さは、高温処理において、第1のシリコン材料層の実質的にすべて及び第2のシリコン材料層の少なくとも一部が、シリサイド材料で置き換えられるような厚さである。従って、完全シリサイド化ゲート構造体を生成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 パッド電極下に能動層が配置されている場合においても、パッド電極下における密着性を確保しつつ、バリアメタル構造を能動面上に安定して形成できるようにする。

【解決手段】 不純物拡散層5a、5bの表面が覆われるようにして層間絶縁膜6上にバリアメタル膜8を形成し、フォトリソグラフィー技術を用いることにより、開口部7が覆われるようにしてパッド電極16下に配置されるバリアメタル膜8の表面を露出させるレジストパターンRを形成し、レジストパターンRをマスクとして、バリアメタル膜8をエッチングすることにより、パッド電極16下に配置される層間絶縁膜6上のバリアメタル膜8を除去し、バリアメタル膜8を介してゲート電極4および不純物拡散層5a、5bに接続された配線層9を層間絶縁膜6上に形成し、ゲート電極4および不純物拡散層5a、5b上に配置されたパッド電極16を形成する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 微細な電極パターンを容易に実現し、かつ基材表面と電極パターン表面とが同一平面となるように形成することにより、電極の上部に積層する絶縁膜を薄膜化することができ、その結果トランジスタの駆動電圧を下げることが出来る薄膜トランジスタの製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタの製造方法は、基材表面に電極のパターンと同一形状の溝である凹部を形成する工程と、該凹部に対して電極材料を埋め込み、基板表面と同一の高さの埋め込み電極を形成する工程とを有する。

(もっと読む)

電子デバイス及びその製造方法

【課題】 通常の製造工程に対して新たな工程を追加することなく、電子デバイスに固有の認識番号を信頼性高く付与できるようにする。

【解決手段】 半導体素子アレイは、一対のソース領域及びドレイン領域となる活性領域1と、活性領域1上に形成され且つワードラインとなるゲート電極2とから構成される複数のアクセストランジスタを有している。活性領域1はOD細線1aを有すると共に、OD細線1aを含む活性領域1の表面はシリサイド化されている。製造工程時におけるOD細線1aのシリサイド化層の断線に起因する不連続な抵抗上昇に基づいて固有認識番号が設定される。

(もっと読む)

表示装置用配線、該配線を有する薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗特性及び信頼性を同時に確保する。

【解決手段】導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する表示装置用配線と、基板110、該基板110上に形成されているゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されているソース電極173を含むデータ線171及びソース電極173と対向しているドレイン電極175、及びドレイン電極175と接続されている画素電極190を有している。ゲート線とデータ線171及びドレイン電極175の少なくとも一方とは、導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する。これにより、配線の密着性が向上するので剥離を防止することができ、信頼性が向上する。

(もっと読む)

ショットキー障壁貫通単電子トランジスタ及びその製造方法

【課題】PADOXのような工程を用いず、トンネル障壁の高さ及び幅を人為的に調節することができる上、電流駆動能力をさらに向上させることができるショットキー障壁貫通単電子トランジスタ及びその製造方法の提供。

【解決手段】ショットキー障壁貫通単電子トランジスタは、基板100上に形成された絶縁層110と、ソース/ドレイン領域120a/120bの少なくとも一部分はシリサイド化されてチャネル領域120bとショットキー接合される。また、ゲート絶縁膜130、ゲート電極140、側壁絶縁膜150、層間絶縁膜パターン160、及び露出した前記ゲート電極140及び前記ソース/ドレイン電極120a/120b上に形成された金属配線170を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 高誘電率絶縁膜を用いて、閾値電圧の変動を低減することのできる半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板5の上に形成されたゲート絶縁膜9は、高誘電率絶縁膜を含む絶縁膜である。MOSFETのうちで、ゲート長およびゲート絶縁膜が同一であるものは、チャネル幅がWである単一のチャネルまたはチャネル幅がWであるチャネルを複数並列した構造を有する。また、チャネル幅の異なるMOSFETの素子分離領域6の端部における曲率が異なる。この場合、素子分離領域6の表面は実質的に同一面をなし、且つ、素子分離領域6の表面から底面までの深さが異なっていることが好ましい。

(もっと読む)

電子回路基板とその製造方法及び電子回路基板を用いた表示装置

【課題】繰り返し折り曲げても断線不良の起きない、接続信頼性が高いフレキシブル基板及びその製造方法、さらにその基板を用いた表示装置を提供する。

【解決手段】フレキシブル性を有するデバイスであって、基板に形成される金属配線12の少なくとも一部が導電性高分子により覆われている。具体的には、基板11上に金属の配線12を形成し、その配線上を覆うように導電性高分子の配線13を形成し、金属配線12と導電性高分子配線13とを多層構造にする。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】AlGaN層の表面を平坦とし、かつ、AlGaN/GaN界面に存在する二次元電子ガスにダメージを与えない半導体装置の製造方法を提供する。

【解決手段】先ず、サファイア又は炭化珪素で形成される支持基板12を用意して、支持基板上にバッファ層14を堆積させる。次に、支持基板及びバッファ層を900℃以上1100℃以下に設定された成長温度に保持した状態で、バッファ層上に、GaN層16及びAlGaN層20を順次に積層してGaN半導体基板10を形成する。GaN半導体基板を形成する工程に引き続いて、GaN半導体基板を500℃以上成長温度以下の温度に保持した状態で、AlGaN層の上側表面28上に、表面保護膜としてAlN層30を形成する。

(もっと読む)

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

導電性パターンの形成方法

【課題】 より簡便に比較的厚さが大きく、インクの着弾径より小さな線幅でも着弾痕のない導電性パターンを得る形成方法を提供することにある。

【解決手段】 撥液剤80は、前述したようにバンク上面12eにおいて、水に対して110°以上の高い接触角を備えているため、導電性液状材料11に対しても接触角θは大きい。一方、バンク溝部20は前述したように親水性となっているために、基板10に到達した導電性液状材料11は、バンク上面12eに配設されている撥液剤80から圧縮力を受け、逆にバンク溝部20からは張力を受ける。このために、導電性液状材料11はバンク溝部20の溝に沿って、同図紙面の垂直方向の前後に広がっていくことができる。また、バンク溝幅Bが液滴の大きさDより大きい場合は、より安定して導電性液状材料11をバンク溝部20の中へ収容することができる。

(もっと読む)

TFT基板

【課題】生産性を向上するTFT基板の提供。

【解決手段】ゲート電極上でゲートパッドを露出の絶縁膜パターン、ゲート電極及び絶縁膜パターン上に形成の半導体膜パターン、ゲート電極上の半導体膜パターンと接触の不純物注入半導体膜パターン、半導体膜パターン上に形成のソース及びドレイン電極とデータライン、ソース及びドレイン電極上且つゲートパッド領域で絶縁膜パターン上に形成の保護膜パターン、保護膜パターン上でドレイン電極に連結の第1画素電極パターンと、ゲートパッドに連結の第2画素電極パターンを備え、絶縁膜及び保護膜パターンはゲートパッド領域で重なり、ゲート電極、パッド及びラインは第1金属膜パターンと第1金属膜パターン上の第2金属膜パターンを含み、第2金属膜パターンの厚さは第1金属膜パターンに対し同じ又は薄く、第1金属膜パターンの幅は第1金属膜パターンの底から狭くなる。

(もっと読む)

配線基板及び半導体装置の作製方法

【課題】少ない工程数で大面積基板に微細な形状を有する配線を形成する方法を提供する。また、少ない工程数及び原料の削減により、コスト削減及びスループットの向上が可能であり、かつ微細構造の半導体素子を有する半導体装置の作製方法を提供する。

【解決手段】金属粒子と有機樹脂とで形成される液状物質にレーザ光を照射し、金属粒子の一部を溶融した後、レーザ光が照射されない液状物質を除去して、配線、電極等に代表される導電層を基板上に形成することを特徴とする。また、本発明は、上記焼結された導電層を配線又は電極として有する半導体装置を形成することを特徴とする。

(もっと読む)

配線パターン形成方法および配線パターン

【課題】液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】基板10Aの表面Sにヘキサメチルシラザンを基板10Aの表面Sに塗布し、HMDS層12を形成するヘキサメチルシラザン層形成工程と、HMDS層12上に、有機感光性材料層を形成する有機感光性材料層形成工程と、前記有機感光性材料層をパターニングしてバンクパターン18を形成する工程と、バンクパターン18によって縁取られた領域に、インクジェット法を用いて、導電性材料を付与する導電性材料付与工程と、を含んでいる。

(もっと読む)

521 - 540 / 620

[ Back to top ]