Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

581 - 600 / 620

薄膜トランジスタ表示板及びその製造方法

【課題】 抵抗が低く、画素電極または半導体層との接触性が優れた配線を有する薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明は、液晶表示装置または有機発光表示装置用薄膜トランジスタ表示板の配線に関し、モリブデン(Mo)にニオビウム(Nb)、バナジウム(V)またはチタニウム(Ti)を所定量含むモリブデン合金層とアルミニウム層の積層構造を形成することによって、既存の純粋モリブデン(Mo)を使用した場合に比べて、モリブデン合金層とアルミニウム層の相対的なエッチング速度の差が減少し、エッチング工程時におけるアンダーカット、オーバーハング及びマウスバイトなどが発生しない。更に、半導体層または画素電極との接触特性も改善されたことを特徴とする低抵抗性及び耐薬品性を同時に有する薄膜トランジスタ表示板及びその製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、高誘電体材料膜を選択的に容易にエッチングできるようにすること。

【解決手段】シリコン基板104の上に、少なくとも高誘電体材料膜106を含む絶縁膜106,111を形成し、絶縁膜106,111上にゲート電極層109を形成し、ゲート電極層109をパターニングしてゲート電極109を形成し、ゲート電極109以外の高誘電体材料膜106を、フッ素化合物を含む強酸水溶液で除去する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 発振することなく動作の安定した半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板21上に複数のトランジスタを隣接して配置し、前記複数のトランジスタのゲート22をゲートバー22aで共通に接続するとともに、前記複数のトランジスタのソースフィンガー24bを共通に接続するソース配線24を前記複数のトランジスタ上に設け、前記ソース配線は前記ゲートバーの一部のみを跨ぐ互いに離間した複数のブリッジ部24aを有する。ゲートバー22aの一部のみをソース配線24が跨ぐので、ゲートバー・ソース容量を減らせることができ、高周波でのインピーダンスが大きくなって、トランジスタに帰還経路が実質的に形成されない。

(もっと読む)

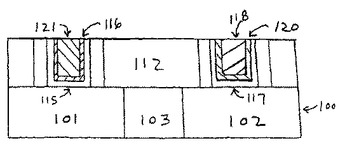

電子装置

多層構造の電子装置を形成する方法であって、横に延びる第1層に断面を規定するステップと、前記第1層の最上部に少なくとも1つの非平坦層を堆積させて、該非平坦層の表面の断面が前記横に延びる第1層の断面と同じにするステップと、前記非平坦層の最上部に少なくとも1つの追加層のパターンを堆積させて、該追加層の横位置が前記非平坦層の断面の形状によって規定されて該追加層が前記第1層の断面と外側で整合するステップとを備える。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】エピタキシャル成長法により半導体層を形成する際の加工寸法誤差を少なくすることができる半導体素子の製造方法を提供する。

【解決手段】有機金属化合物を含有する感光性ペーストを塗布した後ベークして、基板1上に感光性マスク層を形成する。この感光性マスク層をフォトリソグラフィによりパターニングし、更に酸化処理又は還元処理して、基板1上に金属酸化物を主成分とするエピタキシャルマスク4を形成する。そして、基板1表面のエピタキシャルマスク4が形成されていない領域上にダイヤモンドをエピタキシャル成長させて、半導体ダイヤモンド層5a及び5bを形成する。エピタキシャルマスク4を除去した後、半導体ダイヤモンド層5a及び5b上に夫々ソース電極7及びドレイン電極8を形成すると共に、基板1表面におけるチャネル領域上にゲート絶縁膜6を介してゲート電極9を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能を向上させる。

【解決手段】 LDMOSFETのゲート電極30およびn+型ソース領域53上にサリサイド工程により金属シリサイド膜64を形成し、n-型オフセットドレイン領域33、n型オフセットドレイン領域51およびn+型ドレイン領域52上にはこの金属シリサイド膜を形成しない。ゲート電極30のドレイン側の側壁上には、絶縁膜を介して、シリコン膜からなるサイドウォールスペーサが形成され、このサイドウォールスペーサによりフィールドプレート電極44が形成される。フィールドプレート電極44はゲート電極30上に延在しておらず、サリサイド工程ではゲート電極30の上面の全面に金属シリサイド膜64が形成される。

(もっと読む)

アモルファスシリコン薄膜トランジスタ及びその製作方法

本発明は、アクティブマトリクスディスプレイで使用するためのアモルファスシリコン薄膜トランジスタと、その様なトランジスタを製作する方法を提供している。具体的には、本発明の或る態様では、アモルファスシリコン層の厚さとチャネル長を最適化することのできる、チャネル不活性化構造に基づく構造を有するトランジスタを提供している。本発明の別の態様では、低い閾値電圧を提供することができる接触強化層を含んでいる、薄膜トランジスタ構造が提供されている。 (もっと読む)

半導体装置

【課題】 はんだ接続用パッドを有する半導体装置において、製造工程中の熱負荷などによって発生する恐れのある、パッド部の膜剥がれを防止する。

【解決手段】 シリコン、シリコン酸化膜上に形成されるTi膜またはTi化合物膜と、はんだが接続されるNi膜(またはCu膜)との間に、両者との密着性が良好なCr膜を挿入したパッド構造とする。さらに、Ti膜またはTi化合物膜とシリコン酸化膜との界面に生じる剥離を防止するため、Cr膜がTi膜またはTi化合物膜よりも大きな面積で形成された構造とする。

(もっと読む)

CMOSデバイスのソースおよびドレインの寄生抵抗低減

ドープされた半導体基板を与えることと、pn接合部を画定するべく基板に第二ドーパントを導入することと、pn接合部に対応する容量を低減するべくpn接合部付近の基板中に中性化種を導入することとを含む、半導体系デバイスを製造するための方法である。半導体系デバイスは、第一および第二ドーパントを有する半導体基板と、中性化種とを含む。第一および第二ドーパントはpn接合部を画定し、中性化種は、pn接合部に対応する容量を低減するべくpn接合部付近の第一ドーパントの一部を中性化する。 (もっと読む)

半導体素子を備えた表示装置及びその製造方法並びにその半導体素子を備えた表示装置を搭載した電子機器

【課題】 直接描画プロセスを用いて、オン電流や動作速度の高い半導体素子を備えた表示装置を得ることを目的とする。

【解決手段】 ゲート電極を覆うように絶縁膜を形成し、絶縁膜表面の少なくともゲート電極又は配線の一部と重なる領域に有機溶剤を塗布し、絶縁膜表面に、有機溶剤が塗布され且つ残存する領域から有機溶剤が塗布されない領域にわたり、導電性の微粒子が有機溶媒に分散した流動体を液滴吐出法により吐出させた後、流動体を焼成して硬化させることによってソース及びドレイン電極を形成し、ソース及びドレイン電極間に挟まれた湾曲部において絶縁膜と接すると共にソース及びドレイン電極と接するように半導体膜を形成する。有機溶剤は、絶縁膜表面における流動体のぬれ性を高めるために塗布され、湾曲部を介して隣り合う、ソース及びドレイン電極それぞれの端部は、一方は凹状に湾曲し他方は凸状に湾曲して形成される。

(もっと読む)

積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置

【課題】 印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能であって、かつ、パターン形成以外に高付加価値機能を有し、より高移動度の半導体層を有する積層構造体を廉価に提供する。

【解決手段】 エネルギーの付与によって臨界表面張力が変化する材料を含み、より臨界表面張力の大きな高表面エネルギー部3とより臨界表面張力の小さな低表面エネルギー部4との少なくとも臨界表面張力の異なる2つの部位を有する濡れ性変化層2と、この濡れ性変化層2に対して高表面エネルギー部3の部位に形成された導電層5と、濡れ性変化層2に対して少なくとも低表面エネルギー部4の部位に接して設けられた半導体層6と、を有し、濡れ性変化層2は、メチレン基を含み、側鎖に疎水性基を有する高分子材料を含むように積層構造体1を構成した。

(もっと読む)

サリサイド工程及びこれを利用した半導体素子の製造方法

【課題】サリサイド工程及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】 本発明による金属シリサイド膜の形成方法は、シリコン領域を備える基板を準備する段階と、前記基板上にシリコン層を形成する段階と、前記シリコン層と接触する金属膜を形成する段階と、前記金属膜を有する基板を熱伝達気体を採択した対流または伝導方式を使用して等温熱処理して前記少なくとも前記金属膜の一部を金属シリサイド膜に転換する段階と、を含む。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

ゲート誘電体と、アルミナイドを含む金属ゲート電極とを有する半導体デバイスについて示した。  (もっと読む)

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

有機半導体装置

【課題】 高移動度を有するN型有機トランジスタ、さらには電子をキャリヤとする高性能の有機半導体装置を実現するための電極を提供することを目的とする。

【解決手段】 有機半導体層40と、有機半導体層との電気的接点を構成する電極であって、該有機半導体への電子の注入効率を高めるため、該電極、又は有機半導体と接する側の電極の一部が、該有機半導体を構成する分子材料と同一又は類似のイオン化エネルギーを持つ電子受容性分子材料に、電子供与性分子材料を組み合わせることによって導電性電荷移動型錯体を形成した電極2、3とを少なくとも有する有機半導体装置によって解決される。

(もっと読む)

配線基板、薄膜トランジスタ、表示装置及びテレビジョン装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置の作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明の配線基板の作製方法の一は、被処理物を有する第1の領域を形成し、一部の被処理物表面を改質して、第1の領域と境界線を有する第2の領域を形成し、境界線を越えて第1の領域の一部、及び第2の領域に連続的に導電性材料を含む組成物を吐出し、組成物を固化して導電層を形成し、境界線を越えて第1の領域の一部に形成された導電層を除去する。

(もっと読む)

コンタクトホールの形成方法、回路基板の製造方法、及び、電気光学装置の製造方法

【課題】 針を用いて層間膜にコンタクトホールを形成し、導電性材料を埋め込むことで導電部を形成する場合に、導電部による導通の信頼性を備え、凸部による配線の断線を防止した、コンタクトホールの形成方法、回路基板の製造方法、及び電気光学装置の製造方法を提供する。

【解決手段】 基板20と、基板20上に設けられた第1の電極34bと、第1の電極34b上に設けられた層間膜32と、層間膜32上に設けられた第2の電極34とを備えた回路基板10に、層間膜32のコンタクトホールH内に埋め込まれて第1の電極34bと第2の電極34とを導通させる導電性材料からなる導電部300を形成する。まず、層間膜32に、針Pで機械的に孔を開けつつ、針Pに含有させた溶剤によって層間膜32を化学的に溶解することで、第1の電極34bに到達するコンタクトホールHを形成し、コンタクトホールH内に導電性材料を埋め込んで導電部300を形成する。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】パターンの解像度よりもチャネル長を短くすることが容易で、これにより低コストで取り扱い電流量を増加させることが可能な薄膜トランジスタを提供する。

【解決手段】基板3上に、ゲート電極5、これを覆うゲート絶縁膜7、このゲート絶縁膜7を介してゲート電極5を覆うチャネル層(チャネル部半導体薄膜)11がこの順またはこれと逆の順に積層され、チャネル層11の表面側と裏面側とに、ソース電極9とドレイン電極15とが分け置かれていることを特徴としている。

(もっと読む)

成膜方法、無機物膜、電子部品および電子機器

【課題】本発明の目的は、特性に優れる無機物膜を形成し得る成膜方法、かかる成膜方法により形成された無機物膜、この無機物膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、基材5上に、無機物膜8の構成材料である膜材料81’と膜材料以外の部分とで構成される化合物を膜材料前駆体80として用いて、化学的気相成膜法により無機物膜8を形成する成膜方法であり、膜材料前駆体80を収納した収納部7と、基材5とを空間を介して対向させた状態で、膜材料前駆体80をガス状またはミスト状として、基材5に向かって供給し、前記空間において、ガス状またはミスト状の膜材料前駆体81を加熱して、基材5に到達する前に、その少なくとも一部を熱分解させて、膜材料以外の部分を分解・除去することにより、膜材料81’を前記基材に到達させて無機物膜8を形成させるものである。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

581 - 600 / 620

[ Back to top ]