Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

541 - 560 / 620

薄膜トランジスタ及びこれを採用した平板表示装置

【課題】薄膜トランジスタ及びこれを採用した平板表示装置を提供する。

【解決手段】ゲート電極と、これと絶縁されたソース電極及びドレイン電極と、ゲート電極と絶縁され、ソース電極及びドレイン電極と電気的に接続された有機半導体層と、ゲート電極をソース電極及びドレイン電極または有機半導体層と絶縁させる絶縁層とを備え、ソース電極及びドレイン電極と有機半導体層との間にルイス酸化合物を含有する電子受容層を有する薄膜トランジスタ及びこれを採用した有機電界発光素子である。これにより、低電界でも電荷蓄積が容易になる半導体層にチャンネルドーピングの効果を与え、エネルギー障壁特性を排除でき、チャンネルに注入されるキャリアの量を増加させることにより、結果的に接触抵抗の減少、キャリア注入増加及び電荷移動度の増加効果を有する薄膜トランジスタが得られる。

(もっと読む)

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 様々なパターンを有するゲート電極をフルシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に、第1のゲート電極40および第1のゲート電極よりもゲート長またはゲート幅が大きい第2のゲート電極40を形成し、第2のゲート電極の厚みが第1のゲート電極の厚みよりも薄くなるように第2のゲート電極の上部を選択的にエッチングまたは研磨し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の全部をシリサイド化することを具備している。

(もっと読む)

MIS型半導体装置およびMIS型半導体装置の製造方法

ゲート絶縁膜に高誘電率膜を用いるMOSFETにおいて、基板−高誘電率膜間の低誘電率層(シリコン酸化膜)を増大させないようにするために、基板(1)上に高誘電率膜(3)、拡散バリア層(4)を堆積した後、高誘電率膜(3)の膜質改善のための熱処理を行う。次に、ゲート電極材料膜を堆積し、これをパターニングしてゲート電極(6)を形成する。このエッチング工程において、高誘電率膜3)はその側面がプラズマに曝されることにより、電荷が注入されまたダメージを受ける。この電荷を逃がしダメージを修復するために拡散バリア層(8)でゲート部を含む全面を被覆して熱処理を行う。その後、ソース・ドレイン領域となる不純物拡散層を形成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、シリサイドプロセスを適用したMOSFETにおいて、シリサイド膜をより大きく形成できるようにする。

【解決手段】たとえば、シリコン基板11の表面上に設けられたゲート電極16の側面には、それぞれ、内側ゲート側壁膜18および外側ゲート側壁膜21が形成されている。一方、ゲート電極16の形成位置を除く、シリコン基板11の表面部には、浅い低濃度拡散層17、および、二段構造の浅い高濃度拡散層19と深い高濃度拡散層22とが形成されている。そして、浅い高濃度拡散層19および深い高濃度拡散層22に対応するシリコン基板11の表面部には、それぞれの高濃度拡散層19,22の深さに応じて厚さの異なる二段構造のシリサイド膜23が形成されている。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

導電膜の形成方法、薄膜トランジスタの製造方法、電気光学装置、及び電子機器

【課題】 液相法により導電性に優れた透光性導電膜を形成する方法を提供する。

【解決手段】 導電性微粒子と分散媒とを含む分散液150を基体上に配置し、導電性微粒子を含む微粒子膜を基体上に形成し、その後に、導電性微粒子を溶解した有機溶媒151を微粒子膜上に配置し、所定の温度の熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】測定対象の収縮等が生じやすい条件下でも高い精度で測長を行うことができる半導体装置の製造方法を提供する。

【解決手段】Si基板上にレジスト膜を形成した後、レジスト膜に半導体集積回路用の回路パターン、第1のL字型測長用パターン3a,3b及び十字型のアライメント用モニタパターン4a,4bを形成し、これらのパターンに基づいて、Si基板をパターニングする。その後、Si基板の上方に、ポリSi膜を形成し、ポリSi膜上にレジスト膜を形成する。レジスト膜に半導体集積回路用の回路パターン、第2のL字型測長用パターン13a,13b及び十字型のアライメント用モニタパターン15bを形成する。このとき、第2のL字型測長用パターンが平面視で第1のL字型測長用パターンを180度回転させた方向を向くようにする。そして、これらのパターンをマスクとして、ポリSi膜をパターニングすることにより、ゲート電極を形成する。

(もっと読む)

薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法

【課題】フェムト秒レーザーを用いて薄膜を蝕刻することによって工程の単純化及び生産性の向上が図られる薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法を提供する。

【解決手段】基板上に薄膜を形成する段階と、この薄膜上部にパターン形状が定義されたマスクを整列する段階と、このマスクに定義されたパターン形状を有するように前面にフェムト秒レーザーを照射して薄膜を選択的に除去する段階とを備える。

(もっと読む)

有機トランジスタおよびその製造方法

【課題】 短チャネルで高い電気的特性を有する有機トランジスタおよびその製造方法を提供する。

【解決手段】 基板と、ゲート電極と、ゲート絶縁層と、ソース・ドレイン電極と、有機半導体層によって構成されるボトムゲート構造の有機トランジスタにおいて、ゲート絶縁膜が、ソース・ドレイン電極に近接する部分で表面エネルギーが低く、ゲート電極に近接する部分で相対的に表面エネルギーが高く、膜厚方向に組成が異なる有機トランジスタおよびその製造方法。

(もっと読む)

半導体装置

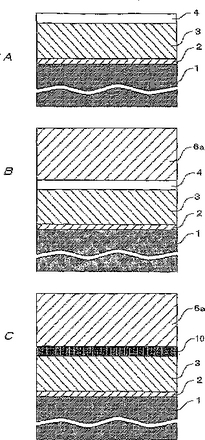

【課題】低抵抗、且つ高耐熱性を有するゲート電極またはゲート配線を備えた高性能な半導体装置を実現する。

【解決手段】ゲート電極またはゲート配線を三層以上の積層構造とし、例えば、第1の導電層106a/第2の導電層106b/第3の導電層106cを形成する。さらに、第2の導電層の幅は、第1の導電層及び第3の導電層の幅よりも狭いことを特徴とする。そして第1の導電層及び第3の導電層は高融点金属でなる。これにより高性能な半導体装置を実現できる。

(もっと読む)

電子デバイス、電子デバイスの製造方法および電子機器

【課題】特性に優れ、かつ、特性の経時劣化を防止し得る電子デバイス、かかる電子デバイスを用いた表示装置、および、電子機器を提供すること。

【解決手段】薄膜トランジスタ1は、互いに分離して設けられたソース電極20aおよびドレイン電極20bと、ソース電極20aおよびドレイン電極20bの表面に形成された有機膜60と、ソース電極20aおよびドレイン電極20bを覆い、かつ、有機膜60と接触するように設けられた有機半導体層30と、有機半導体層30上に設けられたゲート絶縁層40と、ゲート絶縁層40上に設けられたゲート電極60とを有する。有機膜60は、好ましくは一般式:CF3(CF2)m(CH2)nSH(ただし、mは1〜35の整数を示し、nは2〜33の整数を示す。)で表される非共役系有機化合物を含む有機化合物を、ソース電極20aおよびドレイン電極20bの表面に結合させてなるものである。

(もっと読む)

エピタキシャル基板、および半導体素子

【課題】ブレイクダウン電圧を向上できる構造を有しており炭化ケイ素支持基体を用いる半導体素子を提供する。

【解決手段】ショットキダイオード11で炭化ケイ素支持基体13は、第1の面13aと第1の面の反対側の第2の面13bとを有しており、1×1018cm−3を超えるキャリア濃度を示す。窒化ガリウムエピタキシャル層15は第1の面13a上に設けられている。オーミック電極17は第2の面13b上に設けられている。ショットキ電極19は、窒化ガリウムエピタキシャル層15に設けられている。窒化ガリウムエピタキシャル層15の厚さD1は5マイクロメートル以上1000マイクロメートル以下である。また、窒化ガリウムエピタキシャル層15のキャリア濃度は1×1014cm−3以上1×1017cm−3以下である。

(もっと読む)

有機薄膜トランジスタを備える有機電界発光表示装置及びその製造方法

【課題】 有機薄膜トランジスタを備える有機電界発光表示装置及びその製造方法を提供する。

【解決手段】 キャパシタ領域とトランジスタ領域とを備える基板と、基板のトランジスタ領域に形成され、ゲート電極、半導体層、ソース電極及びドレイン電極を備えるTFTと、基板のキャパシタ領域に形成され、下部電極と上部電極とを備えるキャパシタと、TFTのソース電極とドレイン電極のうち、何れか一方に連結される表示素子を備え、半導体層は、有機半導体層を備え、TFTのゲート電極の下部または上部に形成されるゲート絶縁膜は、少なくとも有機絶縁膜を備え、キャパシタの上部電極と下部電極との間に形成されるキャパシタ誘電膜は、無機絶縁膜を備えることを特徴とする有機電界発光表示装置である。

(もっと読む)

CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法

【課題】CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法を提供する。

【解決手段】本発明の一実施形態によると、半導体装置を形成する方法は、半導体本体(14)の外面上にゲートスタック(22)を形成する段階を含む。第1及び第2の側壁本体(34)が、ゲートスタックの対向する側に形成される。ゲートスタックのゲート導電体(24)の外面に第1の凹部(36a)が形成され、この第1の凹部が形成された後にゲートスタックの中に第1のドーパント(40)が注入される。第1のドーパントは、第1の凹部を形成するゲートスタックの外面から内向きに拡散する。第1のドーパントは、ゲートスタックと半導体本体の間のインタフェースに向って拡散する。第1の凹部は、インタフェースにおいて第1のドーパントの濃度を増加させる。

(もっと読む)

MIS型半導体装置

【課題】帰還容量の増大や、耐圧とオン抵抗のトレードオフの悪化を招くことなく、ゲート電極に低抵抗の配線を接続してゲート抵抗を低減すること。

【解決手段】n+ソース領域4とnドリフト領域5との間のpベース領域の表面上にゲート絶縁膜を介してゲート電極1が設けられたMIS型半導体装置において、n+ソース領域4、nドリフト領域5およびゲート電極1を上から見たときのゲート電極1の所々に、nドリフト領域5側には幅が広がらずに、n+ソース領域4側に幅が広がった複数の拡幅部2を設ける。そして、この拡幅部2において接続部3を介して、ゲート電極1を、ゲート電極1よりシート抵抗の低い材料よりなる配線に接続することによって、帰還容量として寄与するゲート−ドレイン間容量を増やしたり、耐圧とオン抵抗のトレードオフの悪化を招いたりすることなく、ゲート抵抗を低減する。

(もっと読む)

薄膜トランジスタの製造方法、電気光学装置、及び電子機器

【課題】 基板加熱温度の制限範囲を逸脱することなく製造コストの低減を実現できる薄膜トランジスタの製造方法を提供する。

【解決手段】 基板上に形成された半導体層と電極部材とを具備した薄膜トランジスタの製造方法であって、前記基板上に前記半導体層を形成した後に行われる前記電極部材を形成する工程が、液相法を用いて金属材料からなる前記電極部材を形成する工程であり、当該工程における前記電極部材の焼成温度が250℃以下であることを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】熱的安定性に優れたhigh-kゲート絶縁膜を実現する。

【解決手段】基板11の上にHfO2 よりなるhigh-k膜14をCVD法を用いて堆積した後、high-k膜14の上にゲート電極15を形成し、その後、ソース・ドレイン領域又はゲート電極15に注入された不純物に対する活性化アニール処理を行なう。high-k膜14の堆積温度をx[℃]とし、活性化アニール処理の温度をy[℃]としたときに、x及びyは、y ≦ 0.5・x + 825 の関係を満たす。

(もっと読む)

半導体素子の製造方法

【課題】 製造工程を簡素化することできると共に、工程数を増加させずに特性を向上させることができる半導体素子の製造方法を提供する。

【解決手段】 絶縁性ダイヤモンド基板1上にギャップ層2を形成し、その両側に導電性ダイヤモンド層3a及び3bを形成する。その後、ギャップ層2を溶解除去し、基板1並びに導電性ダイヤモンド層3a及び3bの一部を覆うように高抵抗ダイヤモンド層4を形成する。次に、高抵抗ダイヤモンド層4上にゲート絶縁膜5を形成し、ゲート電極形成予定領域とソース電極形成予定領域との間及びゲート電極形成予定領域とドレイン電極形成予定領域との間に保護膜6a及び6bを形成する。そして、これらを覆うように金属電極層7を形成した後、この金属電極層7におけるソース電極8、ドレイン電極9及びゲート電極10となる部分以外の部分を収束イオンビームにより除去する。

(もっと読む)

スパッタリングターゲットの製造方法

【課題】ロングスロースパッタやリフロースパッタ等の新スパッタ方式でスパッタリングした際に発生する新たな不良モード(巨大ダストや大きな凹部)の発生を抑制することを可能にしたスパッタリングターゲットの製造方法を提供する。

【解決手段】Y、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Sc、Cu、Si、Pt、Ir、Ru、Pd、Ti、Zr、V、Nb、Ta、Fe、Ni、Cr、Mo、W、Mn、Tc、ReおよびBからなる群から選ばれる少なくとも1種の元素を0.01〜20質量%の範囲で含み、残部が実質的にAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、ArおよびKrから選ばれる少なくとも1種の元素を含むガスを使用する。得られたインゴットまたは焼結体を加工してスパッタリングターゲットを作製する。

(もっと読む)

541 - 560 / 620

[ Back to top ]