Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

561 - 580 / 620

半導体装置およびその製造方法

【課題】基板表面側でトランジスタとストレージノード電極との接続を低抵抗で実現する。

【解決手段】トレンチ3を形成し、トレンチの内壁にカラー酸化膜4を形成し、不純物が導入されている半導体材料を、前記カラー酸化膜4が形成されているトレンチ内に埋め込んでストレージノード電極5を形成する。ストレージノード電極5に隣接した基板領域に、ソース・ドレイン領域11を有するトランジスタTRを形成する。ソース・ドレイン領域11とストレージノード電極5とがカラー酸化膜4を挟んで近接する箇所を、半導体材料のエッチングレートに比べ絶縁材料のエッチングレートが大きい条件でエッチングする。このエッチングによりカラー酸化膜4が基板深部側に後退した部分4Aが形成され、そこに非晶質シリコンなどの半導体材料を埋め込んで半導体接続層15Aを形成する。半導体接続層15Aおよび周囲の半導体部に半導体と金属の合金層19を形成し、当該合金層19によりソース・ドレイン領域11とストレージノード電極5とを電気的に接続する。

(もっと読む)

FINFETと一体化した平坦基板デバイス及びその製造方法

【課題】 FINFETと一体化した平坦基板デバイス及びその製造方法を提供すること。

【解決手段】 フィン型電界効果トランジスタ(FinFET)と一体化した平坦基板デバイス(100)、及び、その製造方法は、基板(103)と、基板(103)上の埋め込み分離層(105)と、埋め込み分離層(105)上の半導体層(115)と、を含むシリコン・オン・インシュレータ(SOI)ウエハ(101)を含む。構造体(100)は、さらに、埋め込み分離層(105)上のFinFET(130)と、基板(103)に一体化された平坦型電解効果トランジスタ(FET)(131)と、を含み、FETゲート(127)は、FinFETゲート(125)に対して高さの違いは極くわずかである。構造体(100)は、さらに、基板(103)に構成された逆型ウェル領域(104、106、108、110)を含む。一実施形態においては、構造体(100)は、さらに、基板(103)に構成された浅いトレンチ分離領域(111)を含む。

(もっと読む)

半導体装置の製造方法

【課題】均一で良好な特性を有する半導体金属合金層を有する半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)半導体層10の上方にゲート絶縁層20を形成する工程と、(b)前記ゲート絶縁層の上方にゲート電極22を形成する工程と、(c)前記半導体層の上方の所定の領域にレジスト層を形成する工程と、(d)前記レジスト層に覆われていない領域の半導体層の表面40をアモルファス化する工程と、(e)前記半導体層の上方に金属層32aを形成する工程と、(f)アモルファス化された前記半導体層と、前記金属層とを反応させるために熱処理を行う工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】

ソース/ドレイン層での金属シリサイド膜の突き抜けやリーク電流の発生を抑えること。

【解決手段】

金属シリサイドのみからなるゲート6と、ソース/ドレイン層9上に形成されるとともに、ゲート6の膜厚よりも薄く、かつ、シリコン基板2のシリサイド化を抑制するシリサイド化抑制成分を含む金属シリサイド膜10と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 高いON電流を有し、しかも消費電力の低いCMOS回路を実現するためのMISトランジスタ構造を提供する。

【解決手段】 nチャネル型MISトランジスタ(Qn)とpチャネル型MISトランジスタ(Qp)のそれぞれのゲート絶縁膜5は、酸化ハフニウム膜で構成されている。また、ゲート電極18は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比がほぼ1(PtSix:x=1)のPtシリサイド膜で構成されている。pチャネル型MISトランジスタ(Qp)のゲート電極17は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比が1未満(PtSix:x<1)のPtシリサイド膜で構成され、ゲート電極17のフェルミレベルピニングが抑制されている。

(もっと読む)

パワー半導体素子

【解決手段】ノンドープGaNからなるチャネル層(1)と、チャネル層(1)の表面上に形成されたn型のAl0.2Ga0.8Nからなるバリア層(2)と、バリア層(2)上に選択的に形成されたp型のAl0.1Ga0.9Nからなる半導体層(3)と、半導体層(3)の両側のうちの一方側に位置するバリア層(2)上に形成されたドレイン電極(4)と、少なくとも半導体層(3)とドレイン電極(4)との間で半導体層(3)に隣接する位置のバリア層(2)上に形成された絶縁膜(7)と、絶縁膜(7)上に形成されたフィールドプレート電極(8)とを有するパワー半導体素子。  (もっと読む)

(もっと読む)

分子ワイヤの製造方法、分子ワイヤ、分子膜および電子素子

【課題】 共役ポリマーをベースとした分子スケールの電子素子を大量生産するために、単一分子ワイヤを製造する方法を提供する。

【解決手段】 本発明の分子ワイヤ24の製造方法は、ハロゲン21を含む共役モノマー溶液中に導電性基板20を浸漬し、導電性基板20の表面にハロゲン21を吸着させるステップと、導電性基板20を電極として、導電性基板20に第1パルスを印加し、ハロゲン21が吸着された導電性基板20の表面に共役モノマー22が2つ以上重合したオリゴマー23を生成させるステップと、導電性基板20に第2パルスを印加し、ハロゲン21が吸着された導電性基板20の表面に沿ってオリゴマー23に共役モノマー22を重合させるステップとを含む。

(もっと読む)

安定化された銀のナノ粒子及びそれらの利用法

【課題】 電気的に伝導的な電子素子要素の製造のために適した、液体プロセス可能(processable)な、安定した、銀含有の、ナノ粒子組成、を低コストで準備する。

【解決手段】 銀化合物、還元剤、安定剤、及び、オプショナルな溶媒を含む反応混合物内で、熱的に除去可能な安定剤の存在下で、銀化合物を、ヒドラジン化合物を含む還元剤と反応させて、銀含有ナノ粒子の表面上の安定剤の分子を伴った、複数の銀含有ナノ粒子を形成すること、を含む工程(process)。

(もっと読む)

半導体装置及びその製造方法

【課題】 High−k膜を用いたMISFETの電子移動度および正孔移動度を共に増加させ高性能の相補型MISFETを形成する。

【解決手段】 シリコン基板1の表面部にpウェル層2およびnウェル層3が形成され、素子分離領域4により区画されたnチャネルMISFETには、窒素添加のないnチャネル界面層5、窒素添加のないnチャネル高誘電体ゲート絶縁膜6およびnチャネルゲート電極7が形成されている。そして、n型ソース・ドレイン拡散層8が設けられている。これに対して、pチャネルMISFETでは、窒素添加のpチャネル界面層9、窒素添加のpチャネル高誘電体ゲート絶縁膜10およびpチャネルゲート電極11が形成されている。そして、p型ソース・ドレイン拡散層12が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタにおけるトランジスタ特性の劣化と、周辺回路用トランジスタにおけるゲートエッジの電界集中とをともに回避し得る半導体装置及びその製造方法を得る。

【解決手段】フローティングゲート3の底面端部及び上面端部には、熱酸化膜4のバーズビーク形状5がそれぞれ形成されている。また、コントロールゲートの底面端部には、熱酸化膜10のバーズビーク形状11が形成されている。ゲート長方向に関する熱酸化膜4の寸法は、ゲート長方向に関する熱酸化膜10の寸法よりも小さい。バーズビーク形状5は、バーズビーク形状11よりも小さい。また、バーズビーク形状5は、周辺回路用トランジスタのゲート電極(ポリシリコン膜36)の底面端部に形成される熱酸化膜37のバーズビーク形状38(図12)よりも小さい。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタの閾値を十分制御することのできるシリサイドゲート電極を作成できる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、(a)シリコン基板の複数の活性領域上に、夫々、ゲート絶縁膜、多結晶シリコン層を含む積層構造を形成する工程と、(b)前記多結晶シリコン層の各々にn型またはp型の不純物を注入する工程と、(c)前記多結晶シリコン層の各々に注入された不純物を活性化する工程と、(d)工程(c)の後、前記各多結晶シリコン層を覆ってシリサイド反応可能な金属層を堆積する工程と、(e)全記多結晶シリコン層と前記金属層との間でシリサイド化反応を生じさせ、前記多結晶シリコン層の全厚さがシリサイド化されたゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 微粒子とこの微粒子に結合した有機半導体分子とによって導電路が形成され、その導電性が電界によって制御されるように構成された半導体装置及びその製造方法であって、デバイス構造を工夫することによって性能が向上した半導体装置及びその製造方法を提供することにある。

【解決手段】 金などの微粒子10と、この微粒子に結合した有機半導体分子13との結合体を電極2の上に層状に形成し、電極2の反対側の結合体層の面上に電極6を設け、電極2と電極6との間の結合体層の膜厚方向に形成された導電路の導電性を、ゲート電極4を通じて制御する縦型電界効果トランジスタを形成する。上記結合体層では微粒子10と有機半導体分子13とが交互に結合したネットワーク型の導電路が形成される。この導電路では、有機半導体分子内の導電路が微粒子内の導電路によって連結され、有機半導体分子内の移動度を最大限に利用することができる。

(もっと読む)

誘電体層表面処理を有する電子デバイスの製造方法

(a)(i)モノマーを含む前駆物質をプラズマ重合すること、および(ii)モノマーのインターポリマー化単位のポリマーを1つ以上含むターゲットからスパッタリングすることからなる群から選択されたプラズマによる堆積技術を用いて、実質的にフッ素化されていないポリマー層を誘電体層上に堆積する工程であって、前記モノマーが芳香族モノマー、実質的に炭化水素のモノマー、およびそれらの組合せからなる群から選択される工程と、(b)有機半導体層を前記ポリマー層に隣接して堆積する工程とによる、電子デバイスの製造方法。  (もっと読む)

(もっと読む)

薄膜トランジスタの製造方法

【課題】 段差のある部位に電極又は配線等を形成する工程を含む薄膜トランジスタの製造方法において、該段差部位に簡便且つ確実に積層膜或いは連結膜を形成することが可能な方法を提供する。

【解決手段】 本発明の製造方法は、半導体層84上であって当該半導体層84の略中央部に位置する第1バンク部31bと、半導体層84の周縁であって、該半導体層84を取り囲む形にて形成される薄膜部32と該薄膜部32を取り囲む形にて形成される厚膜部33とを有する第2バンク部31aと、を含むバンクを形成する工程と、薄膜部32と第1バンク部31bとに取り囲まれた領域内に、導電材料を含む第1機能液60を、半導体層84を覆う形にて配置する工程と、該第1機能液を乾燥させて第1導電膜を得る工程とを含み、その後、薄膜部32を除去して、該除去領域に第2導電膜を形成することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ソースおよびドレインにおける接合リークを抑制し、膜厚が互いに異なるシリサイドをゲート電極に含むトランジスタを同一半導体基板上に備えた半導体装置を提供する。

【解決手段】 半導体基板10の表面に形成された第1のソース層13aおよび第1のドレイン層23aとこの上に形成された第1のシリサイド層14aと、半導体基板表面に設けられた第1のゲート絶縁膜5a上に形成され、第2のシリサイド層20aを有する第1のゲート電極6aと、前記第1のゲート電極の側壁に設けられたシリコン窒化膜9aとを含む第1のトランジスタ101および、半導体基板10の表面に形成された第2のソース層13bおよび第2のドレイン層23bと、この上に形成され、第1のシリサイド層14aと膜厚が同じである第3のシリサイド層14bと、半導体基板表面に設けられたゲート絶縁膜5b上に形成され、第2のシリサイド層20aと膜厚が異なる第4のシリサイド層20bを有する第2のゲート電極6bとを含む第2のトランジスタ102、を備えている。

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

窒化物系半導体装置

【課題】高耐圧/低オン抵抗の窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体装置は、窒化物系半導体から実質的になる第1半導体層1と、第1半導体層上に配設されたノンドープ若しくは第1導電型の窒化物系半導体から実質的になる第2半導体層2と、を有する。第1及び第2半導体層はヘテロ界面を形成する。第2半導体層上にゲート電極11が配設される。ゲート電極を間に挟むように第2半導体層の表面内に第1及び第2トレンチ3、4が形成される。第1及び第2トレンチの表面内に、第1及び第2半導体層よりも低抵抗の拡散層から実質的になる第1導電型の第3及び第4半導体層5、6が形成される。第3及び4半導体層にソース電極15及びドレイン電極16が電気的に接続される。

(もっと読む)

半導体装置

【課題】 高誘電率膜により構成されたゲート絶縁膜と、P型不純物を含む多結晶シリコン膜により構成されたゲート電極とを含む半導体装置において、閾値電圧の増加を抑制する。

【解決手段】 P型MOSFET120は、半導体基板(Nウェル102b)と、半導体基板上に形成され、Hf、Zr、およびランタノイド元素のいずれかからなる群から選択される第一の元素と、ならびにNとを含むシリケート化合物を含む高誘電率膜108により構成されたゲート絶縁膜と、ゲート絶縁膜上に形成されるとともに、P型不純物を含む多結晶シリコン膜114により構成されたゲート電極と、ゲート絶縁膜とゲート電極との間に形成され、第一の元素と多結晶シリコン膜114との反応を阻止するとともに、比誘電率が8以上の阻止酸化膜110と、を含む。

(もっと読む)

半導体装置

【課題】 高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えることができるようにし、ゲートリーク電流の増大を抑えて、信頼性の低下を招かないようにする。

【解決手段】 半導体装置を、ゲート電極1がメタルゲート電極であるか、又は、ゲート絶縁膜4が高誘電率ゲート絶縁膜である場合に、ゲート電極1とゲート絶縁膜4との間に、ゲート電極1側から順に、シリコン酸化膜2、シリコン窒化膜3を備えるものとする。

(もっと読む)

半導体セルの接触不良(contactdefect)を減らす方法とシステム

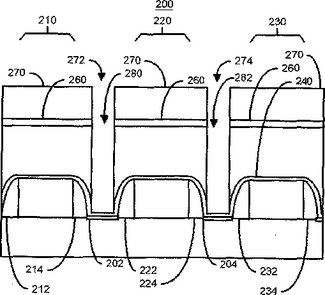

本発明は、半導体デバイス中に少なくとも1つのコンタクトを提供する方法およびシステムを提供する。半導体デバイスは、基板(201)、エッチング停止層(240)、このエッチング停止層(240)上にある層間絶縁膜(250)、層間絶縁膜(250)上にある反射防止(ARC)層(260)、およびエッチング停止層(240)より下にある少なくとも1つの構造を含んでいる。少なくとも1つのアパーチャを有しているとともに、このARC層(260)上にあるレジストマスクを提供する。このアパーチャは、ARC層(260)の露出した部分上方にある。この方法およびシステムは、エッチング停止層(240)を貫通してエッチングすることなく、露出したARC層(260)およびその下にある層間絶縁膜(250)をエッチングすることを含む。これにより、少なくとも1つのコンタクトホールの一部を提供する。この方法とシステムはまた、原位置でレジストマスクを除去し、少なくとも1つのコンタクトホールを原位置に提供すべく、コンタクトホールの一部において露出したエッチング停止層(240)の一部を除去し、コンタクトホールを導電材料で充てんすることを含む。  (もっと読む)

(もっと読む)

561 - 580 / 620

[ Back to top ]