Fターム[4M104HH13]の内容

Fターム[4M104HH13]に分類される特許

141 - 160 / 385

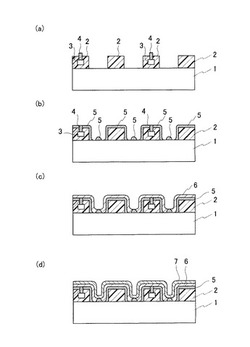

配線構造

【課題】断線が発生することを抑制可能な配線構造を提供する。

【解決手段】始めに、半導体装置の表面にアルミニウム金属膜5を形成する。次に半導体装置の表面に窒化チタン膜6を形成する。そして最後に半導体装置の表面にアルミニウム金属膜7を形成する。すなわち、シリコン基板1と電極4とを接続する電気配線を金属膜の3層構造により段階的に形成する。これにより、シリコン基板1と絶縁膜2との間に形成される段差の底部部分において金属膜の被覆率が低くなることによって断線が生じることを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 高アスペクト比の貫通電極を有する半導体装置を低温プロセスによって製造する。

【解決手段】 半導体基板1の表面側に配置された第1の電極3と裏面側の第2の電極6は、接続孔4に充填された導電物7と、接続孔4内に延在する第2の電極6の延在部6aとによって電気的に接続される。接続孔4が高アスペクト比であっても、第2の電極6を接続孔4の底部まで形成する代わりに導電物7を用いることで、低温プロセスによる成膜が可能となる。

(もっと読む)

スパッタリング装置

【課題】スパッタリング堆積膜のカバレッジ性を適切かつ充分に改善できるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、基板70およびターゲット35Bが配された真空成膜室30と、基板70とターゲット35Bとの間の真空成膜室30の成膜空間30Aにプラズマ27を誘導するプラズマガン40と、成膜空間30Aに配された偏向電極60と、偏向電極60に正電圧を印加する第1電源50と、ターゲット35Bに負電圧を印加する第2電源52と、を備える。そして、このような正負電圧に基づいて、プラズマ27からターゲット35BにドリフトするAr+のターゲット35Bへの入射方向が制御されている。

(もっと読む)

ジピリジル系レベリング剤によるマイクロエレクトロニクスにおける銅の電子沈積

【課題】半導体集積回路デバイス基板におけるビア構造をメタライズするための方法を提供する。

【解決手段】半導体集積回路デバイス基板は、前面、背面、ビア構造を備え、ビア構造は、基板の前面に開口部、基板の前面を内向きに伸びる側壁部、および底部を備え、前記方法は以下からなる:

半導体集積回路デバイス基板に、(a)銅イオン源、および(b)レベラー化合物からなる電解銅沈積組成物を接触させて、前記レベラー化合物はジピリジル化合物およびアルキル化剤の反応生成物からなり;

電流を電解銅沈積組成物に供給し銅金属をビア構造の底部および側壁部に沈積し、これによって銅充填ビア構造を得る。

(もっと読む)

トレンチ及びビアの断面形状を変形させる方法及び装置

本発明の実施形態は、概して、半導体基板を処理する装置及び方法に関するものである。具体的には、本発明の実施形態は、トレンチ及びビアの断面形状を、トレンチ及びビアへの充填を行なう前に変形させる方法及び装置に関するものである。本発明の一実施形態では、トレンチ構造をエッチング液に曝すことにより、犠牲層を形成してトレンチ構造の上部開口部を閉塞する。一実施形態では、エッチング液は、第1材料と反応して犠牲層を形成する副生成物を生成することにより、第1材料を除去するように調製される。  (もっと読む)

(もっと読む)

有機表面パッシベーションでめっきの進行に差を付けて遅らせることによるボトムアップめっき

本発明の実施形態は、概して、半導体基板を処理するための装置及び方法に関するものである。一実施形態は基板を処理する方法を提供し、この方法は、基板に形成されたトレンチ構造又はビア構造を有する基板を覆うようにシード層を形成することと、シード層の一部を有機パッシベーション膜で被覆することと、前記トレンチ構造又はビア構造をめっき液に浸漬して、前記有機パッシベーション膜で被覆されないシード層の上に導電材料を堆積させることとを含む。  (もっと読む)

(もっと読む)

スパッタリング装置及びスパッタリング方法

【課題】コスト高を招くことなく、簡単な構成で高密度化プラズマを発生させることができるスパッタリング装置を提供する。

【解決手段】真空チャンバ1内で基板Sを保持するステージ7と、ステージ7に対向配置されたターゲット2と、真空チャンバ1内にスパッタガスを導入するガス導入手段とを備えたスパッタリング装置Mにおいて、ターゲット2に直流電力を投入する第1のスパッタ電源5と、基板Sに高周波電力を投入する第2のスパッタ電源8とを更に備え、両スパッタ電源5、8から電力投入すると、ターゲット2側の直流プラズマと、基板S側の高周波バイアスプラズマとが重畳されたプラズマがターゲット2と基板Sとの間に発生するように、ターゲット2及び基板Sを近接配置する。

(もっと読む)

薄膜形成装置

【課題】有機チタン化合物を気化させた原料ガスと、これに反応する添加ガスとを反応容器内に供給し、化学蒸着法により、加熱した基体の表面上に窒化チタン薄膜を作製する薄膜形成方法において、基体(例えば、CMOS基板などの半導体基板)の温度を各種機能性材料の耐熱温度である150℃乃至230℃の低温領域にした場合において、実用的な成膜速度が得られ、被覆性も良好な化学蒸着法による薄膜形成方法に用いる薄膜形成装置を提案する。

【解決手段】基体を150℃乃至230℃の温度範囲に加熱し、添加ガスの分圧Padded gasを、有機チタン化合物を気化させた原料ガスの分圧Porganometallic gasに対し、10≦Padded gas/Porganometallic gasの範囲に設定する薄膜形成装置とする。

(もっと読む)

成膜方法および成膜装置、ならびに記憶媒体

【課題】装置構成を複雑にせずに、成膜初期の核形成が短時間でなされ、表面平滑性およびステップカバレッジが良好な膜を得ることができる成膜方法および成膜装置を提供すること。

【解決手段】成膜方法は、基板を処理容器内に搬入する工程と、処理容器内の基板温度が処理容器内に導入される際の原料ガスの温度よりも低い段階で処理容器内に原料ガスを導入し、基板表面に原料ガスを集積させる工程と、原料ガスの導入を継続しつつ基板温度を成膜温度まで上昇させる過程で、基板上に膜形成のための核付を行う工程と、原料ガスの導入を継続しつつ基板温度を成膜温度に保持して基板上に所定の膜を成膜する工程とを有する。

(もっと読む)

窒化チタン障壁層の形成方法及び窒化チタン障壁層を含む半導体デバイス

【課題】追従性が高く良好なステップ・カバレージ及び低い抵抗率を有する窒化チタン障壁層を形成する方法を提供する。

【解決手段】部分的に製作された電子デバイスに窒化チタン障壁層を形成する方法であって、前記部分的に製作された電子デバイスの上に第1の温度で、第1の抵抗率を有する第1の窒化チタンサブレーヤ40を堆積させる工程と、前記第1の窒化チタンサブレーヤの上に第2の温度で、第2の抵抗率を有する第2の窒化チタンサブレーヤ42を堆積させる工程とを備えており、前記第2の温度は前記第1の温度よりも高く、第2の抵抗率は第1の抵抗率よりも低いことを特徴とする窒化チタン障壁層の形成方法。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

(もっと読む)

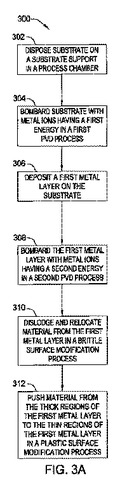

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

スパッタ成膜方法及びプラズマ処理装置

【課題】ホールやトレンチなどの凹部を被覆する膜のカバレッジ性を向上し、かつ、平坦な表面をもつ膜を成膜することが可能なスパッタ成膜方法を提供する。

【解決手段】チャンバ201内で、金属ターゲットに高周波電力及び直流電圧を印加して、プラズマを発生させるとともにターゲット粒子をイオン化させて金属イオンを発生させる。チャンバ201内のステージホルダ302上に載置された、表面に凹部を有する基板306へ、金属イオンを照射して薄膜を形成する。この際、まず初めに、5乃至15Paの圧力下でスパッタ成膜を行うことにより第1の層を形成し、次いで、0.5乃至5Paの圧力下でスパッタ成膜を行うことにより第1の層上に第2の層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

成膜方法および成膜装置、ならびに記憶媒体

【課題】不純物が少ない金属膜を低温でかつ良好なステップカバレッジで成膜することができる成膜方法および成膜装置を提供すること。

【解決手段】基板1上に気相状態の所定の金属元素を含む金属原料ガスを吸着させ吸着層2とする工程と、吸着層2に蟻酸を供給し、基板1上に所定の金属元素の蟻酸塩膜3を生成させる工程と、生成された蟻酸塩膜3に対し、還元雰囲気中でエネルギーを与え、蟻酸塩を分解して金属膜4を形成する工程とを有する。

(もっと読む)

電解処理装置及び電解処理方法

【課題】たとえ高抵抗の多孔質体を使用することで、電解めっき等の電解処理に伴って、多孔質体が発熱して電解液が上昇したとしても、電解液の液温を所定の値に維持することで、基板面内に均一な電解処理方法を提供する。

【解決手段】アノード58を内部に収容するとともに、下端開口部を多孔質体50で閉塞したハウジング48を有するアノードヘッド46と、基板保持部30で保持した基板の被処理面周縁部に接触して該周縁部をシールするシールリング34及び該周縁部に接触して被処理面に通電するカソード接点36を有するカソード部32と、ハウジング48内に温度が制御された電解液を該電解液が多孔質体50と接触するように供給して循環させるアノード側液循環ライン70と、多孔質体50が基板Wと近接した電解処理位置にあるときに該多孔質体50と基板Wとの間に温度が制御された電解液を供給して循環させる基板側液循環ライン72を有する。

(もっと読む)

薄膜パターンの形成方法。

【課題】安定した大きなオーバーハングを形成することによって十分な厚さの金属薄膜を基板の上に形成する薄膜パターンの形成方法を提供しようとするものである。

【解決手段】基板1の上のフォトレジスト層3を露光させ、その後1次現像によってフォトレジスト層3とリフトオフレジスト層2の一部を除去し、フォトレジスト層3を現像液に対する耐性処理を行い、2次現像によってリフトオフ層2の一部を除去することによってフォトレジスト層3にオーバーハングを形成し、その後に金属薄膜5の形成を行い、その後フォトレジスト層3をリフトオフレジスト層2とともに除去するようにした。

(もっと読む)

液晶表示装置、及びその製造方法

【課題】 厚膜銅のパタン加工した断面を順テーパ形状にエッチングすることができ、配線パタンの上に積層する絶縁膜などのカバレッジを良くし、層間短絡などの不良発生を大きく低減可能な液晶表示装置及びその製造方法を提供すること。

【解決手段】 ガラス基板やインジウムを主成分とする透明導電膜を形成した基板上に、第一層を下層とし、第二層を上層とする積層膜から構成され、第一層は純銅、第二層は銅よりもウェットエッチング加工における溶解度が大きい銅を主成分とする合金で形成する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

141 - 160 / 385

[ Back to top ]