Fターム[4M104HH13]の内容

Fターム[4M104HH13]に分類される特許

101 - 120 / 385

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

成膜装置、成膜方法および記憶媒体

【課題】成膜原料として用いるCo2(CO)8を気相供給する際に、その分解を極力抑制して不純物の少ないCo膜を再現性よく成膜することができる成膜装置を提供すること。

【解決手段】成膜装置は、チャンバー1と、チャンバー内でウエハWを加熱するためのヒーター5と、チャンバー1外に配置された、成膜原料としてコバルトカルボニルを収容する成膜原料容器31と、成膜原料容器31から気体状のコバルトカルボニルをチャンバー1に供給するための配管43と、チャンバー1内を減圧排気する排気機構23と、成膜原料容器31から配管43を介してチャンバー1に気体状のコバルトカルボニルを供給するための手段38と、原料容器31および配管43の温度をコバルトカルボニルの分解開始温度未満に制御する温度コントローラ60と、原料容器31内にCOガスを供給する手段37とを具備する。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

成膜方法および記憶媒体

【課題】Coをメッキシードとして電解メッキによるCu膜を成膜する場合に、Coの溶出を抑制してCoシード上に均質でかつ密着性の高いCu膜を形成することができる成膜方法を提供すること。

【解決手段】表面にシード層としてCo膜が形成された基板を準備し、Co膜の上に硫酸銅溶液を主体とするメッキ液を用いて、電解メッキにより基板のCo膜上にCu膜を成膜するにあたり、基板表面をメッキ液に浸漬する前に、基板に対して、Coの表面電位がCoの酸化電位より低くなるような負の電圧を印加する。

(もっと読む)

スパッタリング装置およびスパッタリング方法並びに成膜システム

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料の埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、スパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマ22を磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34BとAlターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってAlターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al堆積膜200のカバレッジ性が、プラズマ放電電流ID、ターゲットバイアス電圧VB、および、ターゲット−基板間距離Lに基づいて調整される。

(もっと読む)

スパッタリング装置およびスパッタリング方法

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料のコンタクト埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、Alからなるターゲット35Bおよび開口部が形成された基板34Bを格納可能なスパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマを磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34Bとターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al材料からなる堆積膜のカバレッジ性が、プラズマ放電電流IDおよび基板バイアス電圧VAに基づいて調整されている。

(もっと読む)

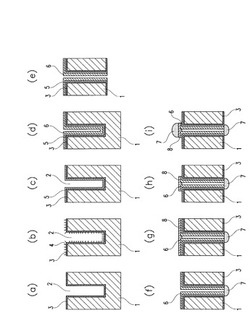

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面側で、Al電極膜表面にボイドが形成され難くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の一方の主面側に半導体機能領域と所要のコンタクトホール8を含む層間絶縁膜7パターンを形成した後、該半導体基板1の前記一方の主面側の全面に、厚膜のアルミニウム膜またはアルミニウム合金膜を成膜して前記コンタクトホール8の底面を含む半導体基板1表面に導電接触させて所要の電極膜9を形成する際に、前記アルミニウムの成膜工程を膜厚に関して複数回に分け、複数回の前記アルミニウム成膜工程の間に、直前のアルミニウム膜表面の凹凸を等方性エッチングにより平坦化する工程を設ける半導体装置の製造方法とする。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

貫通シリコンビアを有するめっき物及びその形成方法

【課題】貫通シリコンビア形成時におけるビア内側壁の銅シード層のカバレッジが良好で均一な銅配線層を有するめっき物を提供することを目的とする。

【解決手段】基材上にバリア層として形成された、タングステン及びタングステンと合金化した際に銅に対するバリア性を有する金属(A)との合金薄膜、その上に無電解置換銅めっきにより銅シード層、さらに前記無電解置換銅めっきを実施したのと同一のめっき液を用いた電気銅めっきにより銅配線層がこの順番で形成されてなる、貫通シリコンビアを有するめっき物。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

銅を充填する方法

【課題】基板上に存在する、アスペクト比(深さ/開口径)が5以上の導電処理した非貫通穴に短時間で銅を良好に充填する方法を提供する。

【解決手段】基板上に存在する、アスペクト比(深さ/開口径)が5以上の導電処理した非貫通穴に銅を充填する方法であって、酸性銅めっき浴として、水溶性銅塩、硫酸、塩素イオン、ブライトナー及びジアリルアミン類と二酸化硫黄との共重合体を含む酸性銅めっき浴を用いて、周期的電流反転銅めっきして非貫通穴に銅を充填することを特徴とする銅充填方法。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】被処理体の表面に形成されている凹部の内径や幅が小さくても、薄膜の成膜時のステップカバレジを向上させることが可能な成膜方法を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部を有する絶縁層が表面に形成された被処理体Wを収容すると共に処理容器内へチタンを含む原料ガスと還元ガスとを供給してプラズマCVD法によりガスを反応させて被処理体に対してチタンを含む薄膜を形成する成膜方法において、反応が原料ガスの反応律速の反応状態となるように原料ガスと還元ガスの各流量を設定するように構成する。これにより、被処理体の表面に形成されている凹部の内径や幅が小さくなったり、凹部のアスペクト比が大きくなっても、薄膜の成膜時のステップカバレジを向上させることが可能となる。

(もっと読む)

めっき方法及びめっき装置

【課題】貫通電極用凹部の底部からのめっき膜の成長速度を遅くすることなく、貫通電極用凹部内に銅等の金属を、内部にボイド等の欠陥を生じさせることなく完全に充填することができるめっき方法を提供する。

【解決手段】表面に貫通電極用凹部12を有する基板Wとアノードとをめっき液中に互いに対峙させて配置し、基板Wとアノードとの間に電圧を印加しながら基板Wとアノードとの間のめっき液を攪拌して貫通電極用凹部12内へ金属を充填し、貫通電極用凹部内12への金属の充填量に相関して、基板とアノードとの間のめっき液の攪拌条件を変化させる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

電解銅めっき浴および電解銅めっき方法

【課題】本発明の目的は、微細な構造であっても溝や穴に電解銅めっきによって銅を良好に埋め込むことのできる抑制剤と、促進剤および平滑剤を必須の有効成分として含有する電解銅めっき浴、およびこの電解銅めっき浴を用いた電解銅めっき方法を提供することにある。

【解決手段】本発明は、特定のブロック重合体化合物からなる抑制剤を0.001〜5質量%;特定の促進剤を0.01〜100質量ppm;およびジアリルアミンと硫酸化合物との塩・マレイン酸共重合体、ビニルピロリドン・N,N−ジメチルアミノエチルメタクリル酸共重合体と硫酸化合物との塩、塩化メチルビニルイミダゾリウム・ビニルピロリドン共重合体、N−アシル−N’−カルボキシエチル−N’−ヒドロキシエチルエチレンジアミンまたはそのアルカリ金属塩(ここで、アシルは、炭素数8〜20の脂肪族アシル基を示す)から選ばれる少なくとも1種の平滑剤を0.01〜250質量ppmを含有してなることを特徴とする電解銅めっき浴に係る。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

101 - 120 / 385

[ Back to top ]