Fターム[4M104HH13]の内容

Fターム[4M104HH13]に分類される特許

21 - 40 / 385

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】互いに隣接する2つの半導体層どうしの境界部分において、電界集中を緩和し、絶縁耐圧を改善することが可能な半導体装置およびその製造方法を提供する。

【解決手段】第1半導体層11の露出面11a、第2半導体層12の一面12a、および第3半導体層13A,13Bの表面13Aa,13Baの互いの境界で段差が実質的に無くなるように形成することで、露出面11a、一面12a、および表面13Aa,13Baからなる平面Q上に、段差無く平坦なゲート酸化膜16が形成できる。

これにより、ゲート酸化膜16の特定部分に電界が集中し、ゲート絶縁耐圧の低下などゲート酸化膜16の機能を大きく損なうことがない。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

ドライエッチング方法

【課題】本発明は、ダミー材料の除去により形成される溝や孔に容易にトップラウンドを設けることができるドライエッチング方法を提供する。

【解決手段】本発明は、層間酸化膜に周囲を囲まれたダミー材料を除去することにより溝または孔を形成するドライエッチング方法において、前記ダミー材料を所定の深さまでエッチングし、前記エッチング後に等方性エッチングを行い、等方性エッチング後に前記ダミー材料の残りを除去することを特徴とするドライエッチング方法である。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

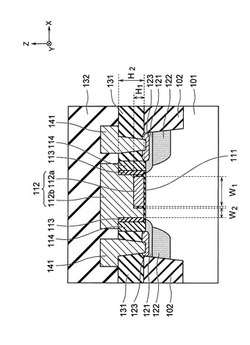

パワーデバイス

【課題】膜剥がれの要因となる有機材料を用いることなく、エレクトロマイグレーションの耐性と長期信頼性を向上できるパワーデバイスを提供する。

【解決手段】バリア層4(AlGaN)4上に形成された酸化シリコン(SiO2)からなる層間絶縁膜10と、層間絶縁膜10のソース電極5上に形成され、基板平面に対して略垂直な第1の側壁W1を有する第1コンタクトホール部10aと、第1コンタクトホール部10aの第1の側壁W1の上縁から上側に向かって徐々に広がるように層間絶縁膜10に形成され、基板平面に対して傾斜した第2の側壁W2を有する第2コンタクトホール部10bと、第1,第2コンタクトホール部10a,10b内および層間絶縁膜10上に形成された配線層12とを備える。上記配線層12は、第1コンタクトホール部10aにおいて第1の側壁W1の基板厚さ方向の寸法よりも膜厚が厚い。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

下地導電層付き基板の製造方法および貫通電極基板の製造方法

【課題】製造時間とコストの大幅な削減が可能な下地導電層付き基板および貫通電極基板の製造方法を提供する。

【解決手段】厚さ方向に複数の貫通孔2を有するガラス基板3の貫通孔2内に下地導電層4を有する基板の製造方法であって、前記ガラス基板3の貫通孔2内に、金属粒子と分散媒とを含有する流動性の導電性組成物(金属インク)の層を形成する工程と、この導電性組成物の層を加熱して、貫通孔2の内壁面に金属粒子の金属を主体とする下地導電層4を形成する工程とを備える方法である。貫通電極基板5の製造方法は、こうして形成された下地導電層4上に電解めっき等により導電性金属の層を形成して、貫通孔2内に充填された貫通電極6を形成する工程を有する。

(もっと読む)

基板中間体、基板及び貫通ビア電極形成方法

【課題】貫通ビア電極を形成する際に処理温度が高くなく且つ低コストで、バリア層を均一に、且つ高い密着強度で製造する。

【解決手段】シリコン基板10の厚さ方向に形成された高アスペクト比の、貫通ビア電極形成用の孔12の内周面に、自己組織化単分子膜24を形成し、これに、金属ナノ粒子14を、高密度で吸着させて、この金属ナノ粒子14を触媒として、バリア層を無電解めっきにより形成し、バリア層の上にシード層を無電解めっきにより形成し、次に、貫通ビア電極材を電解めっきにより堆積して、孔12を埋めて、貫通ビア電極を形成する。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

成膜方法およびリスパッタ方法、ならびに成膜装置

【課題】トレンチおよび/またはホールの間口のオーバーハングを抑制することができる成膜方法およびリスパッタリング方法を提供すること。

【解決手段】処理容器内にプラズマ生成ガスを導入しつつ誘導結合プラズマ生成機構により処理容器内に誘導結合プラズマを生成し、直流電源から金属ターゲットに直流電力を供給し、バイアス電源により載置台に高周波バイアスを印加して、載置台上の被処理基板に金属薄膜を堆積させる工程と、誘導結合プラズマ生成機構によるプラズマの生成と直流電源への給電を停止し、処理容器内にプラズマ生成ガスを導入しつつ載置台に高周波バイアスを印加して、処理容器内に容量結合プラズマを形成するとともにプラズマ生成ガスのイオンを被処理基板に引き込んで堆積された金属薄膜をリスパッタリングする工程とを有する。

(もっと読む)

21 - 40 / 385

[ Back to top ]