Fターム[4M104HH13]の内容

Fターム[4M104HH13]に分類される特許

41 - 60 / 385

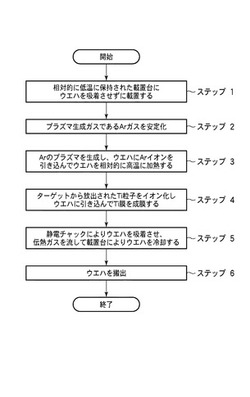

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

パターン修正方法

【課題】配線パターンの修正において、修正抵抗を低減することが可能となる、パターン修正方法を提供する。

【解決手段】パターン修正方法は、導電性パターン20の欠陥部21を修正するパターン修正方法であって、導電性インクを塗布することにより第1のインク層31を形成する工程と、第1のインク層31を焼成することにより第1の修正層32を形成する工程と、少なくとも一部が第1の修正層32に重なるように導電性インクを塗布することにより、第2のインク層33を形成する工程と、第2のインク層33を焼成することにより第2の修正層34を形成する工程とを備え、第1の修正層32および第2の修正層34により欠陥部21を挟んで配置される導電性パターン20間の電気的接続が確保される。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

金属薄膜の製膜方法、金属薄膜、および金属薄膜の製膜装置

【課題】低不純物で、段差被覆性がよく、高真空を使わない金属薄膜の製膜方法を提供する。

【解決手段】有機金属化合物原料を真空チャンバー内に載置された製膜対象物上に搬送する原料搬送工程と、反応性ガスを、加熱された金属触媒体に接触させた後に、前記真空チャンバー内に載置された前記製膜対象物上に搬送する反応性ガス搬送工程と、を有することを特徴とする金属薄膜の製膜方法を提供する。また、有機金属化合物原料または/および反応性ガスが、炭素原子、窒素原子、水素原子、ケイ素原子、リン原子、ホウ素原子および金属原子から選択される1または2以上の原子のみからなることを特徴とする金属薄膜の製膜方法を提供する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、シード層3を形成する工程における下地の加熱温度を、アモルファスシリコン膜を形成する工程における前記下地の加熱温度よりも低くする。

(もっと読む)

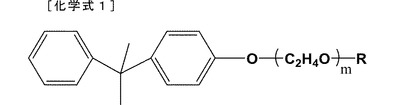

銅めっき溶液およびこれを用いた銅めっき方法

【課題】高縦横比のビアホールを埋め込むのに好適な銅めっき溶液および銅めっき方法を提供する。

【解決手段】シード層を有する基板を浸漬し、水、銅供給源、電解物質、塩素イオン、第1添加剤、第2添加剤、および第3添加剤を含み、前記第1添加剤は、化学式1に示す化合物である銅めっき溶液を用いて銅めっきを行う。

(式中、Rは、水素原子または炭素原子数1〜6のアルキル基であり、mは、平均重合度であり6〜14の実数である。)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】配線形成時に配線形成用溝の間口を閉塞させないで配線形成用溝内に連続したCu膜を形成できる半導体装置の製造方法を提供する。

【解決手段】配線形成用溝形成工程では、層間絶縁膜10に配線形成用溝31を形成する。バリアメタル膜形成工程では、配線形成用溝31が形成された層間絶縁膜10上の全面にバリアメタル膜14を形成する。Cu膜形成工程では、配線形成用溝31間の層間絶縁膜10上の膜厚に比して配線形成用溝31内の底部の方が厚くなるように、バリアメタル膜14上にCu膜15を形成する。リフロー工程では、バリアメタル膜14上のCu膜15をリフローさせ、配線形成用溝31内に埋め込む。そして、除去工程では、少なくとも配線形成用溝31間の層間絶縁膜10上のバリアメタル膜14をCMP法によって除去する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、アミノシラン系ガスのアミノシランは熱分解させないで、下地上に吸着させる。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理に使用するガスを供給する処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、処理室101に、被処理体1を複数収容するとともに、コントローラ150が、下地を加熱し、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、下地を加熱し、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御する。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

電子部品の製造方法

【課題】高温で成膜される低融点金属の凝集を防止し、十分なバリア性及びぬれ性を有するバリア層を形成して、凹部に低融点金属を付け回り良く充填する。

【解決手段】電子部品の製造方法が、4Pa以上20Pa以下の圧力下で、被処理体306と接する電極301に第1のバイアス電力を印加し、プラズマ処理により被処理体306の上にTiNxからなる第1のバリア層404を成膜する手順と、4Pa以上20Pa以下の圧力下で、電極301に第1のバイアス電力よりも小さいイオン入射エネルギーを与える第2のバイアス電力を印加し、またはバイアス電力を印加しないで、プラズマ処理により第1のバリア層の上にTiNxからなる第2のバリア層405を成膜する手順と、第2のバリア層405の上に、Tiからなる第3のバリア層409を成膜する手順と、第3のバリア層409の上に低融点金属406を充填する手順と、を有する。

(もっと読む)

半導体装置の製造方法並びにコンタクトホール及び/又はラインの埋め込み方法

【課題】 表面ラフネスの精度をさらに改善でき、コンタクトホールやラインなどの微細化の進展に対応可能なアモルファスシリコン膜を成膜できる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置内部のコンタクトホール5及び/又はラインが形成された層間絶縁膜である下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜4を形成する工程と、を備える。

(もっと読む)

電気めっき方法

【課題】めっき時における平均電流値をより高くした効率的なめっきによるめっき膜の埋込みを行ってめっき時間を短縮し、しかも理想的なめっき膜の埋込みを行うことができるようにする。

【解決手段】内部にスルーホールを形成した基板をめっき液中に浸漬させてめっき槽内に配置し、めっき槽内に配置される基板の表面及び裏面にそれぞれ対向する位置にアノードをめっき槽内のめっき液中に浸漬させて配置し、基板の表面と該表面と対向する位置に配置されるアノードとの間、及び基板の裏面と該裏面と対向する位置に配置されるアノードとの間に、パルス電流を供給して基板の表裏両面に所定時間のめっきを行うめっき処理を複数回に亘って行い、基板の表面と該表面と対向する位置に配置されるアノードとの間、及び基板の裏面と該裏面と対向する位置に配置されるアノードとの間に、めっき時とは逆方向の電流をそれぞれ供給する逆電解処理をめっき処理の間に行う。

(もっと読む)

拡散バリアー層及びその製造方法

【課題】表面を有する基材アセンブリを提供し、この表面の少なくとも一部の上にバリアー層を提供することを含む、集積回路の製造で使用する方法を提供する。

【解決手段】バリアー層14は、白金(x):ルテニウム(1−x)合金でできており、ここでxは約0.60〜約0.995、好ましくはxは約0.90〜0.98である。バリアー層14は、化学気相堆積によって作ることができ、バリアー層14を形成する表面の少なくとも一部は、ケイ素含有表面でよい。この方法は、キャパシター、蓄積セル、接触ライニング等の製造で使用する。

(もっと読む)

41 - 60 / 385

[ Back to top ]