Fターム[4M106BA14]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | 電圧の印加 (693)

Fターム[4M106BA14]に分類される特許

81 - 100 / 693

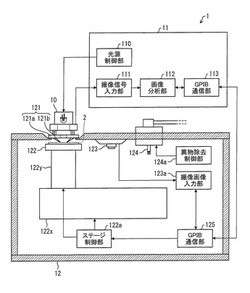

固体撮像素子の検査装置及び検査方法

【課題】本発明は、電気的画素欠陥検査と、画像分析による画素欠陥検査を行うことができ、歩留まりを向上させる固体撮像素子の検査装置及び検査方法を提供する。

【解決手段】本発明の固体撮像素子検査装置は、複数の画素が形成された固体撮像素子2に対して電気的欠陥検査を行う接触型のプローブ121bを備えるテスタ11と、テスタ11による欠陥画素の検出結果に基づき、欠陥画素が検出された固体撮像素子を撮像する撮像部123、及び、撮像部123からの出力画像を基に異物の有無を検出する画像分析部(例えば、画像分析部112)を備えるプローバ12とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】切断が確実に行われる電気ヒューズを備えた半導体装置とその製造方法とを提供する。

【解決手段】電気ヒューズは、ポリシリコン膜14と、タングステンシリサイド等の金属シリサイド膜15との積層構造とされる。所定の長さの電気ヒューズに、電流密度40mA/μm3以上の電流を流すことにより、エレクトロマイグレーションとピンチ効果によって電気ヒューズが確実に切断される。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

プローブ検査装置、及びプローブ検査方法

【課題】ナノプロービングにおいてプローブを試料表面に近づける作業を短時間で行う。

【解決手段】プローブ検査装置400は、試料12を載置する試料台10と、試料台10の上方の待機位置に待機するプローブ20と、試料台10をプローブ20の待機位置に向けて移動させる第1の駆動装置160と、試料台10とプローブ20の待機位置の間を通過する方向に第1の荷電粒子線32を照射する第1の荷電粒子銃30と、試料12が第1の荷電粒子線32を遮断したことを示す信号を生成する第1の検出部120と、第1の検出部120が生成した信号により第1の駆動装置160を制御する第1の制御部140を備える。

(もっと読む)

半導体装置及び抵抗測定方法

【課題】製造時に発生する不具合を減少しつつ、回路面積を縮小可能なチップレイアウトを設計する。

【解決手段】本発明による半導体装置は、電流源接続用の第1パッド1と、一端が、第1パッド1に接続され、他端が、基板20と同じ導電型の拡散層21を介して基板20に接続されたヴィアチェーンと、電圧測定用の第2パッド2及び第3パッド3とを具備する。ヴィアチェーンは、第1パッド1及び第2パッド2が接続される第1配線4と、一端が第1配線4に接続され、他端が第3パッド3に接続された、抵抗測定対象となるヴィア又はコンタクト6とを備える。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査に用いるプローブの耐久性を向上できる半導体装置を提供する。

【解決手段】ウエハーのスクライブ線150上に配置された第1チェック素子1を具備する。第1チェック素子1は、第1配線絶縁膜5と、第1配線絶縁膜5の第1開口部に配置された第1チェック素子パッド10とを備える。第1チェック素子パッド10は、導電性の第1パッドメタル部12と、矩形の平面形状を有する絶縁性の第1ダミー部13とを含む。第1ダミー部13の平面形状は、スクライブ線150の長手方向と垂直な2つの第1長辺と、第1チェック素子パッド10の外周部近傍に配置される2つの第1短辺とを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのテスト時間を短縮可能な半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ10a,10bに、パッドとを有し、且つパッドが半導体チップ11a,11bの主面に形成されたパッド16a,16bと半導体チップの主面と相対向する半導体ウエハの主面に形成されてパッドと電気的接続されたパッド17a,17bとを有するテスト回路を内蔵した半導体チップを複数、形成する工程と、複数の半導体ウエハを、隣接する半導体ウエハにおける半導体チップの入力パッドの各々を互いに接触させて検査装置40のステージ上に載置する工程と、載置された複数の半導体ウエハのうち外側の半導体ウエハにおける半導体チップのパッドに検査装置40のプローブ針43を接触し、半導体チップの各々を一括でテストする工程とを備えることを特徴とする半導体装置。

(もっと読む)

半導体ウェーハ抵抗率測定装置

【課題】ウェーハ端部付近における測定値変動を正しく補正し、正確な値を求めることができる半導体ウェーハ抵抗率測定装置を提供する。

【解決手段】4探針抵抗率測定器を用いて半導体ウェーハ12の抵抗率を測定する半導体ウェーハ抵抗率測定装置において、4探針プローブ14の4探針に供給する電流の探針と測定する電圧の探針を変更して半導体ウェーハ12の端部から半径方向の直線上における複数の位置の抵抗率を測定手段により測定する。前記測定手段により測定された複数値に対して演算を行ってから前記各測定位置から前記ウェーハ端部までの距離と半導体ウェーハ上に生成される薄膜の端部までの距離との差による端部補正係数を乗じて抵抗値を得る。

(もっと読む)

プローブカード検査装置、検査方法及び検査システム

【課題】プローブカードの良否判定を正確に行うことを可能にするプローブカード検査装置を提供する。

【解決手段】プローブカード検査装置10は、プローブカードの複数のプローブ針の先端部を受け入れる被接触面を表面に有する基板を備える。被接触面は、この被接触面に形成された複数の境界線により複数の座標領域Aj(1,1)〜Aj(11,11)に区画されている。複数の座標領域Aj(1,1)〜Aj(11,11)は格子状に配列されている。

(もっと読む)

半導体検査システム、それを構成する半導体装置及び半導体検査装置、並びに半導体装置の検査方法

【課題】単一の電源から複数の半導体主回路部に電源を供給する場合に安定した電源を供給する半導体検査システムを供給する。

【解決手段】半導体検査システムは、半導体装置1100と、半導体検査装置1200とを有し、半導体装置は、半導体基板と、半導体基板に配置された複数の半導体回路領域1120を有し、半導体回路領域はそれぞれ、半導体検査装置による検査の対象となる半導体主回路部1121と、半導体主回路部に供給される電源を検出する検出回路部1122と、検出回路部の出力を無線方式で出力する第1の無線回路部1124と、を備え、半導体検査装置は、主電源部と、プローブカードとを有し、プローブカードは、主電源部に接続された共通電源配線と、共通電源配線に接続された複数の電源回路部と、電源回路部に接続され、電源回路部を制御する制御回路部と、制御回路部に接続された第2の無線回路部1224とを備える。

(もっと読む)

半導体検査システム、それを構成する半導体装置および半導体検査装置、並びに半導体装置の検査方法

【課題】半導体検査システムにおいて、単一の電源から複数の半導体主回路部に電源を供給する場合、各半導体主回路部に安定した電源を供給することができない。

【解決手段】本発明の半導体検査システムは、半導体装置と、半導体検査装置とを有し、半導体装置は、半導体基板と、半導体基板に配置された複数の半導体回路領域を有し、半導体回路領域はそれぞれ、半導体検査装置による検査の対象となる半導体主回路部と電源制御部を備え、半導体検査装置は、主電源部と、プローブカードを有し、プローブカードは、主電源部に接続された共通電源配線を備え、共通電源配線から各電源制御部に対して、第1の電源がそれぞれ供給され、電源制御部は、第1の電源を供給源として第2の電源を半導体主回路部に供給する。

(もっと読む)

基板端子間電圧検知回路

【目的】電圧測定器を接続することなく、半導体ウェハに生じたプラズマチャージアップを広い範囲にわたって迅速に検知することが可能な基板端子間電圧検知回路を提供する

【構成】半導体基板上に設けられた一対の電極間に生じた電圧を検知する基板端子間電圧検知回路は、電極間に接続された抵抗路と、抵抗路の中間点に一端が接続された回路電源と、抵抗路の両端部の一方と回路電源の他端との間に互いに並列接続されて互いに異なる溶断定格電流を有する少なくとも2つのヒューズ回路と、からなる基板端子間電圧検知回路であって、ヒューズ回路の各々は、一方と前記中間点との間の電位差に応じてオンオフするスイッチと、前記スイッチに直列接続した抵抗素子及びヒューズ素子を含んで前記回路電源の両端に接続した電流路と、を含むことを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造精度判定方法及びその装置

【課題】短時間でウエハー面内分布などの数多くのパターン変換差に係るデータを収集することができ、適切に半導体装置の製造精度判定或いは管理を行い得る。

【解決手段】複数の異なる面積を有するキャパシタを、半導体素子生成工程においてアクティブエリアに形成し、各キャパシタに電圧を印加して、夫々のキャパシタ電流を検出し、検出された電流値と対応するキャパシタの面積とからアクティブエリアのパターン変換差を算出し、パターン変換差に基づき製造精度を判定する。

(もっと読む)

半導体製造装置の管理方法及び管理システム

【課題】ウェハの分類等に関し各種の不良領域の高精度な分類等を可能とする。

【解決手段】本方法及びシステムでは、フェイルビット解析結果やクリティカルエリア等の情報を用いて、ウェハ領域を、異物不良領域(E1)、同心円状不良領域(E2)、及びクラスタ不良領域(E3)に分類する処理を行う。そして、各領域の不良率(工程ごと、フェイルビットモードごと等)を求め、その結果情報を出力する。分類処理は、ウェハ領域分割(S501)、チップ単位の不良数の算出(S502)、ヒストグラム作成(S503)、領域合成・異常値チップ除外(S504)、第1の分類(E1,E2)(S505)、第2の分類(E3)(S506)、分類確定(S507)等から成る。

(もっと読む)

回路パターン検査装置およびその検査方法

【課題】高感度にROI領域の欠陥発生頻度や特性尤度の効率的なモニタリングをする。

【解決手段】ステージの連続移動に同期して、マトリクス状に配置した複数の電子線をステージ移動方向に間引いて回路パターンに照射し、発生する二次電子等を取得し、同一領域で取得した画像を加算平均することで高速にしかも高SNの画像を取得し、取得画像より回路パターンの欠陥を判定する。ステージ移動と垂直方向への移動時に隣接領域ではなく、間引いて画像取得することで、ROI領域のみ、又は回路パターン全体の欠陥発生頻度や特性尤度を効率的にモニタリングする。

(もっと読む)

半導体集積回路

【課題】NMOSトランジスタ及びPMOSトランジスタのそれぞれの特性を個別に且つ正確に測定する。

【解決手段】NMOSディレイ回路50が、複数個縦列接続されてインバータチェーン回路が構成される。インバータ55,56は、電源電圧端子に一端を接続されるトランジスタ51、53と、接地端子に一端を接続され他端をトランジスタ51、53の他端に接続されたトランジスタ52,54とを備える。インバータ56に含まれるトランジスタ53は、PMOSトランジスタであり、残りのトランジスタ51,52、54はNMOSトランジスタである。トランジスタ53は、反転プリチャージ信号PCBが”L”のときに導通状態とされてノードN2を電源電圧VDD(”H”)までプリチャージする一方、反転プリチャージ信号PCBが”H”のときは非導通状態とされる。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

集積回路及び集積回路の選別テスト方法

【課題】従来では外部機器にテストデータを保持、管理するため、管理精度の確実性に対する問題や管理コストが増大する問題があった。

【解決手段】不揮発性記憶回路と、第1の回路と、を備える集積回路の選別テスト方法であって、少なくとも前記第1の回路に対して第1の条件でテストを行い、前記第1の条件でのテストの第1の結果を前記不揮発性記憶回路に書き込み、前記第1の結果に応じて、前記第1の回路に対して第2の条件でのテストを行い、前記第2の条件でのテストが行われた場合の第2の結果を前記不揮発性記憶回路に書き込み、前記第1の結果もしくは前記第2の結果から前記集積回路を複数のグレードにランク分けする集積回路の選別テスト方法。

(もっと読む)

半導体ウェハおよび半導体ウェハにおける電圧供給方法

【課題】半導体チップを互いに接続する共通配線を備えた半導体ウェハの製造コストが増大するという課題を解決する半導体ウェハおよび半導体ウェハにおける電圧供給方法を提供する。

【解決手段】半導体基板101と、半導体基板101上に規則的に配置された複数の半導体チップ102と、半導体チップ102を互いに接続する共通配線103と、共通配線103に接続された共用電極パッド104、とを有し、共用電極パッド104は、複数の半導体チップ102を内包する露光照射領域と同一の規則性をもって配置され、かつ、露光照射領域に含まれる半導体チップ102を囲む外縁の内部に配置されている。

(もっと読む)

半導体装置とその製造方法、及び半導体ウエハ

【課題】半導体装置とその製造方法、及び半導体ウエハにおいて、個片化後の半導体チップがもとの半導体ウエハのどこに位置していたかを容易に特定すること。

【解決手段】複数のチップ領域Rcとスクライブ領域Rsとを有するシリコン基板20と、複数のチップ領域Rcの各々に対応する複数のモニタ素子Mと、スクライブ領域Rsに形成され、複数のモニタ素子Mの各々を電気的に接続する配線2とを有し、スクライブ領域RsにおけるダイシングラインX1〜X7、Y1〜Y7の位置をずらしたときに、配線2の異なる部分がダイシングされるようにして、配線2と複数のモニタ素子Mとの結線状態をダイシングラインX1〜X7、Y1〜Y7の位置に応じて可変にした半導体ウエハWによる。

(もっと読む)

81 - 100 / 693

[ Back to top ]