Fターム[4M106BA14]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | 電圧の印加 (693)

Fターム[4M106BA14]に分類される特許

101 - 120 / 693

半導体装置及び半導体チップ

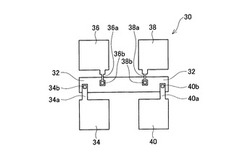

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

エピタキシャル層の抵抗率測定方法

【課題】シリコンウェーハ上の高濃度にドープされたエピタキシャル層の抵抗率であっても、従来に比べて正確且つ容易に測定することができるエピタキシャル層の抵抗率の測定方法を提供する。

【解決手段】シリコン単結晶ウェーハ上に形成されたエピタキシャル層の抵抗率を測定する方法であって、少なくとも、エピタキシャル成長装置に、モニターウェーハとしてSOIウェーハを投入し、該SOIウェーハのSOI層上に、前記シリコン単結晶ウェーハの主表面に成長させるエピタキシャル層の成長条件と同一条件でモニターエピタキシャル層を成長させ、その後、前記モニターエピタキシャル層の膜厚及び抵抗値を測定して前記モニターエピタキシャル層の抵抗率を算出し、該算出された抵抗率を、前記シリコン単結晶ウェーハの主表面に成長させる前記エピタキシャル層の抵抗率とすることを特徴とするエピタキシャル層の抵抗率測定方法。

(もっと読む)

半導体集積回路装置の製造方法

【課題】液晶ドライバ等の半導体集積回路装置においては、その形状が極端に細長いため、長手方向にプロセス特性がばらつくと、所望のデバイス特性が得られない。そこで、実製品ウエハにプロセスモニタ用の検査用素子を各種配置して、それらを測定することによって、プロセス特性のばらつきを監視している。しかし、ウエハ内におけるグローバルなプロセスばらつきは、比較的抽出しやすいものの、チップ内の局所的なプロセスばらつきの高精度の抽出は、大幅に検査用素子密度を上げない限り、困難であることが、本願発明者等により明らかにされた。

【解決手段】本願の一つの発明は、半導体集積回路装置の製造方法において、ウエハ上のチップ領域の近傍に複数のテスト素子領域を異なるピッチで配列し、プローブテストにおいて、それらを電気的に計測することにより、プロセスの局所的ばらつきをモニタするものである。

(もっと読む)

DLTS測定用電極及びその製造方法

【課題】測定時において疑似ピークが現れないDLTS測定用電極を提供する。

【解決手段】シリコン基板上に設けられたアンチモンからなるショットキー電極12aと、シリコン基板10の表面10aとショットキー電極12aとの間に設けられたチタンからなる密着膜12bとを備える。本発明によれば、ショットキー電極の材料としてアンチモンを用いていることから、DLTS測定において疑似ピークがほとんど現れず、しかも、測定時におけるリーク電流を抑制することが可能となる。このため、シリコンウェーハに含まれている重金属の種類や濃度を正確且つ高感度に評価することが可能となる。

(もっと読む)

ウェハ保持体およびそれを搭載したウェハプローバ

【課題】 常温時の高精度なチャックトップ上面の平面度を常温時に限らず昇温時や冷却時にも高精度に維持することができるウェハプローバ用ウェハ保持体を提供する。

【解決手段】 本発明のウェハプローバ用ウェハ保持体は、ウェハ載置面を有するチャックトップと、チャックトップにおいてウェハ載置面とは反対側の面に設置される温度制御手段と、前記チャックトップ及び/又は前記温度制御手段を支持する支持体と、該支持体の下部に設置された底板とを有し、該底板の熱膨張係数が、前記チャックトップの熱膨張係数以上であり、前記チャックトップ、支持体、底板の熱伝導率をそれぞれK1、K2、K3としたとき、K1>K2かつK3>K2であることを特徴とする。

(もっと読む)

半導体構成素子を備えた回路装置

本発明は、電力端子(2.1,2.2)と、該電力端子から電気的に絶縁されている、制御電圧(U2)を印加するための制御端子(2.0)とを有する半導体構成素子(2)、並びに、半導体構成素子の電気的な特性を測定するために制御端子に接触接続するための制御端子コンタクト面(3)を有する電気的な回路装置(1,1a,1b,31,51,61,71)に関する。接続装置(6,32)、特にアンチヒューズ又は回路ユニットが設けられている。接続装置を介して制御端子を直列ユニット(4;34;78,74)と電気的に接続可能であり、接続装置を、制御端子が直列ユニットと電気的に接続されていない非導通状態から、制御端子が直列ユニットと電気的に接続されている導通状態に移行可能である。アンチヒューズを半導体構成素子に集積することができる。  (もっと読む)

(もっと読む)

電気的試験用プローブ、それを用いた電気的接続装置、及びプローブの製造方法

【課題】 機械的特性及び電気的特性のいずれもが良好なプローブを提供することにある。

【解決手段】 電気的試験用プローブは、ニッケル・ボロン合金で形成された針本体部と、該針本体部から下方へ突出しかつ該針本体部と異なる導電性材料で形成された針先部とを備える。前記ニッケル・ボロン合金の結晶サイズは最大で50nmであり、前記ボロンの含有量は0.02以上、0.20wt%以下である。

(もっと読む)

ウエハプローバ、および当該ウエハプローバを用いた故障解析方法

【課題】プロービング状態におけるウエハの反りを可及的に抑え、かつ十分な観測視野が得ることが可能なウエハプローバ、及び当該ウエハプローバを用いた故障解析方法を提供する。

【解決手段】ウエハ1に対して固浸レンズ23を用いた裏面解析を行うためのウエハプローバ10であって、

ウエハ1を支持する表面に設けられた凹部11aと、この凹部11aの底面11a2の一部を貫通する開口部11bとを有するウエハステージ11と、

凹部11aにx−y方向に移動可能に収容され、ウエハ1を支持し、開口部11bよりも小さい観測口12aを有する、可動プレート12と、

を備える。

(もっと読む)

半導体デバイス

【課題】データ入出力パッドとテストパッド間の経路や当該経路途中の回路の不良を検出することを可能とする方法を提供する。

【解決手段】半導体装置のテストのためのテストパッド(第2パッド22)と内部回路23との接続経路に、データ入出力のためのマイクロバンプパッド(第1パッド21)が配置されている。このため、前記第2パッド22を用いたテスト時に、前記内部回路23までの全経路の段線不良、回路不良が検出できる。

(もっと読む)

半導体基板の評価方法及び半導体デバイスの製造方法

【課題】 半導体基板のリーク電流による評価方法において、測定のための構造が単純であっても、安定した測定を行うことができ、デバイス活性領域を感度良く評価することができる半導体基板の評価方法を提供する。

【解決手段】 半導体基板をリーク電流により評価する方法であって、少なくとも、前記半導体基板の表面部にPN接合を形成する工程と、前記PN接合による内部電界と同等の第一の電圧V1を前記PN接合に印加してリーク電流を測定し、第一のリーク電流値I1を得る工程と、前記第一の電圧V1よりも高い第二の電圧V2を前記PN接合に印加してリーク電流を測定し、第二のリーク電流値I2を得る工程と、リーク電流値Iを、計算式I=I2−(V2/V1)1/2×I1に従って算出する工程とを含み、前記算出したリーク電流値Iにより前記半導体基板を評価する半導体基板の評価方法。

(もっと読む)

ワイドギャップ半導体のバンドギャップ電子物性の計測方法

【課題】 光励起を利用したワイドギャップ半導体のバンドギャップ電子物性の計測方法を実現する。

【解決手段】 ワイドギャップ半導体であるn−GaN膜13の表面に、当該ワイドギャップ半導体とショットキー接合が可能な透光性を有する有機金属膜を形成するショットキー電極形成工程により、バンドギャップが広くて仕事関数が大きいという特徴を有する導電性の有機金属膜15をワイドギャップ半導体のショットキー電極として形成し、単色光照射部23により、単色光として、例えば、十分に波長分解能の高い単色光を有機金属膜15側から分光照射し、電圧パルス発生部21により、有機金属膜15が形成されたワイドギャップ半導体n−GaN膜13に所定のタイミングで所定電圧強度のパルス電圧を印加し、インピーダンス計測部22により、有機金属膜15が形成されたワイドギャップ半導体n−GaN膜13のインピーダンスを検出する。

(もっと読む)

半導体試験装置

【目的】載置台の表面に付着した異物を除去し易く、半導体ウエハまたは半導体チップの裏面に、キズやクラックなどの欠陥を発生させない半導体試験装置を提供する。

【解決手段】この半導体試験装置は、載置台1と、載置台1を上下に移動させる移動手段6と、半導体チップ9の図示しない表面電極(エミッタ電極やゲート電極)と接触し電流を流すプローブ4と、載置台1に付着した異物を吹き飛ばすクリーニング機構であるブローノズル5とで構成され、載置台1の表面をシリコンより硬度が高い材料である、たとえば、超硬合金で形成する。

(もっと読む)

半導体装置、及びその評価解析方法

【課題】ゲート酸化膜耐圧評価用TEGにおけるゲート酸化膜の耐圧異常箇所を、確実にTEM観察できる半導体装置、及び、その評価解析方法を提供すること。

【解決手段】半導体基板1上に絶縁領域2aに囲まれたアイランド1aが形成され、アイランド1a表面に形成されたゲート酸化膜2上にて複数本のゲート電極3、4が形成され、奇数本目の各ゲート電極3の一端は、絶縁領域2a上にて第1相互接続部3bに接続され、偶数本目の各ゲート電極4の他端は、絶縁領域2a上にて第2相互接続部4bに接続され、第1相互接続部3bは、絶縁領域2a上に形成された第1パッド3aに接続され、第2相互接続部4bは、絶縁領域2a上に形成された第2パッド4aに接続され、ゲート電極3、4の幅は、0.1μm以上0.5μm以下であり、ゲート電極3、4の幅とゲート電極3、4間の間隔との和となる最小ゲートピッチは、0.2μm以上である。

(もっと読む)

インライン特性化

【課題】インライン特性化のための装置を提供する。

【解決手段】当該装置は、第1の電圧および第2の電圧が順次印加される、熱的に分離された被試験デバイスと、第1の電圧および第2の電圧が順次印加されている間に、第1の温度および第2の温度をそれぞれ実質的に同時に、被試験デバイスに与える局部加熱素子と、被試験デバイスの温度を測定する温度感知ユニットとを含む。

(もっと読む)

位置ずれ検査パターンを有する半導体装置およびパターン位置ずれ検査方法

【課題】パターン位置ずれ検査精度を向上させる位置ずれ検査パターンを有する手段の提供。

【解決手段】複数のFETと、素子形成領域の周囲の領域に、FETのドレイン電極、ソース電極と同時に形成され、それぞれ一定の間隔で設けられた複数対の基準検査パターン19と、FETのゲート電極と同時に形成され、複数対の基準検査パターン19の間に、それぞれ基準検査パターン19の間隔と異なる間隔で設けられた複数の被検査対象検査パターン20と、複数の被検査対象検査パターン20および複数対の基準検査パターン19に接触するように設けられた金属抵抗層18と、それぞれの被検査対象検査パターン20およびこれらの各パターン20の一方において隣接する基準検査パターン19の間の第1の抵抗と、それぞれの被検査対象検査パターン20およびこれらの各パターン20の他方において隣接する基準検査パターン19の間の第2の抵抗とを測定する手段による。

(もっと読む)

FDSOIトランジスタの電気性能を評価するための方法および装置

【課題】FDSOIトランジスタの電気性能を評価するための方法を提供する。

【解決手段】基板3に電圧VBG>0またはVBG<0を印加し、ゲート15に印加される電圧VFGに応じてFDSOIトランジスタのキャパシタンスおよび/またはコンダクタンスを測定する段階と、モデル化トランジスタの誘電体-半導体界面における欠陥密度Dit1、Dit2の選択された理論値について、FDSOIトランジスタと等価な電気回路によってモデル化されたトランジスタのキャパシタンスおよび/またはコンダクタンスの理論値を計算する段階と、FDSOIトランジスタのキャパシタンスおよび/またはコンダクタンスの測定値とモデル化トランジスタのキャパシタンスおよび/またはコンダクタンスの理論値との比較によって、FDSOIトランジスタの対応する界面におけるDit1、Dit2の真の値を決定する段階とを含む。

(もっと読む)

抵抗メモリ素子の抵抗測定方法及び抵抗測定システム

【課題】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムを提供すること。

【解決手段】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムにおいて、前記抵抗メモリ素子の抵抗測定のために、まず、データ書き込みパルスを印加した後、抵抗読み取りパルスを印加する。前記抵抗読み取りパルスを印加した時のパルス波形から前記抵抗メモリ素子のセルを通して、降下する微少電圧と、これを使い、抵抗メモリ素子の抵抗を測定する。前記方法によると、抵抗メモリ素子のセルにデータを記録した直後の抵抗メモリ素子の抵抗を正確に測定することができる。

(もっと読む)

電子デバイスの絶縁性薄膜の信頼性評価法

【課題】電子デバイスの絶縁性薄膜の信頼性評価を行う方法を提供する。

【解決手段】本発明の一態様は、MLCC2を用意する工程と、前記第1の導電体が抵抗素子4の一方端に電気的に接続され、前記抵抗素子の他方端が第1の直流電源5に電気的に接続され、前記第1の直流電源が前記第2の導電体に電気的に接続され、前記抵抗素子の一方端及び他方端それぞれが増幅器7の入力側に電気的に接続され、前記増幅器の出力側が周波数分析器8に電気的に接続された接続状態で、前記増幅器の出力を前記周波数分析器によって分析することで得られるPool Frenkel電流に基づく1/f特性を示す範囲の電流ゆらぎの大きさを測定する工程と、前記工程で測定された1/f電流ゆらぎの大きさが大きい場合は、前記絶縁性薄膜の質が悪いと判定し、前記工程で測定された1/f電流ゆらぎの大きさが小さい場合は、前記絶縁性薄膜の質が良いと判定する工程とを具備する。

(もっと読む)

半導体素子評価方法

【課題】半導体モジュールの歩留まり、生産性を向上させる。

【解決手段】表面構造と裏面電極を有する複数の半導体素子が配列された半導体基板の主面に、導電性を有するシートを固着し、その主面にシートが固着された状態で、半導体基板を第1の支持台上で半導体チップに分断し、分断された複数の半導体チップを第2の支持台上に前記シートを介して載置し、載置された複数の半導体チップの動特性試験を第2の支持台上で連続して行う。これにより、縦型半導体素子の動特性試験において発生するクラックから進展・伝播する亀裂が抑制され、半導体モジュールの歩留まり、生産性が向上する。

(もっと読む)

ゲート絶縁膜の絶縁破壊寿命の評価方法、ゲート絶縁膜の絶縁破壊寿命の評価装置、ゲート絶縁膜の絶縁破壊寿命の評価用のプログラム

【課題】ソフトブレークダウンの判定条件を一意に決定することを可能にする、ゲート絶縁膜の絶縁破壊寿命の評価方法を提供する。

【解決手段】MOS型素子のゲート絶縁膜の絶縁破壊寿命を評価する際に、MOS型素子のゲート絶縁膜のソフトブレークダウンに至る寿命分布のワイブル傾きを決定する工程S1と、その後、決定したワイブル傾きから、ソフトブレークダウンの検知条件を決定する工程S2と、決定した検知条件を使用して、絶縁破壊試験を行う工程S3とを行う。

(もっと読む)

101 - 120 / 693

[ Back to top ]