Fターム[4M112EA11]の内容

Fターム[4M112EA11]に分類される特許

81 - 100 / 1,034

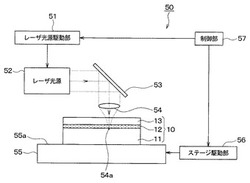

半導体装置の製造方法

【課題】犠牲層の改質度をさらに上げて、犠牲層のエッチングレートを向上させることができる半導体装置の製造方法を提供する。

【解決手段】犠牲層領域17に対応する支持基板11にレーザ光の焦点54aを合わせ、半導体層13側からレーザ光を照射する。これにより、レーザ光の焦点54aからレーザ光の入射側に伝達する熱応力によって犠牲層領域17に位置する犠牲層12にマイクロクラック12aを形成する。この後、半導体層13の開口部15からエッチング媒体を導入し、マイクロクラック12aが形成された犠牲層12をエッチングして除去することにより、支持基板11に対して構造体22〜24を浮遊させる。このように、犠牲層12にマイクロクラック12aを形成して改質度を向上させているので、犠牲層12の深部にエッチング媒体が入り込みやすくなり、犠牲層12のエッチングレートがさらに向上する。

(もっと読む)

マイクロフォン

【課題】上方から見た平面積を小さくすることができ、しかも、音響センサのバックチャンバの容積をより大きくすることのできるマイクロフォンを提供する。

【解決手段】回路基板43の上面にインターポーザ52を実装し、その上面に音響センサ51を実装する。信号処理回路53は、インターポーザ52に設けられた空間70に納められて回路基板43に実装される。音響センサ51は、インターポーザ52に設けた配線構造を通じて回路基板43に接続される。音響センサ51やインターポーザ52などは、回路基板43の上面に被せたカバー42によって覆われる。カバー42には、音響センサ51のフロントチャンバと対向する位置に音導入孔48が開口されている。インターポーザ52には、音響センサ51のダイアフラム56よりも下方の空間を、カバー42内でインターポーザ52よりも外の空間とを音響的に連通させるための通気用切欠71が形成されている。

(もっと読む)

複合センサ

【課題】電位差によって生じる静電力の影響を抑え、S/N比の低下やセンサ感度の変動を防止できる複合センサを提供することを目的とする。

【解決手段】本発明に係る複合センサは、第1可動部および第2可動部と、これらの周辺に配置されている第1ダミー部および第2ダミー部を、積層基板の層内に形成して備えている。第1ダミー部と第2ダミー部は電気的に分離されており、第1可動部と第1ダミー部には第1電位が印加され、第2可動部と第2ダミー部には第2電位が印加される。

(もっと読む)

静電容量型電気機械変換装置

【課題】溶融接合により作製される静電容量型電気機械変換装置において、接合面積などの境界条件が異なる箇所で生じる振動膜の初期変位のバラツキを低減して性能を高めることができる構成を有する装置を提供する。

【解決手段】静電容量型電気機械変換装置は、シリコン基板1と、振動膜7と、シリコン基板1の一方の表面と振動膜7との間に間隙3が形成されるように振動膜7を支持する振動膜支持部17と、で形成されるセル構造102を、少なくとも一つ以上含む素子101を有する。素子101の周囲に、振動膜支持部17と共通の層2に形成された溝103が配されている。

(もっと読む)

加速度センサー及びその製造方法

【課題】小型化が可能な加速度センサーを提供する。

【解決手段】基板と、基板上に位置する第1の電極層と、第1の電極層の第1の面と対向して位置する第2の電極層と、第2の電極層を基板に支持する支持部と、を含み、第2の電極層は、上記第1の面に沿った方向に動くことができ、支持部は、第2の電極層が上記第1の面に沿った方向に動くことができるように第2の電極層を基板に支持する。これにより、感度と精度を確保しつつ、基板の面に垂直な方向における加速度センサーの厚みを低減し、加速度センサーを小型化することができる。

(もっと読む)

MEMSデバイスの製造方法およびMEMSデバイス

【課題】 基板に沿った方向に相対的に移動可能な一対の対向電極を有するMEMSデバイスにおいて、他方の対向電極の下端部を削ることなく、一方の対向電極の下端部を短く削ることが可能な技術を提供する。

【解決手段】 本発明の製造方法は、半導体ウェハを準備する工程と、半導体ウェハの下側表面から第1導電体層と絶縁体層を貫通して第2導電体層に達する第1溝部を形成する工程と、前記第1溝部に導電体からなる保護部を形成する工程と、半導体ウェハの上側表面にレジストパターンを形成する工程と、反応性イオンエッチング法により第2導電体層に一対の対向電極を形成する工程と、反応性イオンエッチング法を継続して一方の対向電極の下端部を削る工程と、絶縁体層を選択的に除去する工程を備えている。その製造方法では、前記第1溝部は一対の対向電極が対向する方向に関して他方の対向電極の両側面の外側に配置されている。

(もっと読む)

静電容量型MEMSセンサ

【課題】高感度でありながら小型であり、かつ、製造コストも削減できる静電容量型MEMSセンサを提供すること。

【解決手段】静電容量型MEMSセンサの一例としての静電容量型マイクロフォン1は、互いに対向する第1電極部Xおよび第2電極部Yを有している。静電容量型マイクロフォン1は、第1電極部Xとしての側壁12を有する凹所9が厚さ方向に掘り込まれた半導体基板2と、凹所9の深さ方向に沿う姿勢で第1電極部Xに対向するように凹所9内に配置され、凹所9の底面から離隔した底面20Cを有し、半導体基板2の材料からなる第2電極部Yとしての膜20と、膜20を半導体基板2に結合する絶縁膜21とを含む。

(もっと読む)

静電容量式デバイスの製造方法および静電容量式デバイス

【課題】デバイス特性に影響を与えてしまうのを抑制することのできる静電容量式デバイスの製造方法および静電容量式デバイスを得る。

【解決手段】固定側基板2aの両面に露出するようにシリコンを貫通させて形成した貫通シリコン23a、23b、24a、24bを固定電極20a、20b、21a、21bとし、貫通シリコン23a、23b、24a、24bの外側露出面に金属膜25を成膜するとともに、固定側基板2aの表面における貫通シリコン23a、23b、24a、24bの外側露出面以外の部位に金属膜25と離間するように金属膜26を成膜する。そして、可動体基板1と固定側基板2aとを陽極接合する際に、金属膜25,26を用いて、固定側基板2aと可動体基板1との間に電位差を設ける一方、貫通シリコン23a、23b、24a、24bと可動体基板1とが同電位となるようにした。

(もっと読む)

静電容量型圧力センサおよび静電容量型圧力センサの製造方法

【課題】低コスト化かつ小型化を実現できる静電容量型圧力センサを提供すること。

【解決手段】圧力センサ1は、内部に基準圧室8が形成されたシリコン基板2と、シリコン基板2の一部からなり、基準圧室8を区画するようにシリコン基板2の表層部に形成されたダイヤフラム9と、ダイヤフラム9の周囲を取り囲んでダイヤフラム9をシリコン基板2の他の残余部分11から分離する分離絶縁層10とを含んでいる。ダイヤフラム9には、基準圧室8に連通した貫通孔12が形成されていて、貫通孔12内には、充填体14が配置されている。

(もっと読む)

ガラス埋込シリコン基板およびその製造方法

【課題】簡便な方法でありながら狭間隔へもガラスが埋め込まれやすくなるガラス埋込シリコン基板およびその製造方法を提供する。

【解決手段】ガラス埋込シリコン基板の製造方法は、シリコン基板10に凹部11を形成する工程と、凹部11に粉末状、ペースト状または前駆体溶液であるガラス材料20aを充填する工程と、ガラス材料20aを加熱して軟化させる工程と、軟化させたガラス材料20aを焼結させる工程と、凹部11にガラス材料20aが充填されたシリコン基板10の表裏面においてガラス材料20aとシリコン基板10とを露出させる工程とを備える。

(もっと読む)

加速度角速度センサ装置の製造方法

【課題】第1収容空間に異物が導入されることを抑制することができる加速度角速度センサ装置の製造方法を提供する。

【解決手段】

加速度検出部1および角速度検出部2が形成されたセンサ部10と蓋部20とを用意する準備工程と、センサ部10と蓋部20とを減圧空間で接合し、加速度検出部1および加熱されることによりガスを放出するガス放出材24a、50を第1収容空間3に収容すると共に、角速度検出部2を第2収容空間4に収容する接合工程と、ガス放出材24a、50からガスを放出させることにより、第1収容空間3の圧力を第2収容空間4の圧力より高くする内圧変動工程とを行う。

(もっと読む)

機能素子、機能素子の製造方法、物理量センサー及び電子機器

【課題】製造効率の低下を抑制した機能素子、機能素子の製造方法、物理量センサー及び電子機器を提供する。

【解決手段】第1基板12と、前記第1基板12上に設けられ、且つ、素子部を有する第2基板50と、を備え、前記第1基板12と前記第2基板50との間には内部空間68が設けられ、前記第1基板12および前記第2基板50の互いに対向する面の少なくとも一方には、前記内部空間68と外部とを連通する排気溝24が設けられていることを特徴とする。

(もっと読む)

荷重センサ及びその製造方法

【課題】 特に、押圧部材と当接する受圧部表面の耐摩耗性を向上させた荷重センサを提供することを目的とする。

【解決手段】 本実施形態における荷重センサ1は、荷重を受けて厚さ方向に変位可能な変位部4と、前記変位部4での変位量を検出可能な素子部(ピエゾ抵抗素子6)と、を有し、前記変位部4の荷重を受ける側の面から突出するシリコンからなる突起部5と突起部5の表面5aに成膜された無機絶縁層30とからなる受圧部17が設けられていることを特徴とする。

(もっと読む)

超音波探触子及びこれを用いた超音波診断装置

【課題】cMUTを用いた超音波探触子において、好適な絶縁構造を施すことにより被検体への電気漏洩を防止し、電気的安全性を向上させた超音波探触子を提供する。

【解決手段】音響レンズ26の超音波送受信面側あるいは音響レンズとcMUTチップ20の間に、電気漏洩防止手段が備えられている。電気漏洩防止手段は、例えば絶縁層であり、例えばグランド層である。このような構造の超音波探触子2cにより、超音波探触子から被検体への電気漏洩を防止し、電気的安全性を向上させた超音波探触子及びこれを用いた超音波診断装置を提供することができる。

(もっと読む)

半導体圧力センサ及びその製造方法

【課題】半導体圧力センサの小型化に伴う性能のばらつきを抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体圧力センサの製造方法は、ポリシリコンダイヤフラム6と、その下方の真空室となるべき空間13側に形成されたポリシリコンゲージ抵抗4bと、これらを内包し、犠牲層16と接するエッチング液導入孔15を有する絶縁膜群3,5,7とを含む積層構造を、犠牲層16上に形成する。そして、エッチング液を前記エッチング液導入孔15に通じて、犠牲層16をエッチングすることにより積層構造を真空室上で機能するダイヤフラム体11として形成するとともに、シリコン基板1における第1絶縁膜2の第1開口2a下の表面をエッチングすることにより真空室となるべき空間13と、当該空間13中に配置され、ダイヤフラム体11の中央付近に向かって突出するダイヤフラムストッパー12とを形成する。

(もっと読む)

MEMSセンサおよびその製造方法、ならびにMEMSパッケージ

【課題】互いに噛み合う櫛歯状の第1電極および第2電極の大きさのばらつきを少なくでき、センサの検出精度を向上できるMEMSセンサおよびその製造方法を提供すること。

【解決手段】ベース基板7をエッチングすることにより、柱状部29およびベース部30を形成する。次に、当該柱状部29およびベース部30を熱酸化することにより、これらを絶縁膜に変質させる。これにより、柱状部29からなる絶縁層85およびベース部30の表層部からなるベース絶縁層21を形成する。次に、ベース絶縁層21上にポリシリコン層22を形成し、当該ポリシリコン層22およびベース絶縁層21の積層構造をエッチングして、Z固定電極71およびZ可動電極72の形状に成形する。同時に、それらの間にトレンチ50を形成する。そして、当該トレンチ50の底部を等方性エッチングすることにより、ベース絶縁層21直下に凹部20(空洞23)を形成する。

(もっと読む)

センサーを製作するための方法

【課題】サイズが小さく、大量に効果的に生産できる高感度圧力センサを製造するための方法を提供する。

【解決手段】第1のデバイスウエハーをエッチングされた第2のデバイスウエハーに接合して架設された構造を作る、センサー10を製作するための方法が、開示され、その構造のたわみは、第1のデバイスウエハーのデバイス層110に埋め込まれた相互接続部400を通じてセンサー10の外面と電気的に連通する埋め込まれた感知素子310によって決定される。架設された構造は、封鎖物500によって封入される。

(もっと読む)

半導体圧力センサ

【課題】構成の小型化、製造工程の簡略化を達成し得る半導体圧力センサを提供することを課題とする。

【解決手段】半導体基板13のダイヤフラム部12に形成された複数のn型半導体領域21と、各n型半導体領域21のそれぞれに対応してn型半導体領域21内に形成されたピエゾ抵抗素子R1〜R4と、絶縁体薄膜層22を介して各ピエゾ抵抗素子R1〜R4上に形成された導電性のシールド薄膜層23とを有し、複数のピエゾ抵抗素子R1〜R4がホイートストンブリッジ回路を構成する半導体圧力センサ11において、n型半導体領域21とピエゾ抵抗素子R1〜R4上に形成されたシールド薄膜層23とは、ダイヤフラム部12に形成されたコンタクト部24によって電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

MEMSセンサおよびその製造方法、ならびにMEMSパッケージ

【課題】低コストで簡単な方法により、固定電極および可動電極を保護する層を形成できるMEMSセンサの製造方法およびこの製造方法で得られるMEMSセンサを提供する。

【解決手段】センサ領域10およびパッド領域を有するベース基板9をエッチングすることにより、露出空間38を形成し、同時にZ固定電極81およびZ可動電極82を形成する。次に、センサ領域10を覆うように第1犠牲層39および第2犠牲層40を形成する。次に、底部がパッド領域に対して接着するように、かつ頂部18が第2犠牲層40を覆うようにSiO2からなる保護層16を形成する。次に、保護層16の直下の犠牲層39,40を除去して、保護層16とセンサ領域10との間に空間を形成する。犠牲層39,40の除去後、等方性エッチングにより、Z固定電極81およびZ可動電極82の下方部を連続させて空洞を形成する。

(もっと読む)

81 - 100 / 1,034

[ Back to top ]