Fターム[4M118EA18]の内容

Fターム[4M118EA18]に分類される特許

1 - 20 / 205

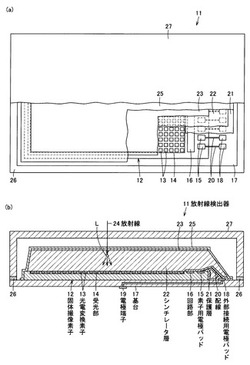

放射線検出器およびその製造方法

【課題】小型化もしくは受光部の拡大が可能で、信頼性を確保でき、さらに、解像度特性を改善できる放射線検出器を提供する。

【解決手段】複数の光電変換素子13が配列された受光部14、および光電変換素子13と電気的に接続された素子用電極パッド15を有する固体撮像素子12を備える。外部接続用電極パッド18およびこの外部接続用電極パッド18と電気的に接続されている電極端子19を有する基台17に、固体撮像素子12を固定する。素子用電極パッド15と外部接続用電極パッド18とを配線20で電気的に接続する。素子用電極パッド15、外部接続用電極パッド18および配線20を一体に被覆する保護層21を気相成長法によって形成する。固体撮像素子12の受光部14上とともに、保護層21で被覆された素子用電極パッド15、外部接続用電極パッド18および配線20上にシンチレータ層22を形成する。配線20をシンチレータ層22内に埋没固定する。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

半導体装置

【課題】電磁適合性(EMC)の問題を改善することができる半導体装置を提供する。

【解決手段】第1主面と第2主面とを有する半導体基板10と、第1主面上に形成され、入射光を電気信号に変換するセンサ部31と、第1主面上に形成されたロジック回路12と、センサ部31及びロジック回路12上に形成され、電磁波を遮断するシールド層14と、第2主面上に配置されたカラーフィルタ37と、カラーフィルタ37上に配置されたマイクロフィルタ38とを有する。

(もっと読む)

固体撮像装置

【課題】CCD型の固体撮像装置において、水平方向の読み出しの際の転送動作による発熱を効率良く放熱し、且つ出力信号に含まれるノイズを低減する。

【解決手段】固体撮像装置2Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、及び、撮像面12に対して列方向の一端側に各列毎に配置されており各列から取り出される電荷の大きさに応じた電気信号をそれぞれ出力するN個の信号読出回路20を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換してシリアル信号として順次出力するC−MOS型の半導体素子50と、主面81a及び裏面81bを有する伝熱部材80と、裏面81b上に設けられた冷却ブロック84とを備え、半導体素子50と伝熱部材80の主面81aとが互いに接合されている。

(もっと読む)

半導体素子、撮像素子、撮像モジュール、撮像装置、並びに、製造装置および方法

【課題】パッドの腐食を抑制することにより、金属材料とパッドとの接続性を向上させることができるようにする。

【解決手段】本開示の半導体素子は、内部回路の外部端子となる電極と、前記電極の表面に形成され、外部水分が接触しないように前記電極を保護する無機材料の薄膜である保護膜とを備える。本開示は、半導体素子、撮像素子、撮像モジュール、撮像装置、並びに、製造装置および方法に適用することができる。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

3次元構造を持つイメージセンサの分離型単位画素及びその製造方法

【課題】フォトダイオードに入射する光の多様な入射角に対する対応能力を提供する。

【解決手段】3次元構造を持つイメージセンサの分離型単位画素は、半導体物質の導電型とは反対の不純物を含有しているフォトダイオード14および、前記フォトダイオードの光電荷量を外部に転送するためのパッド17を備える第1のウエハ10と、前記フォトダイオードを除いたトランジスタ構成の規則的な配列を持つ画素アレイ領域、前記画素アレイ以外のイメージセンサの構造を持つ周辺回路領域、及び前記各画素を接続するためのパッド21を備える第2のウエハ20と、前記第1のウエハのパッドと前記第2のウエハのパッドとを接続する連結手段30と、を含む。

(もっと読む)

撮像素子、電子機器、並びに、情報処理装置

【課題】より容易により多様な光電変換出力を得ることができるようにする。

【解決手段】本開示の撮像素子は、入射光を光電変換する光電変換素子が形成される光電変換素子層と、前記光電変換素子層の、前記入射光の入射面とは反対の側に形成される、前記光電変換素子から電荷を読み出すための配線が形成される配線層と、前記光電変換素子層および前記配線層に積層され、他の光電変換素子を有する支持基板とを備える。本開示は撮像素子、電子機器、並びに、情報処理装置に適用することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】歩留まりの向上、およびコスト削減を図る。

【解決手段】半導体装置は、デバイス基板600と、前記デバイス基板上に接合された支持基板200と、を具備する。前記デバイス基板は、前記支持基板との接合面側の外周部に溝50を有する。

(もっと読む)

光透過性部材、光学装置およびそれらの製造方法

【課題】クラックの進行を抑制するために有利な構成を有する光透過性部材を提供する。

【解決手段】第1主面、第2主面および側面を有する光透過性部材は、前記第1主面、前記第2主面および前記側面には現れないように前記第1主面と前記第2主面との間に形成された複数の変質部を有する。

(もっと読む)

固体撮像素子及び固体撮像素子の実装構造

【課題】外部回路や載置部材などのコストや準備期間を容易に削減することが可能な固体撮像素子及び固体撮像素子の実装構造を提供すること。

【解決手段】固体撮像素子IS1は、光感応領域3を有する半導体基板1と、半導体基板1の主面1a上に配列された複数の第一電極パッド10と、半導体基板1の主面1a上に、複数の第一電極パッド10が配列された方向に沿う方向に配列された複数の第二電極パッド12と、複数の第一電極パッド10と複数の第二電極パッド12とを1対1に接続する複数の配線14と、を備えている。複数の配線14は、複数の第一及び第二電極パッド10,12の配列方向に直交する中心線lに対して線対称となる位置関係にある第一電極パッド10と第二電極パッド12とを接続している。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器

【課題】装置の信頼性や、製品の歩留まりなどを向上させる。

【解決手段】第1の開口と第2の開口との内部に金属材料を埋め込んで第1プラグと第2プラグとを設けると共に、第1プラグと第2プラグとの間を接続する接続配線を設けることで、接続導電層を形成する。そして、接続導電層において接続配線の上面を被覆するようにパッシベーション膜を形成する。このパッシベーション膜の形成工程では、高密度プラズマCVD法などのように埋め込み性に優れた成膜法で、SiO2などの絶縁膜を成膜することによって、パッシベーション膜を形成する。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

電圧調整回路、電圧調整方法および固体撮像装置

【課題】低消費電力で、かつ、発生する電圧に依存することなく消費電力が一定している電圧調整回路を提供する。

【解決手段】半導体基板上に形成され、発生する電圧を調整するための回路であって、直列に接続された複数の抵抗体(抵抗11、12、13a〜13f)と、複数の抵抗体の接続点のそれぞれに一端が接続され、他端がお互いに共通に接続された第1組の複数のヒューズ31a〜31gと、共通に接続された第1組の複数のヒューズ31a〜31gの他端に接続された第1の出力端子2とを備える。

(もっと読む)

固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続することによって構成される固体撮像装置において、それぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化とコストの削減を図ることができ、かつ、高品質の画像が得られる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とを電気的に接続する接続部によって、第1の基板と第2の基板とを電気的に接続する固体撮像装置であって、光電変換素子は第1の基板内に配置し、読み出し回路は第2の基板内に配置して光電変換素子で発生し接続部を経由した信号を読み出し、読み出された信号に対して信号処理を行う素子や回路を具備した信号処理回路は、一部の素子や回路を第1の基板内に配置し、残りの素子や回路を第2の基板内に配置し、接続部を介して第1の基板と第2の基板とに配置された素子や回路を電気的に接続する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】半導体素子上にカバー部材が貼り合わされることによってパッケージングされた半導体装置において、半導体素子へのクラックの発生を抑制し、歩留まりの向上を図る。

【解決手段】半導体素子2上にリング状のシール部材3を介してカバー部材4を貼り合わせた構成の半導体装置1において、シール部材3の内周面の形状を、半導体素子2からカバー部材4に向けて側段階的に変化するように形成する。半導体素子1側からカバー部材側に押圧する外力が加えられた場合、内周面が、半導体素子1の面に対して垂直方向に段階的に変化するように形成されることにより、半導体素子1にかかる応力が緩和される。

(もっと読む)

カラー固体撮像素子用オンチップカラーフィルタとその製造方法

【課題】画素間に遮光パターンを有する色再現性の良好なカラー固体撮像素子に使用するための画素剥がれのない良好な形状のオンチップカラーフィルタを提供すること。

【解決手段】半導体基板上に複数の光電変換素子を平面配置した固体撮像素子画素部の受光面側表面に、遮光パターンと複数色の着色透明パターンとを色別に順次平面配置するカラーフィルタ形成工程において、初期遮光パターンを、着色透明パターンの1色目の画素部になる箇所が開口部となるように黒色材料により形成する工程、1色目の着色透明材料を塗布して硬化する工程、1色目の画素部になる箇所を全て含む領域を選択的に覆うようにエッチングレジストパターンを形成する工程、エッチングレジストパターンの開口部に露出する1色目の着色透明材料とその下層の黒色材料とを除去する工程、を含む各工程を順に実施する。

(もっと読む)

補正処理装置、撮像装置および補正処理方法

【課題】より高品質の画像を得ることができ、且つ固体撮像装置が形成されるチップ面積の縮小化を図ることができる。

【解決手段】第1の基板と第2の基板とが接続部を介して電気的に接続される固体撮像装置を備える補正処理装置であって、前記固体撮像装置が有する画素は、前記第1の基板に含まれる光電変換素子と、前記第1の基板から前記接続部を介して前記第2の基板に送られた信号を出力する水平読み出し回路と、を有し、当該補正処理装置は、前記第1の基板と前記接続部との接合部分を示す接合領域の前記第1の基板上における配置パターンに応じて、前記画素から出力される信号の補正を制御する補正処理部をさらに有する。

(もっと読む)

ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法

【課題】ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体装置の正面と背面に対応する正面と背面を有する装置基板と、装置基板の正面上に形成される金属層部と、半導体装置の背面に設置され、金属層部と電気的に接続するボンディングパッドと、装置基板の背面上に設置されるシールド構造と、を含み、シールド構造とボンディングパッドは異なる厚さを有する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、及び、電子機器

【課題】ワイヤグリッド偏光子へのダストの付着を抑制することが可能な固体撮像装置を提供する。

【解決手段】光電変換素子21と、光電変換素子21上に設けられたワイヤグリッド偏光子30と、光電変換素子21に設けられる導体層24とワイヤグリッド偏光子30とを電気的に接続する導体膜35とを備える固体撮像装置20を構成する。

(もっと読む)

1 - 20 / 205

[ Back to top ]