Fターム[5B060CB00]の内容

メモリシステム (7,345) | ロード/ストア制御 (453)

Fターム[5B060CB00]の下位に属するFターム

ロードバッファ/ストアバッファ制御 (270)

データ修飾を伴うロード/ストア (51)

ロードとストア競合処理 (34)

同一アドレスに対するロードとストア (19)

Fターム[5B060CB00]に分類される特許

21 - 40 / 79

メモリコントローラおよびフラッシュメモリのデータ管理方法

【課題】フラッシュメモリにおおいて大きなサイズのデータの一部分のみを書き換える場合の書き込み処理を高速に実現し、かつ、書き換え回数の低減によりフラッシュメモリの寿命を延ばすフラッシュメモリのデータ管理方法等を提供すること。

【解決手段】フラッシュメモリ2に書き込まれている元データ(データA(ver=1))に対して書き換えが必要な差分データ(データA差分データ(ver=1.1))を取得し、該差分データのみをフラッシュメモリ2に書き込む。

(もっと読む)

メモリ制御回路および電気光学装置の駆動装置

【課題】 不揮発性メモリ(例えばMTPメモリ)を搭載するICのピン数(端子数)を削減でき、また、例えば、不揮発性メモリ(例えばMTPメモリ)にデータをプログラムするときのユーザの負担を軽減すること。

【解決手段】 データレジスタ36と、コマンドレジスタ37とを含む制御レジスタ35と、発振回路40と、書き込み回路39と、を有し、コマンドレジスタ37にプログラム開始コマンドが設定されると、発振回路40から出力される動作クロックが、不揮発性メモリ40ならびに書き込み回路39に供給され、書き込み回路39から、動作クロックOPCKに同期して、アドレス情報および書き込みデータが不揮発性メモリに向けて出力され、不揮発性メモリ50内のメモリ領域に書き込みデータが書き込まれる。

(もっと読む)

レジスタデータリード回路、半導体集積回路およびレジスタデータ出力方法

【課題】制御部における同一の機能を実装した複数の機能ブロックのデータの読み出し時間や読み出したデータ値の比較時間を削減する。

【解決手段】制御部10から同一の機能を実装した各機能ブロックに対応づけたレジスタ12−1〜12−nが保持しているデータに対する読み出し信号が有効になった時に、読み出し信号の対象となったデータを選択して出力するデータ選択部21と、各機能ブロックに対応づけたレジスタ12−1〜12−nが各々保持しているデータを比較して、全一致か否かを示す比較結果を出力する比較部22と、データ選択部21から出力される選択された機能ブロックのデータと比較部22から出力される比較結果とを連結して、読み出し信号に対するリードデータとして制御部10に出力する連結部23とを備える。

(もっと読む)

半導体メモリの制御方法

【課題】物理ブロックと論理ブロックのミスマッチに起因する書き込み性能低下を防止することを可能とした半導体メモリの制御方法を提供する。

【解決手段】nビットの物理ブロックを消去単位とする半導体メモリを、前記物理ブロックの容量より大きい2のべき乗で表されるmビットの論理ブロック単位でアドレス管理を行う半導体メモリの制御方法であって、前記論理ブロックを、先頭アドレスから連続するnビット部分を第1の管理単位として前記半導体メモリの物理ブロックに対応させ、残りの端数部分を第2の管理単位として複数個まとめて一つの物理ブロックに対応させる、というアドレス管理を行う。

(もっと読む)

半導体集積回路

【課題】フラッシュROMを搭載した半導体集積回路において、フラッシュROMのセクタを2つ以上使用しEEPROM機能を実現するに当たり、書き込み要求受理時に書き込み対象セクタがデータで埋め尽くされていると、転送が完了するまで書き込みが実行できない。

【解決手段】書き込み対象セクタの全領域を使用せず、データ領域と余裕領域とにあらかじめ設定しておく。かかる構成により、データ領域が空いている場合はそのままデータ領域にデータを書き込むが、データ領域が全て埋め尽くされている場合は、余裕領域と転送先領域の両方に同一のデータを書き込み、更新を行なう。更新時に、書き込み要求が発生した場合は更新を停止し、余裕領域と転送先領域の両方に同一のデータを書き込み、セクタ転送を再開する。

(もっと読む)

記憶媒体アクセス装置及び記憶媒体アクセス方法

【課題】アプリケーションが処理実行中に記憶媒体へのアクセス要求を受け付けても、それまで行っていたアプリケーションを周期時間内に終了することができ、しかもそのアクセス要求に基づくアクセス処理も滞りなく実行することができる記憶媒体アクセス装置及び記憶媒体アクセス方法を提供する。

【解決手段】アプリケーション15とデバイスドライバ16との間に、ミドルウェアとしてアクセスモジュール17を設ける。アクセスモジュール17は、アプリケーション15から関数の呼び出しを受け付けると、アプリケーション15が処理実行中であれば、これを一旦バッファリングする。アクセスモジュール17は、アプリケーション15の時処理が完了して次周期の処理を待つアイドル時間に入ると、それまでバッファリングしていた関数の呼び出しをデバイスドライバ16に出力し、このアイドル時間においてフラッシュロム13へのアクセスを実行する。

(もっと読む)

メモリ制御装置

【課題】使用する記憶容量の増加を抑制しつつ、コンピュータの立ち上げ時間の短縮化を図ることができるメモリ制御装置を提供すること。

【解決手段】CPUのキャッシュメモリに対する主記憶メモリの所定領域毎のキャッシング状態を保持するディレクトリメモリ内に、主記憶メモリの所定領域毎の初期化状態を表す初期化情報を記憶し、主記憶メモリの所定領域に対するアクセス時に、当該所定領域に対応するディレクトリメモリ内の初期化情報に基づいて、当該所定領域の初期化を行う初期化手段を備えた。

(もっと読む)

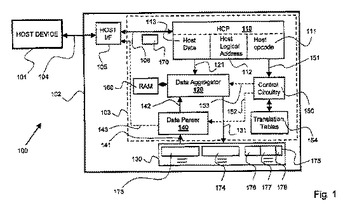

1セル当り単一ビットNANDフラッシュメモリをエミュレートする1セル当り多ビットNANDフラッシュメモリ用コントローラ

1セル当り単一ビットNANDフラッシュメモリデバイスをエミュレートする1セル当り多ビットNANDフラッシュメモリデバイスのコントローラを開示する。コントローラは、NANDホストデバイスからホストデータを受信するホストNANDインターフェイスと、ホストデータに補足データを統合することによりNANDフラッシュメモリデバイスのNANDフラッシュメモリセルアレイのデバイスページに記憶可能なデバイスデータを作成するデータ統合部とを含む。コントローラはデバイスデータを作成した後にNANDフラッシュメモリセルのデバイスページにデバイスデータを書き込む。コントローラはまた、データ読み出し操作を実行するときにデバイスデータからホストデータを解析するデータ解析部を含む。コントローラは、データ書き込み操作を実行するときに、必要に応じて、データ解析部を使用してデバイスデータから補足データを解析しデバイスデータを作成する。  (もっと読む)

(もっと読む)

記憶装置及びメモリ制御方法

【課題】データの書換え時の応答性能と、装置の許容書換え回数を十分に確保する。

【解決手段】不揮発性半導体メモリ2を制御する手段として、物理ブロックを少なくともデータページ222と交替ページ223とに分割し、ホスト装置3からの書込み要求毎に、新たな交替ページ223に書き込みを行う。また、交替ページ223が不足するときには、交替ブロック23に最新のデータを移し、同様の書込み制御を行う。

(もっと読む)

フラッシュメモリに最適化された入出力制御方法および装置

本発明は、フラッシュメモリに最適化された入出力制御方法および装置に関するものであって、より詳細にはフラッシュメモリの性能を向上させることができるフラッシュメモリに最適化された入出力制御方法および装置に関するものである。

本発明の実施形態によるフラッシュメモリに最適化された入出力制御方法は、フラッシュメモリにデータのランダムな記録演算が発生するかを判断する段階、および前記ランダムな記録演算が発生すると判断されると、ランダムに入力されるデータを前記フラッシュメモリの既設定された余分の領域に順次に記録する段階を含む。  (もっと読む)

(もっと読む)

コントローラの性能要件に基づくプログラミング

方法とソリッドステートドライブが開示される。例えばソリッドステートドライブは、3レベル以上のビットパターンをあらわすアナログデータ信号を送受信する(例えば、個々のビットを示すデータ信号を通信するデバイスと比べて、データ転送速度の増加を促進する)ように構成される。不揮発性メモリセルのアレイを含むソリッドステートドライブのプログラミングは、コントローラ回路の所望の性能レベルに応じてプログラムされる各メモリセルのレベルを調整することを含んでもよい。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 メモリマクロが搭載される半導体集積回路の設計期間および設計コストを削減する。

【解決手段】 インタフェース変換マクロは、コントローラから出力されるシステムインタフェース仕様に従った信号を、メモリインタフェース仕様に従った信号に変換し、メモリマクロに出力するとともに、メモリマクロから出力される信号を、システムインタフェース仕様に従った信号に変換し、コントローラに出力する。インタフェース変換マクロによりシステムインタフェース仕様およびメモリインタフェース仕様を相互に変換することにより、システムインタフェース仕様が異なる場合にも、半導体集積回路に共通のメモリマクロを搭載できる。したがって、システムを設計する際に、半導体集積回路の設計検証時間、評価時間および試験時間を短縮できる。この結果、半導体集積回路の設計期間および設計コストを削減できる。

(もっと読む)

不揮発性メモリのデータ処理装置及びその処理方法

【課題】トランザクションブロックを利用して複数のセクターに対して単位書き込みを支援し、トランザクションブロックを一括してデータブロックに変換してファイルシステムやデータベースの無欠性を保障することができる不揮発性メモリのデータ処理装置及びその処理方法を提供する。

【解決手段】複数のブロックを含む不揮発性メモリと、ユーザの書き込み作業要求時、前記ブロックにデータを書き込んだ後に前記データが書き込まれたブロックを一括して有効化させる作業処理部と、前記作業処理部の作業処理に対応して前記ブロックの状態を管理するブロック管理部とを有する。

(もっと読む)

フラッシュメモリのデータ更新方法、そのデータ更新プログラム、およびデータ書込み装置

【課題】写真処理装置に内蔵されているフラッシュメモリのデータ更新中にアクシデントが発生してもデータが全てなくなることがない、フラッシュメモリのデータ更新方法を提供することを目的とする。

【解決手段】フラッシュメモリのデータ更新方法であって、データ更新の際に、更新されるデータが記憶されている記憶領域を前記管理領域から検索し、前記検索結果に基づいて、前記管理領域に記憶されている管理情報を比較し、前記比較結果に基づいて、第1または第2記憶領域を決定し、前記決定された記憶領域にデータ更新を実行する場合に、先ず、一方の分割管理領域の管理情報を更新し、次いで、記憶領域のデータ更新を実行し、他方の分割管理領域の管理情報を更新することを特徴とする。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】1セクタ単位のユーザデータと、その付加データが書き込まれる領域をカラムアドレスが連続する領域に割り当てフラッシュメモリにデータを書き込む際、ブロックステータス領域にユーザデータや付加データが書き込まれてしまうことを回避する。

【解決手段】ホストシステム側から供給される1セクタ単位のユーザデータを保持する工程と、前記保持された前記ユーザデータを先頭データから順番に前記フラッシュメモリに転送する工程と、前記フラッシュメモリに転送された前記ユーザデータに対応する付加データを前記フラッシュメモリに転送する工程と、予め設定されたダミーデータを前記フラッシュメモリに転送する工程とを有し、前記ダミーデータを前記フラッシュメモリに転送する工程は、前記フラッシュメモリに転送されるデータの書き込み先がブロックステータスの記憶領域に対応するときにだけ実行される。

(もっと読む)

直列入力データを取り込む装置および方法

直列入力データ処理装置は、コマンド解釈をコマンドデコーダで高周波数にて行いながら、1ビットの損失もなく直列データを取り込む方法を提供する。定義済みシーケンスによる直列ビットの個々のバイトがラッチされ、ビットストリームが複数クロックと共に一時格納される。この一時格納は、アドレスを登録するために割り当てられたアドレスレジスタにバイト情報を転送する前に行われる。アドレス登録とデータ登録は、複数クロックの立ち上がり区間で直列入力の全ビットストリームをラッチすることにより実行される。高周波操作時(例えば、1GHzまたは1ナノ秒サイクル時間)においては、コマンドビットストリーム解釈と次のビットデータストリームの間に十分な時間的余裕をもってコマンド解釈中にビットデータを格納する目的のために追加レジスタが要求されることはない。  (もっと読む)

(もっと読む)

空データトークン指令を用いてストレージデバイス中のデータを管理するための装置、システム及び方法

装置、システム及び方法が、ストレージデバイス(150)での空データセグメント指令でデータを管理するために開示される。データを管理するための装置、システム及び方法は、書き込み要求受信モジュール(1302)及びデータセグメントトークンストレージモジュール(1304)を具える。書き込み要求受信モジュール(1302)は要求デバイス(1326)からストレージ要求を受信する。ストレージ要求はストレージデバイス(150)内にデータセグメントを記憶する要求を含む。データセグメントは反復する同一キャラクタの配列、又は反復する同一キャラクタ列の配列を含む。データセグメントトークンストレージモジュール(1304)はストレージデバイス(150)にデータセグメントトークンを記憶する。データセグメントトークンは少なくともデータセグメント識別子とデータセグメント長とを含む。データセグメントトークンはデータセグメントからのデータを実質的に含まない。 (もっと読む)

データベース管理方法、データベース管理装置、及びデータベース管理プログラム

【課題】機密情報を秘匿し、保護するデータベース管理方法を提供する。

【解決手段】データベース管理装置において、データベースに格納される機密情報に対するアクセスを管理するデータベース管理方法であって、データベース管理装置は、データベースに対するアクセス要求を受け付けるデータベース管理システムと、データベースの定義情報であるディクショナリとを格納し、ディクショナリは、データが格納される表を構成する列の属性に列に格納されるデータが機密情報であるか否かを示すための機密識別属性を含み、データベース管理装置は、データベースに格納されたデータの取得要求を受け付け、受け付けられたデータの取得要求を解析し、要求されたデータが格納される列の機密識別属性を参照し、要求されたデータが機密情報であるか否かを判定し、要求されたデータが格納される列に機密情報が含まれる場合には、列の射影を禁止する。

(もっと読む)

半導体集積回路及びシングルチップマイクロコンピュータ

【課題】書き込みデータサイズや書き込みモードの異なるプログラム格納不揮発性メモリ5、6とデータ格納不揮発性メモリ9とのいずれの書き込みを共通の不揮発制御ユニット8により実行すること。

【解決手段】シングルチップマイクロコンピュータ1は、メインCPU2、プログラム格納不揮発性メモリ5、6、データ格納不揮発性メモリ9、不揮発制御ユニット8を有する。書き込みデータサイズの大きなプログラム格納時と小さなデータ格納時にデータサイズ情報(H´80、H´40)と書き込みモード情報(H‘E8、H’E9)とがメインCPU2から不揮発制御ユニット8へ供給される。この情報に応答して不揮発制御ユニット8は、書き込みデータサイズの異なるプログラム格納不揮発性メモリ5、6とデータ格納不揮発性メモリ9とへの書き込みとモードの異なる書き込みとを実行する。

(もっと読む)

不揮発性メモリの書き込み方法

【課題】外部から書き込みを行うデータサイズによって、不揮発メモリの書き込み先を切り替えるとき、書き込み先が決定された後の書き込みデータの転送に要する時間を削減し、高速な書き込みを可能な不揮発性メモリの書き込み方法を提供する。

【解決手段】 独立して書き込み可能な複数の物理ページを有する不揮発性メモリ(104;106)にデータの書き込みを行う書き込み方法であって、不揮発性メモリ(104:106;109)に書き込みデータを転送するデータ転送ステップ(S204)と、データ転送ステップ(S204)の実行の後に不揮発性メモリ(104;106)に対して書き込み先の物理ページのアドレスを指定する第1の書き込みアドレス指定ステップ(S207)とを備える。

(もっと読む)

21 - 40 / 79

[ Back to top ]