Fターム[5C006FA51]の内容

Fターム[5C006FA51]の下位に属するFターム

高価な部品の回避 (131)

Fターム[5C006FA51]に分類される特許

1 - 20 / 1,090

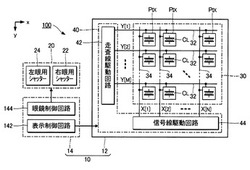

電気光学装置および電子機器

電気光学装置および電子機器

【課題】右眼用画像と左眼用画像との混在が観察者に知覚されることを抑制しながら表示画像の明度を向上させる。

【解決手段】複数の画素PIXは、複数の走査線32および複数の信号線34の各交差に対応して配置され、走査線32の選択時における信号線34の階調電位X[n]に応じた階調を表示する液晶素子CLを含む。各選択期間Hに走査線駆動回路42が選択する2本の走査線32に対応し信号線の延在方向に隣合う2個の画素PIXには、表示制御回路142に供給される表示データVが当該2個の画素PIXの各々に指定する階調の加重平均として算出される階調に応じた階調電位X[n]が、信号線駆動回路44より供給される。

(もっと読む)

液晶制御装置

【課題】安価な構成でカラー表示を実現する。

【解決手段】フレームバッファRAM204の2値表示データを順次取得し、ポート2(P2 207)により、表示用RAM5のRGBの各ドットのNビットのいずれかに送信し、また指定された表示エリアに対して、ポート3(P3 208)により階調データを出力し、ポート2とは異なる各ピクセルのNビットのいずれかにデータを入力することで、階調変換テーブルの設定値に応じてカラー表示が可能となり、ROM、RAM容量を削減した安価な構成でカラー表示を実現する。

(もっと読む)

圧縮画像データ処理装置及び画像表示装置

【課題】画像データを高圧縮率で圧縮した場合であっても、フリッカーの発生を最小化するとともに動画ぼやけを低減できる圧縮画像データ処理装置及び画像表示装置を提供する。

【解決手段】本発明に係る圧縮画像データ処理装置は、動画のぼやけが生じやすいのが画像のエッジ部分であることに着目して、エッジと判断された画素には、モード情報と量子化した画素情報を付与し、符号化に多くのビット数を割り当ててオーバードライブ処理を行う一方、平坦部分に対してはオーバードライブ処理を行わず、最小限の1ビットのモード情報のみを付与することで符号量を削減する。

(もっと読む)

タッチパネルを備えた液晶表示装置およびその駆動方法

【課題】LCDノイズの影響を低減することにより、誤動作を防止し、操作感を向上させることができるタッチパネルを備えた液晶表示装置およびその駆動方法を得る。

【解決手段】ホストコントローラ50から入力される水平同期信号に同期した水平制御信号を生成するタイミングコントローラ30Aと、LCD10に供給される共通電圧のフィードバック電圧および水平制御信号に基づいて、共通電圧を安定化制御するVcomフィードバック回路60Aとを備え、Vcomフィードバック回路60Aは、フィードバック電圧と所定の参照電圧とを比較するオペアンプと、オペアンプの反転入力端子と出力端子との間に接続された抵抗と、液晶ディスプレイの液晶書き込みに伴って発生するLCDノイズを低減するように、抵抗と協働して、オペアンプの反転入力端子と出力端子との間の抵抗値を調整するVcomフィードバック調整回路61と、を有する。

(もっと読む)

液晶表示装置

【課題】DACのためのカウンタクロック周波数を高くすることなく、またコスト増加を抑えた構成により、DACのビット数を増加する。

【解決手段】コンパレータ161は、カウンタ値とデジタル画像データの画素値とが一致した時に一致パルスを出力する。4入力1出力D/S162は、位相が90度ずつ異なる4本のコンパレータクロックCP1〜CP4の中から一つのコンパレータクロックをデジタル画像データの下位2ビットデータの値に基づいて選択する。DFF163は、選択された一本のコンパレータクロックの立ち上がりエッジのタイミングで一致パルスをラッチしてローレベルのゲート信号VSW_GATEをアナログSW164に出力し、これをオフに制御する。これにより、ランプ信号がサンプリングされる。このランプ信号のサンプリングレベルは、デジタル画像データをDA変換して得たアナログ信号電圧に相当する。

(もっと読む)

電力供給装置、液晶モジュールおよび電力供給装置の制御方法

【課題】液晶モジュールの内部回路の温度上昇を抑制すると共に、表示品質を維持しつつ、液晶モジュールのコストを低減する。

【解決手段】液晶モジュール1におけるソースドライバ3に電力を供給する電力供給装置10において、ソースドライバ3に供給する電流の電流値が所定の検出閾値を超えている場合、ソースドライバ3に供給する出力電圧の電圧値を降下して、ソースドライバ3に電力を供給する。

(もっと読む)

液晶表示装置

【課題】ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し且つ違和感の無い画像表示を実現する。

【解決手段】液晶セルと、ゲートドライバと、ソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、液晶セルにおけるソースラインの総数がソースドライバの出力ラインの総数よりも1本多く、液晶セルにおける最外側のソースラインは近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる。

(もっと読む)

表示装置

【課題】任意形状の面表示装置を容易に実現可能とする表示装置の提供。

【解決手段】走査回路の一段を構成する回路と、前記走査回路の出力に接続された画素回路とを含む表示装置要素を、一筆書きの要領で表示装置基板208に配設する。つまり、走査回路の一段を構成する回路と、前記回路の出力ノードに接続された画素回路とを含む表示装置要素を、表示装置基板208に連続して配設した構成とされる。これを駆動するために必要なクロック信号が1相のクロック信号である構成とする。

(もっと読む)

液晶表示装置および液晶表示装置の駆動方法

【課題】上下反転表示を実現するとともに表示品位の良好な液晶表示装置およびその駆動方法を提供する。

【解決手段】画素電極PEが配列した行に沿って延びたゲート線Gおよび補助容量線Csと、画素電極PEが配列した列に沿って延びた信号線Sと、ゲート線G、信号線S、および、補助容量線Csを駆動する駆動回路XD、YDと、を備えたアレイ基板ARと、アレイ基板ARと対向して配置された対向基板CTと、上下方向に並ぶゲート線Gを順次駆動する第1走査と、下上方向に並ぶゲート線Gを順次駆動する第2走査とを切替える走査方向制御信号UDと、補助容量線Csに供給する信号SCsの極性を制御する極性制御信号FRと、を供給し、第1走査を行う場合と第2走査を行う場合との極性制御信号FRが同じであるフレーム期間において、信号線Sへ供給する信号の極性を水平期間H単位で位相が異なるように駆動回路XD、YDを制御可能な制御回路と、を備える。

(もっと読む)

分散アパーチャディスプレイ

【課題】個々にアドレス可能ピクセルを使用するディスプレイによって示される視覚アーチファクトを低減するための方法及び装置を提供する。

【解決手段】ピクセルのアレイを備え、各ピクセルは可変の透過度又は輝度の切替可能領域32と、非切替可能領域34とを有する。各ピクセルの切替可能領域は、非切替可能領域の有意な部分によって少なくとも部分的に分離された少なくとも2つの同時切替可能部分に分散される。1次空間高調波及び視覚アーチファクトは有意に低減される。カラーディスプレイでは、各色のピクセルが同様に細分される。

(もっと読む)

ビデオフォーマット変換を有するタイミング制御部、その方法、並びにディスプレイシステム

【課題】 ビデオフォーマット変換を有するタイミング制御部のための方法が提供される。

【解決手段】方法は、2次元(2D)又は3次元(3D)ディスプレイモードを示す制御信号を受信するステップ、制御信号に応答して、ディスプレイパネルモジュールとディスプレイ制御ユニットとの間に結合されたタイミング制御部により、2D又は3D出力ビデオ信号を出力するステップ、を有する。出力するステップは、2Dディスプレイモードを示す制御信号に応答して、2D出力ビデオ信号を出力するステップ、3Dディスプレイモードを示す制御信号に応答して、3Dデータフォーマット変換ユニットにより、3D出力ビデオ信号を出力するステップ、を有する。

(もっと読む)

バックライト装置及びそれを備えた画像表示装置

【課題】画像表示パネルを照明するバックライト装置において、画像表示パネル上の映像のぶれ等の発生を抑制し、バックライトを部分的に調光できるようにし、製造コストの低減及び小型化を図る。

【解決手段】バックライト装置は、画像表示パネルの走査線と平行な線を基準としてグループ31A〜31Dに区分された複数のLED31と、画像表示パネルの垂直走査に同期させて、グループ31A〜31DのLED31を順次、間欠点灯させるスイッチング制御回路37と、LED31への供給電流量をグループ単位で調整するための電流調整回路38とを備える。電流調整回路38は、点灯タイミングの重ならないグループのLED31間で共用される。順次点灯により映像の残像効果を抑制できる。また、電流調整回路38によりLED31をグループ毎に調光でき、バックライト33を部分的に調光できる。しかも、電流調整回路38の共用により、回路数を低減できる。

(もっと読む)

バックライト装置、画像表示装置及びバックライト装置の制御方法

【課題】LEDパッケージ数を増やさずに、対応する光源を個別に制御可能な領域数を増加させることが可能なバックライト装置およびそれを用いた画像表示装置を得ること。

【解決手段】上記の目的を達成するため、本発明の一態様は、表示装置に用いられるバックライト装置であって、表示装置の表示範囲が複数に分割された分割エリア夫々に対応して設けられる複数のLEDパッケージと、照射された光を夫々のLEDパッケージが対応する分割エリアに拡散させる単一導光板103と、LEDパッケージを点灯制御するバックライト制御部601とを含み、LEDパッケージ102は、並列に接続された複数系統のLED及び発光させるLEDを切り替えるスイッチを含み、バックライト制御部601は、表示装置のフレーム周期を分割した分割期間毎に複数系統のLEDが点灯されるようにスイッチを制御することを特徴とする。

(もっと読む)

表示装置

【課題】拡大表示または縮小表示のためにスケーラによる画像処理を必要とせず、高速かつ高品位な拡大表示または縮小表示を可能とする表示装置を提供する。

【解決手段】第1解像度を有する第1表示パネルと、第1解像度に比して高い第2解像度を有する第2表示パネルと、第2表示パネルの一部に表示された画像の画像データを出力し、第1表示パネルに拡大画像を表示させる画像出力部と、を備える表示装置とする。

(もっと読む)

表示装置

【課題】クロック信号を停止させることなく双方向走査可能とすることにより、回路規模を縮小した双方向走査可能な表示装置を提供する。

【解決手段】表示装置は、並行する複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、初段出力回路は、複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、クロック信号である第1クロック信号が印加される第1クロック信号線と、第1クロック信号とは異なるクロック信号である第2クロック信号が印加される第2クロック信号線と、初段出力信号線がソースに接続され、第1クロック信号線がドレインに接続された第1トランジスタと、スタート信号線がゲートに接続され、スタート信号線が導通電位となることにより、第2クロック信号線と第1トランジスタのゲートとを導通させる第2トランジスタと、を備える。

(もっと読む)

表示装置

【課題】低コストで照明光の面内における部分的な出射をより細かくすることの可能な表示装置を提供する。

【解決手段】照明装置は、サイドエッジ型の照明装置であり、導光板と光源の他に、電位差に応じて、光源からの光に対して散乱性もしくは透明性を示す光変調層と、光変調層を挟み込む第1電極および第2電極とを有している。第1電極および第2電極は、ともに、複数の帯状電極からなる。第1電極の帯状電極と、第2電極の帯状電極とは、互いに交差する方向に延在している。駆動回路は、二次元映像、三次元映像、または二次元映像と三次元映像とを混在させた映像を表示パネルに表示させる際に、第1電極の帯状電極と、第2電極の帯状電極との電位差の面内分布が1フレーム期間内で一定となるように、各帯状電極を駆動するようになっている。

(もっと読む)

表示装置

【課題】端子設定により、一対の伝送線路の終端方法を切り替える。

【解決手段】各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(もっと読む)

虚像表示装置

【課題】使用感を向上させることができる虚像表示装置を提供する。

【解決手段】虚像表示装置1は、画像光を出射する表示素子6と、前記表示素子6からの画像光を投射する投射レンズ71と、前記投射レンズ71からの画像光を所定位置に導く導光部3と、前記投射レンズ71に対して前記表示素子6を回転可能に支持する回転機構9とを備えている。表示素子6には、当該表示素子6による表示を制御する表示制御手段が設けられてもよい。

(もっと読む)

階調電圧生成回路、画像表示装置及びプロジェクター

【課題】コストを低減し、後段の回路等に対するダメージを防ぐことが可能な階調電圧生成回路、画像表示装置及びプロジェクターを提供する。

【解決手段】インピーダンス変換部56と階調電圧生成部52とを結ぶ配線L1〜L9には、接地電圧との間に、基準電圧Vref1〜Vref9を安定させるためのコンデンサーC1〜C9が接続されている。また、両端の演算増幅器A1,A9と階調電圧生成部52とを結ぶ配線L1,L9には、演算増幅器A1,A9とコンデンサーC1,C9との間に、所定の抵抗値を有する抵抗器R1,R9が配置されている。つまり、演算増幅器A1,A9の出力端子と、階調電圧生成部52の第2の分圧部57とは、抵抗器R1,R9を介して接続されている。この抵抗器R1,R9は、起動時に、第2の分圧部57に供給される基準電圧Vref1,Vref9の立ち上がりを遅くする作用を有している。

(もっと読む)

1 - 20 / 1,090

[ Back to top ]