Fターム[5E070CB11]の内容

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | インダクタンス、トランスの形成 (1,197)

Fターム[5E070CB11]の下位に属するFターム

パターン自体で形成するもの (387)

パターンの積層(積層コイル) (702)

パターンの折り畳み (15)

パターンの巻回 (34)

巻線コイルと組み合わせるもの (8)

Fターム[5E070CB11]に分類される特許

21 - 40 / 51

ノイズフィルタ

【課題】新たな部品を追加することなくプリントパターンだけで、コモンモードチョークコイル間の浮遊容量を小さくしてフィルタ特性の改善を図る。

【解決手段】電力変換器を含む電気機器の交流電源ラインまたは入力電流整流後の直流ラインに挿入され、少なくとも2つのコモンモードチョークコイル2A,2Bおよびコンデンサ(図示なし)を含む素子から構成され、これらの素子をプリント配線基板1に実装して構成されるノイズフィルタにおいて、プリント配線基板1のコイルやコンデンサ等の素子を実装する面をほぼベタパターン4Aとし、このベタパターン4Aをアース電位に接続するようにする。

(もっと読む)

インダクタ

【課題】輻射ノイズが大幅に低減されるとともに実装スペースを有効利用でき、球状コアよりも製造容易で製造コストがかからないインダクタを実現することを課題とする。

【解決手段】

高透磁率又は高飽和特性の磁性体コアと、磁性体コアの内部に一体的に埋設されたコイル素子とを有するインダクタにおいて、磁性体コアは底面が角数5以上の正多角形の多角柱構造を有することを特徴とするインダクタによって課題を解決する。これにより底面の各角度は90度よりも大きくなる。

(もっと読む)

インダクタおよび表面実装型デバイス

【課題】高温耐久性の高いデバイスを提供する。

【解決手段】回路基板2と回路基板2に実装された複数の回路素子3とをモールド樹脂5により封止したパッケージ8を有する表面実装型のデバイス1であって、デバイス1の回路素子3に含まれるインダクタ10は、磁性成型体11と、磁性成型体11に内蔵されたコイル15とを備え、さらに、磁性成型体11は、回路基板2に面した実装側の面(下面)11bと、実装側の面の反対側の面(上面)11aと、上面11aを囲うように設けられた第1の斜面であって、上面11aに対して後退するように傾いた第1の斜面51とを含むデバイス。

(もっと読む)

コモンモードフィルタ

【課題】コモンモードフィルタの大きさに影響を与えずに、コモンモードチョークコイルの特性インピーダンスを調整できるコモンモードフィルタを提供する。

【解決手段】基板101と樹脂積層部110と基板109とがこの順で積層された積層体を有し、樹脂積層部110は、スパイラル導体151,152と、スパイラル導体151,152それぞれを外部電極と接続する引出導体151a,151b,152a,152bと、平面導体P1〜P6とが形成され、平面導体P1は、樹脂積層部110内の、スパイラル導体151の外周形と積層体を構成する各層の外形との違いによって生ずる第1の余白領域(又は引出導体151aの形成によって生ずる第2の余白領域)に形成され、平面導体P2は、平面導体P1と積層方向で対向する位置に形成されることを特徴とする。

(もっと読む)

積層型誘電体フィルタ

【課題】 高周波信号成分に対する阻止帯域の減衰量が十分にとれた、信号の選択性に優れる積層型誘電体フィルタを提供する。

【解決手段】 複数の誘電体層が積層されてなる積層体1と、積層体1の外面に被着されている入出力端子電極3,4およびグランド端子電極2と、積層体1の内部で誘電体層間に配置され、一端が入出力端子電極3,4と電気的に接続されているコイル導体5,6と、積層体1の内部で積層方向においてコイル導体5,6の上下に位置する誘電体層間1a−1b,1l−1mに、積層方向に見たときにコイル導体5,6が配置されている領域の外側に配置され、グランド端子電極2と電気的に接続されている環状グランド導体7とを具備する積層型誘電体フィルタ10である。コイル導体5,6による容量が小さく、デジタル信号回路に利用することが可能で、環状グランド導体7により外部からの電磁波ノイズが充分に除去される。

(もっと読む)

インダクタンス素子及びその製造方法

【課題】小型薄型でQ値が高く、量産性に優れているインダクタンス素子及びその製造方法を提供すること。

【解決手段】基板1に設けられた磁性体部2と、この磁性体部2をコイル状に取り囲むように接続されているコイル導体3,4とを備え、磁性体部2は、磁性体層2aと非導体層2bとが周期的に繰り返されている構造を有している。磁性体層2aは、非導体層2bに形成された複数の溝部2cに沿って設けられている。

(もっと読む)

インダクタンス素子及びその製造方法

【課題】小型薄型でQ値が高く、量産性に優れているインダクタンス素子及びその製造方法を提供すること。

【解決手段】基板1に設けられた磁性体2bと、基板1を貫通するスルーホール3aに埋め込まれた接続導体3bを備えており、基板1の上下面の少なくとも一方より掘り込まれた溝部2aに磁性体2bが設けられ、基板1の上下面に設けられたパターン導体5a,5bと基板1を貫通して設けられた接続導体3bとが、磁性体2bをコイル状に取り囲むように接続されている。

(もっと読む)

転写用導体の製造方法および電鋳母型

【課題】本発明は、小型化、高インピーダンス化を図ることができる転写用導体の製造方法を提供することを目的とするものである。

【解決手段】本発明の転写用導体の製造方法は、導電性を有するベース板21上に、このベース板21の表面の露出部23を規定するパターンを有する感光性のフォトレジスト膜22を形成する工程と、前記ベース板21上の前記露出部23にめっきをすることによって転写用導体25を形成する工程と、前記転写用導体25を被転写体26に転写する工程とを備え、前記フォトレジスト膜22を形成した後、転写用導体25を形成する前に、前記フォトレジスト膜22に紫外線を照射するようにしたものである。

(もっと読む)

電子部品及びその製造方法

【課題】基板内部の配線と、基板表面に形成される導体との間の電気的断線を回避でき、しかも低温焼成可能な電子部品を提供する。

【解決手段】第1の絶縁層と、第2の絶縁層と、外部接続電極とを有する電子部品であって、前記第1の絶縁層は、複数であって、その内部に内部導体を有する基板を構成し、それぞれは、セラミック成分及びガラス成分を含む複合組成物であり、第2の絶縁層は、樹脂を含み、前記第1の絶縁層上に設けられ、前記外部接続電極は、前記第2の絶縁層上に設けられ、前記内部導体に接続される配線導体を構成している。

(もっと読む)

平面型広帯域トランス

【課題】平面型広帯域トランスの一次コイルと二次コイルの並列コイルを配置する方法及び製造方法を提供する。

【解決手段】帯域幅をDC〜GHzに広げ、コアの透磁率が大幅に減少する場合高周波結合を可能にし、広帯域幅にわたって低反射エネルギ及び低損失を実現するように、平面型広帯域トランスの一次コイルと二次コイルの間隔及び幅を配置する。所定パターンの孔対を有する下側モールドに導体素子を垂直に挿入し、導体素子の中間部が上側モールドと下側モールドとの間に延在するように該上側モールドを取り付ける。中間部を絶縁材料で覆う。モールドの押しのけ部は空間を作る。該空間にフェライト素子を堆積させる。第2の上側モールドを下側モールドとつなぎ、絶縁材料を堆積させ、成形アセンブリを作成する。塗布された所定パターンの導電コーティングが導体素子の端部同士を接続し、トランスのコイルを画定する。

(もっと読む)

薄膜トランスおよびその製造方法

【目的】占有面積を拡張することなく、エネルギー変換効率を容易に向上できる薄膜トランスとその製造方法を提供すること。

【解決手段】シリコン基板1上に形成したシリコン酸化膜2、5、7である絶縁膜内に渦巻き状(平面スパイラル状)の1次コイルを構成する第1コイル導体4、2次コイルを構成する第2コイル導体6が互いに横方向に対向するように形成する。コイル導体4、6の幅を垂直方向にとれるので占有面積を拡張することなく、エネルギー変換効率を容易に向上できる。

(もっと読む)

受動素子及びその製造方法、受動素子の実装構造及びその実装方法

【課題】インダクタ、電気抵抗等を薄型化及び小型化し、特性値を可変できる受動素子を提供すること。

【解決手段】封止材25の一方の面に一方向に沿って互いに分離して配置された複数の薄膜導体10と、前記一方向に沿って互いに分離して配置され、封止材25に少なくとも一部分が埋設された複数のワイヤ導体12−1とを有し、薄膜導体10とワイヤ導体12−1とが接続されてコイル状導体を形成したインダクタ部品34。この受動素子では、外部に露出する薄膜導体10のいずれかを端子として選択することによって、特性値を可変にできる。

(もっと読む)

積層インダクタ

【課題】 プリント基板に実装する際に端子電極の方向を判別する必要がなく、既存のサイズの巻線インダクタと同等の磁気特性が容易に得られる積層インダクタを提供する。 【解決手段】 積層インダクタ1の正方形状の底面13には、極性がない4個の端子電極2a,2b,2c,2dが、底面13の中心に対して90度回転対称位置に設けられている。4個の端子電極2a,2b,2c,2dは、全て同一形状をなしており、底面13の4辺の周縁部にそれぞれ1個ずつ設けられている。対向する2個の端子電極2a,2cそれぞれは、同方向(反時計回り方向)に90度回転した位置に設けられた2個の端子電極2b,2dそれぞれと、積層体の内部で接続されている。 (もっと読む)

コイル部品とその製造方法

【課題】本発明は、携帯電話等の各種電子機器に用いられるコイル部品のQ値向上を目的とする。

【解決手段】そして、この目的を達成するために本発明は、柱状の支持体3と、この支持体3の中央部表面に設けたコイル6Aと、支持体3の両端部表面に設けた電極4Aとを備え、コイル6Aが上層6AAと下層(図示せず)とを有し、この下層(図示せず)の導電率と電極4Aの導電率とが等しく、電極4Aの導電率が上層6AAの導電率よりも低いコイル部品。

(もっと読む)

高QプレーナインダクタおよびIPD応用例

【課題】高いクオリティ(Q)ファクターを有するプレーナインダクタを生産するための方法および装置を提供すること。

【解決手段】このインダクタは、第1の比較的広いコイルターンと、第1のコイルターンによって占有されたものと異なる平面内で変位された少なくとも1対の比較的狭い方の第2のコイルターンとを準備することによって形成される。そのようなコイルターンの構成により、コイルターンの間で高い値の相互結合が生じ、高いクオリティ(Q)ファクターを有するインダクタが得られる。

(もっと読む)

導体パターン形成方法およびその導体パターンを形成する成形型、導体パターン

【課題】導体パターンを作成するにあたり、少ない工程で容易かつ安価に微細導体パターンを作成することを目的とし、また、製造工程での精度低下を無くし精度良い微細導電パターンを作成することを目的とする。

【解決手段】所定のパターンに対応した凹部31aを有する樹脂層31からなる成形型30を用いて、凹部31aに金属ガラス50を対向させ、金属ガラス50をそのガラス遷移温度Tgより高い温度でかつ樹脂層31の耐熱温度より低い温度に加熱する。加熱された金属ガラスを成形型30に圧着して凹部31aに金属ガラス50を充填させ(51)、金属ガラスを冷却する。金属ガラスのうち凹部に充填された部分(51)を残して金属ガラスを取り除き導体パターンを形成する。

(もっと読む)

複合積層型電子部品

【課題】 バリスタ素子部と、インダクタ素子部とをクラックの発生等が生じることなく確実に接合・一体化させることができ、しかも、接合のための接合中間層の厚さを極力薄く設定することができ、部品のコンパクト化が図れる複合積層型電子部品を提供する。

【解決手段】 バリスタ素子部(10)と、インダクタ素子部(20)と、これらの双方の素子部を接合するために介在される接合中間層(50)とを有し、その接合中間層(50)は、組成の異なる第1番目から第N番目までのN層(Nは2以上の整数)の接合膜を積層することにより構成されるとともに、それらの総和厚さが240μm以下であり、インダクタ素子部と、これに接する第1番目の接合膜との相互の線膨張率の差が1(ppm/K)以内であり、それ以外のN−1箇所の接合界面を構成する隣接する接合膜同士の相互の線膨張率の差が2(ppm/K)以内であり、バリスタ素子部と、これに接する第N番目の接合膜との相互の線膨張率の差が2(ppm/K)以内に構成される。

(もっと読む)

平面コイルの製造方法

【課題】本発明は、平面コイルの製造方法に関するものであり、大判シートにおける高速めっき化と、個片シートの重量測定による直流抵抗値の高精度化により、平面コイルの高精度化と生産性の向上を実現することを目的とするものである。

【解決手段】本発明は、大判シート3によりパターニングされた平面コイルを個片シート10に切断し、個片シート10の重量測定により個片シート10毎に直流抵抗値を調整する平面コイルの製造方法である。

(もっと読む)

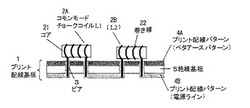

3次元スパイラルインダクタを内蔵したプリント基板およびその製造方法

【課題】小さな面積でも大きなインダクタンス値が得られる3次元スパイラルインダクタ内蔵型プリント基板およびその製造方法を提供する。

【解決手段】複数の絶縁層および導体層を含んでなるプリント基板において、前記複数の導体上に、互いに平行なストリップ状にパターニングされ、同一の垂直面上に位置し、基板の中心層から外側に行くほど長さが増加する、伝導性物質からなった複数のコイル導体パターンと、前記中心層に対して対称な前記導体層に位置する前記コイル導体パターン間を電気的に接続して、前記コイル導体パターンとともにスパイラル状のインダクタを形成する複数の導電性スルーホールと、前記複数のコイル導体パターンと前記複数の導電性スルーホールからなる前記スパイラルインダクタの始点および終点にそれぞれ接続され、外部電源を供給するための一対のリードアウトパターンとを含む。

(もっと読む)

フェライト材料及びインダクタ素子

【課題】基本配合組成Ni−Cu−Zn系フェライト材料の初透磁率の温度特性を改善する。

【解決手段】40〜50モル%のFe2O3、5〜35モル%のNiO、1〜32モル%のZnO、及び5〜15モル%のCuOを基本組成とするNi−Zn−Cu系のフェライト材料に、3.0〜8.0モル%のSnO2を含有させことにより、初透磁率の温度特性を大幅に改善することができる。

(もっと読む)

21 - 40 / 51

[ Back to top ]