Fターム[5E343ER11]の内容

プリント配線の製造 (50,760) | その他の関連処理方法 (3,993) | レジスト処理 (1,145)

Fターム[5E343ER11]の下位に属するFターム

Fターム[5E343ER11]に分類される特許

81 - 100 / 142

銅のエッチング処理方法およびこの方法を用いてなる配線基板と半導体パッケージ

【課題】配線基板の微細配線形成、特に、L/S=15μm/15μm以下または配線厚み15μm以下の微細配線形成が可能な銅のエッチング処理方法およびこの方法を用いてなる配線基板を提供することである。

【解決手段】銅をエッチング処理する方法であって、銅を酸化処理して酸化銅とする工程、その後、前記酸化銅を酸性溶液で溶解する工程を有する、銅のエッチング処理方法。

(もっと読む)

導電性パターンの形成方法、配線板の製造方法及び配線板

【課題】環境負荷が少なく、大面積を連続的に生産することが可能となる導電性パターンの形成方法、配線板の製造方法及び配線板を提供する。

【解決手段】基板11の表面に、導電性パターンを形成する導電性パターンの形成方法であって、疎水性の表面を有する基板11を選択し、基板11の表面のうち導電性パターンを形成する導電性パターン形成部12に親水化処理を施す親水化処理工程と、基板11の表面に、金属粒子、バインダー、溶媒を含む親水性の溶液14を接触させ、親水化処理が施された導電性パターン形成部12に選択的に溶液14を付着・固化させて金属粒子層14Aを形成する金属粒子層形成工程と、金属粒子層14Aが形成された基板11の表面に、無電解めっきあるいは電解めっきを施してめっき層を形成するめっき工程とを、備えたことを特徴とする。

(もっと読む)

回路パターン形成方法

【課題】インプリント技術やフォトリソグラフィー技術を用いて回路パターンを形成するためには、下地に金属膜を形成し、さらにエッチング工程を必要とする。

【解決手段】本発明は、インプリントされた樹脂パターン8が形成された、透明な3基板の背面から光を照射し、光CVD法により樹脂パターン8の無い凹部にだけ選択的に導体パターン(光CVD膜パターン6)を形成する。樹脂パターン8部においては、基板背面から照射された光が吸収または遮光されるので、光CVD反応は起こらない。

(もっと読む)

パターン修正方法およびパターン修正装置

【課題】10μm前後の細線で電極断線部などを修正することができ、かつ、欠陥部周辺の汚染が小さなパターン修正方法を提供する。

【解決手段】このパターン修正方法では、孔3aの開いたフィルム3をマスクとして電極2のオープン欠陥部2aに修正ペースト7を塗布する場合に、フィルム3の厚さFtと孔3aの短軸長Swとの関係をFt>Swにする。これにより、修正ペースト7を孔3a内に保持する力を強くすることができ、孔3aに塗布された修正ペースト7がフィルム3と基板1との隙間に吸い込まれることを防止することができる。

(もっと読む)

レジスト膜形成方法およびレジスト膜形成装置

【課題】微細配線形成を可能とする低コストで省資源なレジスト膜形成方法を提供する。

【解決手段】光触媒膜12を形成した支持基板11を準備し、光触媒膜の一部に光14を照射し、その光照射領域を親水性に変化させることにより、光触媒膜12の膜表面に所定パターンの親水領域15を形成し、光触媒膜12上にレジストを塗布して撥水領域15a上のレジストを選択的に親水領域15上に集合させることにより、所定パターンのレジスト膜16を形成する。また、レジスト膜被転写用基板27に支持基板11上のレジスト膜16を密着させ、その支持基板11を除去して基板27にレジスト膜16を転写する。親水領域15を再び撥水領域に復元することにより、支持基板11を繰り返し再利用する。

(もっと読む)

フレキシブルプリント配線板及び液晶モジュールのバックライト装置

【課題】電気的特性の良好なFPCを低コストに提供する。

【解決手段】FPCは、ベースフィルム上の導体層のエッチングによって形成される導体ライン5〜12と、該導体ラインの部品実装部に電解メッキ処理によって形成される導体ランドパターン24と、アイランド型の導体ライン6,7,10,11から延びてFPC外周部に至るメッキ用導通線6a,7a,10a,11aとを有する。FPC外周部に、FPCの端面ラインよりも内側に後退する凹部25を設け、メッキ用導通線6a,7a,10a,11aの末端が該凹部25に位置する。

(もっと読む)

配線回路基板およびその製造方法

【課題】伝送特性を悪化させることなく導体パターンとカバー絶縁層との接着性を向上することが可能な配線回路基板およびその製造方法を提供する。

【解決手段】ポリイミドフィルムからなるベース絶縁層1上に例えば電解銅めっきにより所定の導体パターン2が形成される。導体パターン2上の一部の領域を除いて当該導体パターン2を覆うようにカバー絶縁層6が形成される。すなわち、導体パターン2上の上記一部の領域が端子用開口部7となり、カバー絶縁層6により覆われていない導体パターン2の部分が端子部となる。導体パターン2上の上記一部の領域には電解金めっき層10が形成される。端子用開口部7の外側の周縁における導体パターン2上の一部の領域に粗化部5が形成される。

(もっと読む)

配線回路基板およびその製造方法

【課題】伝送特性を悪化させることなく導体パターンとカバー絶縁層との接着性を向上することが可能な配線回路基板およびその製造方法を提供する。

【解決手段】屈曲部100aおよび2つの非屈曲部100bに渡ってベース絶縁層1上に所定の導体パターン2が形成される。粗化レジスト4が形成されていない屈曲部100aにおける導体パターン2の表面に、例えば凹凸形状を有する粗化部5が形成される。粗化処理用の処理液として、例えば、硫酸と過酸化水素との混合液、アルカリ−亜塩素酸系の処理液、または有機酸系の処理液を用いることができる。また、粗化部5の表面粗さ(算術平均高さ)Raは、1μm〜3μmであることが好ましい。そして、導体パターン2上の端子用開口部の領域を除いて、ベース絶縁層1および導体パターン2上に例えばポリイミドからなるカバー絶縁層6が形成される。

(もっと読む)

アルカリ可溶性樹脂層処理液、アルカリ可溶性樹脂層除去方法、レジストパターンの形成方法及び回路基板の製造方法

【課題】回路基板の貫通孔の孔径の大小に係わらず、サイドエッチ量が変わらず、かつ現像残渣の発生がないレジスト像を形成することができるアルカリ可溶性樹脂層処理液、アルカリ可溶性樹脂層除去方法、レジストパターンの形成方法及び回路基板の製造方法を提供する。

【解決手段】アルカリ金属炭酸塩、アルカリ金属リン酸塩、アルカリ金属水酸化物、アルカリ金属ケイ酸塩から選ばれる無機アルカリ化合物のうち少なくともいずれか1種を高濃度で含み、さらに、硫酸塩または亜硫酸塩のうち少なくともいずれか1種を適量含むアルカリ可溶性樹脂層処理液と、この処理液を用いたアルカリ可溶性樹脂層除去方法と、このアルカリ可溶性樹脂層除去方法を用いたレジストパターンの形成方法及び回路基板の製造方法である。

(もっと読む)

パターン形成材料及びパターン形成方法

【課題】薄膜感光層であっても、優れた厚み均一性と基板への密着性とを両立することができるため、高解像度であり、かつ、感度と現像許容性とに優れ、高精細なパターンを形成可能なパターン形成材料、及び該パターン形成材料を用いたパターン形成方法の提供。

【解決手段】支持体と、該支持体上に感光層とを少なくとも有してなり、前記感光層が、バインダー、重合性化合物、光重合開始剤及びフッ素系界面活性剤を少なくとも含んでおり、前記バインダーが、分子中にカルボキシル基を含有する共重合体と、1分子中に1つのエポキシ基を有する飽和エポキシ化合物との開環付加反応物であり、ガラス転移温度(Tg)が300〜400Kであり、かつ、質量平均分子量が1,000〜10,000であり、前記感光層の厚みが、3〜10μmであることを特徴とするパターン形成材料、及び該パターン形成材料を用いたパターン形成方法である。

(もっと読む)

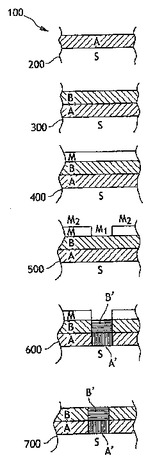

特性が制御された多層構造物の製造方法

本発明はn層の所定材料の元素状活性層(nは2以上の整数)を含む多層構造物を支持体上に製造する方法(100)に関する。この方法は、第1の元素状材料活性層の成膜工程(200)と、n番目の元素状材料活性層の成膜工程(300)とを含む方法であって、特性が制御された多層構造物を得るために、成膜されたn層の材料元素状活性層上に、n層の元素状活性層のそれぞれの個々の特性を変性させるのに適したイオン種をレジストを介して注入する単一の工程(600)を含むことを特徴とする。  (もっと読む)

(もっと読む)

粒子堆積方法

【課題】本願発明は、従来のスクリーン印刷やめっき方法とは異なる方法によって、電子部品のバンプ等の導電部を簡易かつ効率的に形成可能とする技術を提供する。

【解決手段】 本願発明は、開口部を有するレジストで被覆された基材を、粒子を分散させた懸濁液に浸漬し、懸濁液中の粒子を開口部に堆積させる方法であって、懸濁液は、分散させた粒子が沈降して開口部に堆積するような粘性を有し、基材を該懸濁液に浸漬して、粒子を開口部に堆積させることを特徴とする粒子堆積方法に関する。よって、本願発明では、基板の開口部に比較的短時間で均一に粒子を堆積させることが可能となる。また、レジスト上に残留した余剰な粒子についても簡易的に取り除くことができるため、電子部品において所望の形状を備えたバンプ等の導電部を形成することが可能となる。

(もっと読む)

プリント配線板製造方法及びプリント配線板

【課題】回路パターンの高さの均一性を必要とする箇所において、回路パターンの高さが均一なプリント配線板を提供する。

【解決手段】絶縁基材の表面上に導電性のシード層を形成する工程と、シード層上にレジスト層を形成する工程と、レジスト層に回路形成用パターンをパターンニングしてメッキ用レジスト層を形成する工程と、メッキ用レジスト層の回路形成用パターンで高さの均一性を必要とする箇所にカバー材を配置する工程と、シード層から成長させたメッキをカバー材で制限して回路パターンを形成する工程と、メッキ用レジスト層及びカバー材を除去する工程と、回路パターンが形成された部分以外のシード層を除去する工程とを含む。

(もっと読む)

ポリイミド表面への金属パターン形成方法およびスルーホールを有するポリイミド配線基板の製造方法

【課題】高い密着性と、高いパターン精度で、ポリイミド表面に金属パターンを形成することができる、ポリイミドへの金属パターン形成方法を提供する。

【解決手段】ポリイミド表面の金属パターンを形成しない領域にアルカリ性水溶液に溶解しない疎水性物質を付着させ、疎水性物質が付着していない領域に選択的にアルカリ性水溶液を塗布し、この水溶液を塗布した領域に前記アルカリ金属イオンとは異なる金属イオンを含有する水溶液を接触させることによってカルボン酸金属塩の層を生成し、次いで、カルボン酸金属塩を還元して金属薄膜からなる金属パターンを形成する。

(もっと読む)

導電性回路の形成方法

【課題】マスキング材と基体との双方が高周波信号に対して誘電正接が低く、両者の密着性に優れる導電性回路を簡易かつ低コストで形成できる。

【解決手段】軟質重合体を混合分散したシクロオレフィン系樹脂を射出成形して一次基体1を形成し、その表面上に相溶性がある、軟質重合体を混合しないシクロオレフィン系樹脂を射出成形してマスキング層2を形成する。シクロオレフィン系樹脂自体は耐エッチング性を有するため、マスキング層2で覆われていない一次基体1の表面、すなわち導電性回路を形成すべき部分1aだけについて軟質重合体を溶解させて粗化できると共に親水性となる。したがってマスキング層2で覆われていない部分1aにのみ、選択的に無電解めっきによる導電層4が形成できる。

(もっと読む)

めっき配線基板および無電解めっき方法

【課題】透明基材の被処理面に粗面化処理を施すことなく、少量かつ十分の量の触媒層を透明基材に付着させることにより、透明基材に対してめっき膜を確実に密着させることができるとともに、非めっき膜形成部において触媒層を除去しなくても、透過率がよく、光学的特性が良好なめっき配線基板を形成する方法と配線基板の提供。

【解決手段】透明基材2に、錫化合物を接触させる錫処理工程と、錫処理工程の後、透明基材2に銅化合物を接触させる銅処理工程と、銅処理工程の後、透明基材2にパラジウム化合物を接触させて触媒層5を形成するパラジウム処理工程と、触媒層5上に任意のパターンの銅めっき膜3を形成するめっき処理工程とを有し、触媒層5におけるパラジウム化合物の付着量を、1×1013〜5×1014atms/cm2とし、非めっき膜形成部7に形成されたレジスト8の表面高さと銅めっき膜3の表面高さとを同一高さ位置に形成する。

(もっと読む)

フリップチップ実装用回路基板とその製造方法、並びに半導体装置とその製造方法

【課題】半導体素子と回路基板の接続信頼性を確保できるフリップチップ実装用回路基板を提供する。

【解決手段】基板表面に配線パターン1と、フリップチップ実装用の接続パッド2と、接続パッド2上に開口部4が形成されたソルダレジスト3とを備えたフリップチップ実装用回路基板において、開口部4内に導電性を有する物質5を形成する。

(もっと読む)

配線基板の製造方法、配線基板の中間製品

【課題】めっき厚のばらつきが抑制されるため良品率を向上できるにもかかわらず、高コスト化を伴わない配線基板の製造方法の提供。

【解決手段】本発明の配線基板は、準備工程及び配線層形成工程とを経て製造される。準備工程では、製品となるべき部分27が複数配置された製品形成領域28と、製品形成領域28の周囲を取り囲む枠部29とからなる配線基板の中間製品11を準備する。中間製品11の枠部29は、第1縁部21と、製品形成領域28を挟んで第1縁部21の反対側に位置する第2縁部22とを有する。第1縁部21には第1メッシュ導体層81が形成され、第2縁部22には第1メッシュ導体層21よりも面積率が低い第2メッシュ導体層82が形成される。配線層形成工程では、中間製品11を電解めっき浴に浸漬してパターンめっきを行い、製品となるべき部分27に配線層62,72を形成する。

(もっと読む)

配線基板及びその製造方法

【課題】 ホイスカの発生がなくて信頼性が高く、ワイヤボンディング性や半田濡れ性の改善された配線基板を確実な方法で得る。

【解決手段】 セミアディティブ法により絶縁体表面にメッキ層からなる銅配線を設けた配線基板であって、該メッキ層からなる銅配線表面の表面粗さ(Rz)が0.25μm以下の配線基板とする。銅配線は絶縁体表面にメタライズ層もしくはシード層とメタライズ層とを介して設けるのが好ましい。銅配線表面の表面粗さ(Rz)が0.25μm以下にするには、組成が、硫酸濃度5〜50g/l、過酸化水素濃度10〜60g/l、塩素濃度5〜40ppmであるフラッシュエッチング液を使用して、銅メッキ層をフラッシュエッチングする。

(もっと読む)

立体回路基板の製造方法

【課題】立体回路基板の製造方法において、環境に対する負荷が少ない方法で、強固な下地密着性を有する回路の形成を可能とする。

【解決手段】成形体の表面に回路を備えた立体回路基板を製造する方法であって、所望の立体形状の成形体を形成する成形体形成工程(S1)、成形体の表面にレジスト膜を形成するレジスト膜形成工程(S2)、レジスト膜から回路となる部位のレジスト膜をレーザ光を用いて除去してパターンを形成するパターン形成工程(S3)、レジスト膜を含む成形体の表面に下地膜となるチタン膜を形成する下地膜形成工程(S4)、レジスト膜を除去することによりレジスト膜の表面に形成されたチタン膜を除去する不要部除去工程(S5)、成形体の表面に残ったチタン膜の表面にめっきを施すことにより回路を形成するめっき膜形成工程(S6)、を含んでおり、この順番で実施される。

(もっと読む)

81 - 100 / 142

[ Back to top ]