Fターム[5F004EA03]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380)

Fターム[5F004EA03]の下位に属するFターム

Fターム[5F004EA03]に分類される特許

141 - 160 / 430

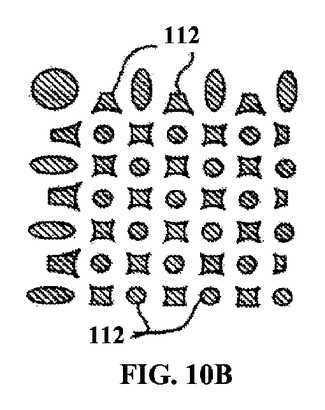

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

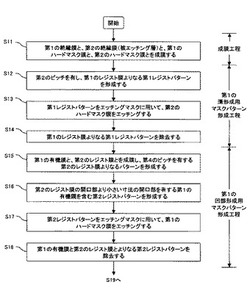

【課題】デュアルダマシン法による解像限界以下の溝(トレンチ)及び凹部(孔又はビア)のパターンをCD値を高精度に形成することができる半導体装置の製造方法を提供する。

【解決手段】被エッチング層上に、第1のハードマスク膜と、第2のハードマスク膜とを成膜する成膜工程S11と、第1のピッチを有し、第2のハードマスク膜よりなるパターンであって、溝のパターンを形成する際のエッチングマスクとなる溝形成用マスクパターンを形成するための第1の溝形成用マスクパターン形成工程S12〜S14と、第4のピッチで設けられた開口部を有する第2のレジスト膜と、第2のレジスト膜の開口部と連通し、第2のレジスト膜の開口部の寸法より小さい寸法の開口部を有する第1の有機膜とよりなる第2レジストパターンを用いて、第1のハードマスク膜をエッチングする第1の凹部形成用マスクパターン形成工程S15〜S18とを有することを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

半導体装置の製造方法

【課題】芯材パターンの側壁に形成するマスク材を利用したパターン形成において工程数を削減できる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、露光により酸を発生する酸発生剤を含む芯材パターン15を下地膜上に形成する工程と、芯材パターン15における長手方向の端部15aを除く部分を選択的に露光する工程と、芯材パターン15から酸の供給を受けて架橋可能なマスク材16を芯材パターン15を覆うように下地膜上に供給する工程と、マスク材16をエッチバックして、芯材パターン15の上面を露出させると共に、マスク材16における芯材パターン15の端部15aに形成された部分を除去し、芯材パターン15の側壁に形成されたマスク材側壁部16aを残す工程と、芯材パターン15を除去し、下地膜上に残されたマスク材側壁部16aをマスクにして下地膜を加工する工程と、を備えた。

(もっと読む)

二重層マスク、三重層マスクのCD制御

【課題】パターンつきフォトレジストマスクと、その下に配された中間マスク層と、その下に配された機能性有機質マスク層と、その下に配されたエッチング層とによって形成されるスタックにおいてエッチング層内のエッチング構成の限界寸法を制御するための方法を提供する。

【解決手段】中間マスク層416は、パターンつきフォトレジストマスク420に対して選択的にエッチングすることによって開口される。機能性有機質マスク層412の開口は、COSを含む開口ガスを流すこと、プラズマを発生させること、および開口ガスを流すことを停止する工程とを含んでいる。その後エッチング層408は、所望の寸法にエッチングされる。

(もっと読む)

マスクパターンの形成方法、微細パターンの形成方法及び成膜装置

【課題】パターン有機膜にシリコン酸化膜を成膜して微細パターンを形成する際に、レジストパターンをスリミング処理する工程を削減することができ、プロセスのコストを低減することができるマスクパターンの形成方法及び微細パターンの形成方法を提供する。

【解決手段】半導体基板上に、薄膜を形成する工程S11と、薄膜上に、レジスト膜を形成する工程S12と、フォトリソグラフィ技術を用いて、レジスト膜を、所定のピッチを有するレジストパターンに加工するパターン加工工程S13と、レジストパターンの形状を加工する形状加工工程S14と、ソースガスと酸素ラジカル又は前記酸素含有ガスとを供給し、形状加工工程により形状を加工されたレジストパターン及び薄膜上に、酸化膜を成膜する成膜工程S15とを具備する。形状加工工程S14と、成膜工程S15とを、酸化膜を成膜する成膜装置内で連続して行う。

(もっと読む)

クロム膜のパターニング方法及びクロム電極

【課題】ウェットエッチング処理工程を含まず、塩素系ガスの専用処理設備を必要としない、安価な装置構成で処理可能な、クロム膜のパターニング方法を提供する。

【解決手段】基材10上にクロム膜11’を形成するクロム膜形成工程と、クロム膜11’の上に、後のパターニング工程における酸素プラズマ条件で除去されないマスク材料膜12’を形成するマスク材料膜形成工程と、マスク材料12’膜をパターニングして所定のマスクパターン12を形成するマスクパターン形成工程と、マスクパターン12が設けられていない部分のクロム膜を、載置されるステージを加熱して酸素プラズマ条件の温度範囲とし且つ塩素原子を含まない酸素プラズマに晒して酸化クロムとして昇華除去するパターニング工程と、を有するように構成して、所定のクロムパターン11を得る。

(もっと読む)

ケイ素含有膜形成用組成物、ケイ素含有膜形成基板及びパターン形成方法

【課題】 リソグラフィーで用いられる多層レジスト法において、フォトレジスト膜の良好なパターン形成が可能であり、良好なドライエッチング耐性を有するエッチングマスク用ケイ素含有膜を形成でき、保存安定性が良好であり、剥離プロセスで使用される溶液で剥離が可能なケイ素含有膜形成用組成物、ケイ素含有膜形成基板、更にパターン形成方法を提供する

【解決手段】 リソグラフィーで用いられる多層レジスト法において成膜されるケイ素含有膜を形成するための熱硬化性ケイ素含有膜形成用組成物であって、少なくとも、(A)酸を触媒として用いて加水分解性ケイ素化合物を加水分解縮合することにより得られるケイ素含有化合物、(B)熱架橋促進剤、(C)炭素数が1〜30の1価又は2価以上の有機酸、(D)3価以上のアルコール、(E)有機溶剤、を含むことを特徴とする熱硬化性ケイ素含有膜形成用組成物。

(もっと読む)

パターン形成方法、半導体装置の製造方法及び半導体装置の製造装置

【課題】2回目の露光工程を必要とせずに、露光限界よりも細い微細なパターンを高精度で形成することができ、従来に比べて工程の簡略化と半導体装置の製造コストの低減を図ることのできるパターン形成方法、半導体装置の製造方法及び製造装置を提供する。

【解決手段】マスクとなるパターンを形成する方法であって、第1パターン105を形成する工程と、第1パターン105の幅をトリミングする工程と、境界層106を第1パターン105の表面に成膜する工程と、境界層106の表面に第2マスク材層107を形成する工程と、境界層106の頂部が露出するように第2マスク材層107の一部を除去する工程と、境界層106をエッチングして第1パターン105を露出させるとともに、第2マスク材層107を上部に有する第2パターンを形成する工程とを具備している。

(もっと読む)

表面処理用マスクの製造方法、表面処理方法、光学デバイス、及び粒子含有フィルムの製造方法

【課題】粒子が重なり合うことなく単層配列で存在し、被処理物が大面積であっても品質にバラツキが生じ難く、且つ高速に凹凸加工を施すことができ、量産性及び低コスト化に優れた表面処理用マスク及びその製造方法、表面処理方法並びに当該表面処理方法により処理された基板を持つ光学デバイスを提供すること。また、粒子が重なり合うことなく単層配列して存在した粒子含有フィルム及びその製造方法を提供すること。

【解決手段】フィルムマスクを被処理物表面に配置した後、エッチング処理を施して、被処理物の表面に凹凸を形成するエッチングする表面処理方法に利用される、表面処理用マスクとしてのフィルムマスクを、基材上に結着剤及びゲル化剤を含む第1塗布層と粒子を含む第2塗布層とをこの順で略同時に塗布形成し、前記第1塗布層をゲル化させた後、前記第1塗布層及び前記第2塗布層を乾燥させて、前記フィルムマスクを形成する。

(もっと読む)

表面処理用マスク及びその製造方法、表面処理方法、光学デバイス、並びに、粒子含有フィルム及びその製造方法

【課題】粒子が重なり合うことなく単層配列で存在し、被処理物が大面積であっても品質にバラツキが生じ難く、且つ高速に凹凸加工を施すことができ、量産性及び低コスト化に優れた表面処理用マスク及びその製造方法、表面処理方法並びに当該表面処理方法により処理された基板を持つ光学デバイスを提供すること。また、粒子が重なり合うことなく単層配列して存在した粒子含有フィルム及びその製造方法を提供すること。

【解決手段】粒子及び粒子よりも体積量が小さい結着剤とを含み且つ粒子が露出した粒子層と結着剤を含み且つ露出した粒子を覆う結着剤層と、を含んで構成されるフィルムマスクを被処理物表面に配置した後、エッチング処理を施して、被処理物の表面に凹凸を形成するエッチングする表面処理方法。また、当該表面処理方法に用いるフィルムマスクを有する表面処理用マスク及び製造方法並びに表面処理方法により得られる基板を持つ光デバイス。

(もっと読む)

表面処理方法、表面処理用マスク、及び光学デバイス

【課題】被処理物が大面積であっても品質にバラツキが生じ難く、且つ高速に凹凸加工を施すことができ、量産性及び低コスト化に優れた表面処理方法、及びそれに用いる表面処理用マスクを提供すること。また、当該表面処理方法により処理された基板を有する光学デバイスを提供すること。

【解決手段】被処理物の表面に凹凸を形成するための表面処理方法であって、第1粒子と第1粒子よりもエッチング耐性が低い第2粒子とを有する粒子群を含んで構成される表面処理用マスクを、被処理物表面に配置する工程と、表面処理用マスクが配置された被処理物の表面に対し、エッチング処理を施し、被処理物の表面に凹凸を形成するエッチング工程と、を有することを特徴とする表面処理方法である。また、当該表面処理方法に用いる表面処理用マスク、及び当該表面処理方法により得られる基板を有する光デバイスである。

(もっと読む)

ドライエッチング方法

【課題】シリコン基板のエッチング加工において、側壁ダメージの防止、マイクロトレンチの防止および垂直形状加工を両立させる。

【解決手段】真空可能なチャンバ10内に配置されたサセプタ(下部電極)12上にシリコン基板Wを載置し、チャンバ10内でエッチングガスを放電させてプラズマを生成し、サセプタ12にイオンを引き込むための第1の高周波RFLを印加する。そして、チャンバ10内の圧力を1mTorr〜100mTorrに選び、圧力(mTorr)をx、サセプタ12に生成される自己バイアス電圧(ボルト)の絶対値をyとすると、y≧−1.7x+295の関係が満たされるようにする。

(もっと読む)

直接パターンによるピンホールフリーのマスク層を利用した太陽電池の製造方法

太陽電池の製造方法が記載される。製造方法では、先ず、誘電体層が上に設けられた基板を準備する。次に、誘電体層の上にピンホールフリーのマスク層を形成する。最後に、マスクを利用せずに、ピンホールフリーのマスク層をパターニングして、パターニングされたピンホールフリーのマスク層を形成する。 (もっと読む)

エッチング方法および加工方法

【課題】パターン露光後の現像工程を省略することができる、新規なフォトリソグラフィー法を提供すること。

【解決手段】被加工表面上に、ヒートモード感光性化合物を蒸着することにより蒸着膜を形成すること、上記蒸着膜に、上記化合物が感光性を有する波長のレーザー光をパターン露光すること、および、上記パターン露光後の蒸着膜を有する被加工表面の少なくとも一部にエッチング処理を施し、上記パターン露光において露光された部分に対応する領域における被加工表面の少なくとも一部をエッチングすること、を含む被加工表面のエッチング方法。被加工物上に複数の凹凸を形成する加工方法。被加工物上に、ヒートモード感光性化合物を蒸着することにより蒸着膜を形成すること、および、上記蒸着膜に、上記化合物が感光性を有する波長のレーザー光をパターン露光することにより、該蒸着膜に複数の凹部を形成すること、を含む。

(もっと読む)

磁性材料の加工方法及び磁気ヘッドの製造方法

【課題】主磁極を従来よりも微細にすることができる磁性材料の加工方法を提供する。

【解決手段】基板1の上方に、磁性材料を有する磁性体層31を形成し、磁性体層31の上に、塩化された状態での沸点が磁性材料の塩化物の沸点に比べて高い金属を含むマスク35を形成し、塩素系ガスとの化学反応を含むドライエッチング法によりマスク35から露出している領域の磁性体層31をエッチングする工程により、磁気ヘッドの磁極を形成する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写プロセスにおいて側壁パターンの曲がりを抑制する。

【解決手段】側壁パターンをマスクとする下地絶縁膜の加工を、フルオロカーボン系のガスを用いたドライエッチングにより行い、その際に、側壁をなすシリコン膜の膜厚をxnmとすると、Vdc<46x−890の関係式を満たす自己バイアス電圧Vdcを基板に印加する。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を増加させることができる半導体素子のパターン形成方法を提供する。

【解決手段】基板300上のデュアルマスク層をパターニングして第1領域Aには第1マスクパターン320Aを形成し、第2領域Bには第1マスクパターン320Aより幅広である第2マスクパターン320Bを形成する。第1マスクパターン320Aの両側壁を覆う第1スペーサ350Aと第2マスクパターン320Bの両側壁を覆う第2スペーサ350Bとを同時に形成する。第1マスクパターン320Aを除去した後、第1領域Aでは、第1スペーサ350Aをエッチングマスクとして利用し、第2領域Bでは第2マスクパターン320B及び第2スペーサ350Bをエッチングマスクとして利用して第1領域A及び第2領域Bで同時に基板300をエッチングする。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】シリコン基材50上にアモルファスカーボン膜51、SiON膜52、反射防止膜53及びフォトレジスト層54が順に積層され、フォトレジスト層54は、反射防止膜53の一部を露出させる開口部55を有するウエハQにおいて、ガス付着係数S

が、S=0.1乃至1.0のデポ性ガスであるCHF3から生成されたプラズマによってフォトレジスト膜54の開口部55の側壁面にデポ66を堆積させて開口部55の開口幅を所定幅に縮小させる開口幅縮小ステップを有する。

(もっと読む)

グラフェンナノデバイスの製造

【課題】 グラフェンナノデバイスの製造を提供する。

【解決手段】 ナノスケールのグラフェン構造製造技術が提供される。マスクとして有用な酸化物ナノワイヤが、グラフェン層上に形成され、次にイオンビームエッチングが実施される。ナノスケールグラフェン構造は、イオンビームエッチング後、残った酸化物ナノワイヤを除去することにより製造される。

(もっと読む)

141 - 160 / 430

[ Back to top ]