Fターム[5F004EA03]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380)

Fターム[5F004EA03]の下位に属するFターム

Fターム[5F004EA03]に分類される特許

121 - 140 / 430

半導体装置の製造方法

【課題】エッチング時に、除去しにくい反応生成物を生じさせうる膜を含む積層構造の被加工膜にも対応できるエッチング技術を提供する。

【解決手段】ハードマスク膜と前記ハードマスク膜上に積層されたフォトレジスト膜とを含むマスク層を被加工膜上に選択的に形成し、フォトレジスト膜を含むマスク層をマスクとして前記被加工膜に対し第1のエッチングを行い、前記マスク層に前記フォトレジスト膜が実質的に存在しない状態で前記ハードマスク膜をマスクとして前記被加工膜に対し第2のエッチングをさらに行うことを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

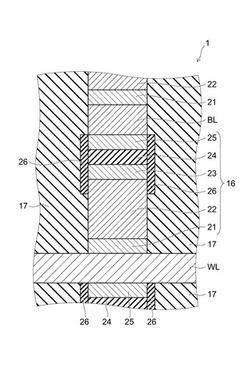

半導体装置及びその製造方法

【課題】可変抵抗素子をエッチングすることなく、残渣を除去できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】ワード線WL上に、バリアメタル膜21、ポリシリコン膜22、下部電極膜23、金属酸化物からなる可変抵抗膜24、上部電極膜25を堆積させる。次に、上部電極膜25、可変抵抗膜24、下部電極膜23をドライエッチングして選択的に除去する。このとき、金属系の残渣が発生する。次に、APMを用いて金属系の残渣を除去する。次に、下部電極膜23、可変抵抗膜24及び上部電極膜25の端面を覆う保護膜26を形成する。次に、ポリシリコン膜22及びバリアメタル膜21をドライエッチングして選択的に除去する。このとき、シリコン系の残渣が発生する。次に、DHFを用いてシリコン系の残渣を除去する。このとき、保護膜26が可変抵抗膜24をDHFから保護する。

(もっと読む)

有機反射防止膜をプラズマエッチングする方法

【課題】有機反射防止膜のドライエッチングに、O2を含むガスを用いて、上層のフォトレジストが横方向にエッチングされ、クリティカルディメンジョンの変化を対策する方法を提供する。

【解決手段】半導体製造プロセスであって、このプロセスは、有機反射防止膜が、下層に対して選択性を与え、及び/又は、フォトレジストによって定められるクリティカルディメンジョンを維持する上層のフォトレジストの横方向のエッチング速度を最小化する。その為に、有機反射防止膜のドライエッチングに、エッチャントガスとしてSO2、キャリアガスとしてHe又はAr等を用いる。このガスには、随意的に、HBr等の他のガスを付加してもよい。このプロセスは、ダマシン構造等の構造を形成するときに0.25μmかそれ以下のコンタクト開口部又はビア開口部をエッチングするのに役立つ。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】高速電子による有機膜の改質効果を十分に発揮することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させる第2条件とを交互に繰り返し、第1の直流電源から、第1条件の期間よりも第2条件の期間のほうが印加電圧の絶対値が大きくなるように負の直流電圧を印加する。

(もっと読む)

トレンチ絶縁部を有する半導体素子およびその製造方法

【課題】トレンチ絶縁で、底接触接続された活性遮蔽部備える半導体素子で、遮蔽効果を改善するとともに、集積密度を改善できる半導体素子を提供する。

【解決手段】トレンチ絶縁(STI,TTI)は、深いトレンチを備えている。この深いトレンチは、被覆絶縁層10,11と、側壁絶縁層6と、導電性充填層7とを有している。この導電性充填層7は、トレンチの底領域において半導体基板の所定のドーピング領域1と導電接続されている。トレンチ接触部(DTC)は、深いトレンチを備えている。この深いトレンチは、側壁絶縁層6と、導電性充填層7とを有している。この導電性充填層7は、接触トレンチの底領域において半導体基板の所定のドーピング領域1と導電接続されている。このトレンチ接触部(DTC)を使用することにより、所要面積を低減するとともに電気的遮蔽特性を改善できる。

(もっと読む)

基板処理方法

【課題】マスクとして用いる層に形成された開口部の幅を縮小する基板処理方法を提供する。

【解決手段】サセプタにウエハWを載置した後、上部フォトレジスト層40に形成された開口部41の幅を縮小する際に、サセプタへプラズマ生成用の高周波電力のみを印加してCF4ガス及びCH4ガスからプラズマを生じさせ、幅が縮小された開口部41を介してハードマスク層39に開口部42を形成しつつ、該開口部42の幅を縮小する際に、サセプタ12へイオン引き込み用及びプラズマ生成用の高周波電力を印加してCF4ガス、CH4ガス及びO2ガスからプラズマを生じさせ、さらに、下部フォトレジスト層38に形成された開口部43の幅を縮小する際に、サセプタ12へプラズマ生成用の高周波電力のみを印加してC4F8ガス及びO2ガスからプラズマを生じさせる。

(もっと読む)

半導体装置の製造方法

【課題】多層マスクエッチングを用いたホール加工において、開口径及び深さの均一なホールを絶縁膜内に形成する。

【解決手段】窒化膜1上に、層間絶縁膜2とレジスト膜3とハードマスク膜4とを順に積層させた多層マスクを形成する工程と、層間絶縁膜2を露出させる開口を多層マスクに形成する工程と、フルオロカーボンを含むガスFRをエッチングガスとしてエッチングを行うことにより、開口内の層間絶縁膜2を除去しつつ、開口の周囲のハードマスク膜4を除去する工程(図3(b))と、開口の周囲にレジスト膜3が露出する前に、ガスFRをガスFRよりもC/F(炭素原子数とフッ素原子数との比率)が高いフルオロカーボンを含むガスFPに切り替えてエッチングを行うことにより、開口から窒化膜1が底面をなすコンタクトホールを形成する工程(図3(c))と、を含む。

(もっと読む)

パターン形成方法

【課題】微細化したホール又はラインのパターンを、従来よりも容易に形成する製造方法を提供する。

【解決手段】被加工膜(2)上に第1のカーボン膜(3)と第1のARL(4)を順次堆積し、第1のARLをパターニングする工程、第2のカーボン膜(6)と第2のARL(7)を順次堆積し、第2のARLをパターニングする工程と、第2のARLをマスクとして第2のカーボン膜を除去する工程と、露出した第1のARLとをマスクとして、第1のカーボン膜を除去する工程と、残存している第1及び第2のカーボン膜をマスクとして被加工膜のエッチングを行う工程とを備えている。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】多層レジストや、メタルゲート/High−k等の積層膜のドライエッチング加工において、高精度の加工精度が要求される。

【解決手段】複数層の連続エッチング加工において、エッチング後の寸法測定することなく、加工の形状または寸法を、真空処理室1の内壁または半導体基板4と、真空処理室1内に生成されたプラズマとの間の電荷量に応じて変動するバイアス電位を計測し、また、プラズマ中の波長の異なる各イオン種の発光強度を測定し、これらから予め設定したモデル式にて、各膜種のエッチング処理毎に、エッチング後の各膜種の加工寸法を予測し、次の膜のエッチング後寸法が、所定の寸法値になるよう処理条件を変更し、連続して次の膜種のエッチング処理を行うことで、寸法や形状を補正するドライエッチング方法および装置を提供する。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク層又は中間層に形成する基板処理方法を提供する。

【解決手段】シリコン基材50上にアモルファスカーボン膜51、Si−ARC膜52、フォトレジスト膜53が順に積層され、フォトレジスト膜53は、Si−ARC膜52の一部を露出させる開口部54を有するウエハWにおいて、CHF3ガスとCF3Iガスとの混合ガスから生成されたプラズマによって、フォトレジスト膜53の開口部54の開口幅を縮小させる開口幅縮小ステップと、開口部54の底部のSi−ARC膜52をエッチングするエッチングステップを1ステップとして行う。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ開口部に傾斜面を形成し、耐圧低下を防止できる半導体装置及びその製造方法を提供することができる。

【解決手段】本発明にかかる製造方法は、半導体基板10にトレンチ21を形成する工程と、絶縁膜23をトレンチ21に堆積させる工程と、プラズマエッチングによりトレンチ21底部の絶縁膜23をエッチングするとともに、トレンチ開口部21aに半導体基板主面10aに対して傾斜角αをなす傾斜面25を同時に形成する工程と、半導体基板10の上面からトレンチ21底部の絶縁膜23に亘って半導体基板10及びトレンチ21を被覆するゲート絶縁膜24を形成する工程と、ゲート絶縁膜24上にゲート電極22を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】導電層と絶縁層とが積層された構造に貫通ホールを一括して形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にシリコン酸化物を含む絶縁層17とシリコンを含む導電層WLとの積層体を形成する工程と、絶縁層17及び導電層WLを貫通するホール50を積層体に形成する工程とを備え、ホール50の形成工程は、積層体上にシリコン酸化物を含む第1のマスク層41を形成する工程と、第1のマスク層41をマスクにして導電層WLをエッチングする工程と、第1のマスク層41上に絶縁層17よりもシリコン含有量が多い第2のマスク層42を形成し第2のマスク層42をマスクにして、絶縁層17をエッチングする工程とを有する。

(もっと読む)

発光素子及びその製造方法

【課題】発光体近傍の透明導電体層表面に凹凸を形成し、その間隔ピッチ、形状を制御することにより、放熱性の向上と、光取出し効率の更なる向上が図れる発光素子及び該発光素子の製造方法の提供。

【解決手段】屈折率が1.7以上である透明導電体層を少なくとも有する発光素子であって、前記透明導電体層表面に、該表面を基準として複数の凹部が配列されたことによって形成された凹凸部を有してなり、隣接する凹部の中心間の最短距離が100nm以上1200nm以下であり、かつ凹部深さが60nm以上350nm以下である発光素子とする。

(もっと読む)

基板処理方法及び記憶媒体

【課題】ホールの上面形状を整えて線条痕をなくすと共に、ボトム形状に歪みがなく、しかもボーイング形状の発生を防止して良好な垂直加工形状のホールを処理対象層に形成することができる基板処理方法を提供する。

【解決手段】処理ガスとしてCF4ガス、CHF3ガス及びC4F8ガスを含有する混合ガスを用い、処理圧力100mTorr(1.33×10Pa)〜150mTorr(2.0×10Pa)で中間層としてのBARC膜53をエッチングし、次いで、処理ガスとしてCOSガス含有ガスを用いて下層レジスト層としてのACL52をエッチングし、その後、処理ガスとしてC6F6ガス含有ガスを用いて処理対象層としての酸化膜51をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】工程数の増加を抑えながら、ビア間の耐圧の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】配線2上に低誘電率膜5及び6を形成した後、低誘電率膜5及び6上にハードマスク7、8及び9を形成する。ハードマスク7〜9上にレジストマスクを形成する。レジストマスクを用いて低誘電率膜5及び6にビアホール11を形成する。レジストマスクをアッシングする。このとき、レジストマスクから生じる飛散物をビアホール11の少なくとも側面に付着させて保護膜12を形成する。その後、ビアホール11を配線2まで到達させ、ビアホール11内に導電材を埋め込む。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】形状性良くかつ高いエッチングレートで被エッチング膜をエッチングして高アスペクト比のホールを形成することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成し、かつ直流電源から負の直流電圧を上部電極に印加する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させ、かつ直流電源から負の直流電圧を上部電極に印加する第2条件とを交互に繰り返し、第1条件によりプラズマ中の正イオンによりエッチングを進行させ、第2条件により負イオンを生成し、直流電圧により負イオンを前記ホール内に供給することによりホール内の正電荷を中和する。

(もっと読む)

ドライエッチング方法

【解決手段】酸素及び/又は窒素を含有し、遷移金属を含有してもよい単層又は多層の第1のケイ素系材料層と、第1のケイ素系材料層に隣接して形成され、遷移金属を含有してもよく、第1のケイ素系材料層より窒素及び酸素の合計の含有率が小さいケイ素系材料層からなる単層又は多層の第2のケイ素系材料層とからなる積層体から、第1のケイ素系材料層のエッチング速度に対する第2のケイ素系材料層のエッチング速度が大きくなるように塩素系ガスと酸素ガスとの比率を設定して、塩素系ドライエッチングにより、第2のケイ素系材料層を選択エッチング除去する。

【効果】エッチングストッパー膜を用いなくとも、同種のケイ素系材料の積層体、例えば、位相シフト膜であるケイ素系材料の遮光膜を、ケイ素系材料の位相シフト膜上に積層したものを用いても、位相シフト膜にダメージを与えることなく、遮光膜に対する高精度なエッチング加工が可能となる。

(もっと読む)

半導体発光装置の製造方法と、それを用いて製造した半導体発光装置

【課題】輝度が改良された半導体発光装置とそれを製造するための方法の提供。

【解決手段】半導体発光素子の光取り出し表面へ自己組織化膜により凹凸構造を形成する際に、電極部分の厚さに起因する凹凸構造が形成できない部分を減少するため、電極形成部分を保護膜により保護し、最後に電極を形成する。このとき、光取り出し表面と電極との間にオーミックコンタクトを生成させるコンタクト層を設ける。

(もっと読む)

微細パターンの形成方法

【課題】LLEにより微細パターンを形成する際に、工程数を削減することができ、第1パターンと第2パターンのCD値の差を小さくすることができる微細パターンの形成方法を提供する。

【解決手段】第1の形状加工工程と、第2の形状加工工程と、エッチング工程とを有し、第1の形状加工工程は、第1のレジスト膜よりなるパターンを形成する第1のパターン形成ステップS13と、そのパターンをトリミング処理する第1トリミングステップS14と、そのパターンの上にエッチングガスの反応生成物よりなる保護膜を堆積し、第1パターンに加工する保護膜堆積ステップS15とを有し、第2の形状加工工程は、第1パターンと交互に配列し、第2のレジスト膜よりなるパターンを形成する第2のパターン形成ステップS17と、そのパターンをトリミング処理し、第2パターンに加工する第2トリミングステップS18とを有する。

(もっと読む)

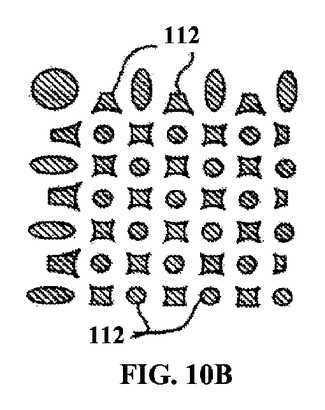

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

121 - 140 / 430

[ Back to top ]